芯片封装体、工作组件和计算设备的制作方法

- 国知局

- 2024-08-02 15:47:13

本技术涉及芯片封装,尤其涉及一种芯片封装体、工作组件和计算设备。

背景技术:

1、一方面,随着半导体制造技术的提高,晶体管密度逼近极限并带来发热、功耗严重生产制造成本的非线性增加等问题。半导体制造技术节点提高变缓并进入“后摩尔时代”,而先进封装成为延续摩尔定律的重要途径。

2、另一方面,随着高性能计算的应用场景不断拓宽,对算力芯片性能提出更高要求。相关技术中,内存墙对传统计算性能的阻碍也是一个大的挑战,近存计算就是为了解决内存墙问题而提出的方案,通过缩小处理器和存储器之间的路径长度并增大路径带宽,从而提升计算性能。而芯片工艺和性能的提升推动了先进封装及芯片模组(chiplet)的需求。

技术实现思路

1、本技术实施例提供一种芯片封装体、工作组件和计算设备,以解决或缓解现有技术中的一项或更多项技术问题。

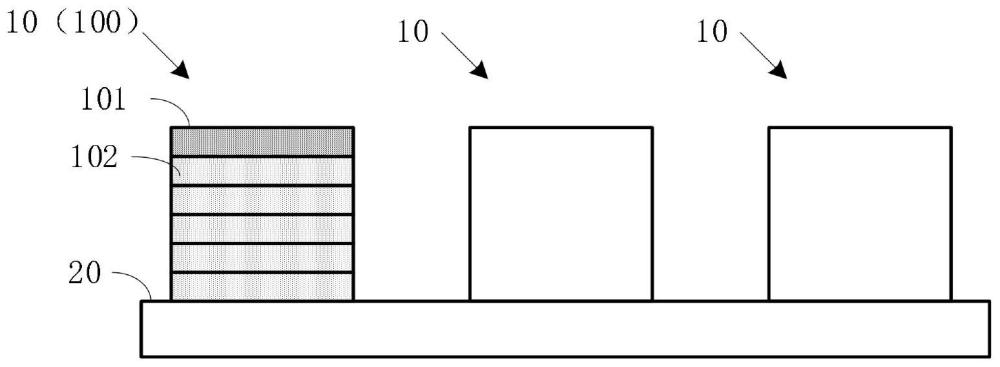

2、作为本技术实施例的一个方面,本技术实施例提供一种芯片封装体,包括:基板;多个裸片模组,布置于所述基板的一侧,所述多个裸片模组中的至少部分相互连接;所述多个裸片模组中包括至少一个存储器裸片模组,所述存储器裸片模组包括堆叠的存储器裸片和逻辑处理裸片。

3、在一种实施方式中,所述逻辑处理裸片包括存储器控制单元和/或处理器单元。

4、在一种实施方式中,所述存储器裸片的数量为多个。

5、在一种实施方式中,逻辑处理裸片的数量为一个或多个。

6、在一种实施方式中,所述存储器裸片模组的顶层裸片为所述存储器裸片,所述存储器裸片模组的底层裸片为所述逻辑处理裸片;或者,所述存储器裸片模组的顶层裸片为所述逻辑处理裸片,所述存储器裸片模组的底层裸片为所述存储器裸片。

7、在一种实施方式中,所述存储器裸片模组的非顶层裸片设置有硅穿孔tsv。

8、在一种实施方式中,所述存储器裸片模组的裸片之间通过混合键合的方式连接,或通过微凸点连接。

9、在一种实施方式中,裸片模组之间的连接方式包括:通过所述基板连接。

10、在一种实施方式中,所述基板中嵌入有基板电路,裸片模组之间的连接方式包括:通过所述基板电路相互连接。

11、在一种实施方式中,所述基板中设置有桥接裸片和重分配rdl中介层,所述rdl中介层布置于所述桥接裸片的朝向所述裸片模组的一侧,裸片模组之间的连接方式包括:通过所述rdl中介层相互连接。

12、在一种实施方式中,所述桥接裸片被配置为硅介质。

13、在一种实施方式中,所述桥接裸片包括硅介质以及所述硅介质中的tsv。

14、在一种实施方式中,裸片模组之间的连接方式包括:通过中介层连接,所述中介层布置于所述基板与所述裸片模组之间。

15、在一种实施方式中,所述中介层包括rdl中介层,所述rdl中介层包括rdl介质以及所述rdl介质中的rdl布线层。

16、在一种实施方式中,所述中介层包括桥接裸片中介层,所述桥接裸片中介层中包括填充介质以及被所述填充介质包围的桥接裸片。

17、在一种实施方式中,所述桥接裸片中介层还包括rdl中介层,所述rdl中介层布置于所述桥接裸片的朝向所述裸片模组的一侧。

18、在一种实施方式中,所述桥接裸片被配置为硅介质;或者,所述桥接裸片包括硅介质以及所述硅介质中的tsv。

19、在一种实施方式中,所述桥接裸片中介层还包括位于所述填充介质中的孔tiv,用于连接所述裸片模组和所述基板。

20、在一种实施方式中,所述中介层包括硅中介层,所述硅中介层包括硅介质以及设置于硅介质中的tsv。

21、在一种实施方式中,所述中介层包括硅中介层和位于所述硅中介层与所述裸片模组之间的rdl中介层,所述硅中介层包括硅介质以及设置于硅介质中的tsv。

22、在一种实施方式中,所述中介层还包括位于所述硅中介层与所述基板之间的rdl中介层。

23、在一种实施方式中,多个存储器裸片模组在所述基板的一侧呈行列分布。

24、在一种实施方式中,多个存储器裸片模组中存在相互连接的相邻存储器裸片模组,其中,所述相邻存储器裸片模组为第一方向上相邻的存储器裸片模组,和/或,所述相邻存储器裸片模组为第二方向上相邻的存储器裸片模组,所述第一方向为行方向或列方向,所述第二方向与所述第一方向在所述基板所在平面呈夹角。

25、在一种实施方式中,所述多个裸片模组中还包括输入输出io裸片,所述io裸片至少与部分的存储器裸片模组相互连接。

26、在一种实施方式中,各所述存储器裸片模组与各所述io裸片呈行列分布的阵列。

27、在一种实施方式中,在第一方向上所述io裸片位于所述阵列的边缘,所述第一方向为行方向或列方向。

28、在一种实施方式中,所述多个存储器裸片模组中存在相互连接的相邻存储器裸片模组,其中,所述相邻存储器裸片模组为第一方向上相邻的存储器裸片模组,和/或,所述相邻存储器裸片模组为第二方向上相邻的存储器裸片模组,所述第一方向为行方向或列方向,所述第二方向与所述第一方向在所述基板所在平面呈夹角。

29、在一种实施方式中,每个所述存储器裸片模组的周围分布有至少一个所述io裸片。

30、在一种实施方式中,每个所述存储器裸片模组的周围分布有四个所述io裸片,在第一方向上相邻的io裸片之间相互连接,所述第一方向为行方向或列方向。

31、在一种实施方式中,所述多个裸片模组中还包括io裸片模组,所述io裸片模组包括堆叠的io裸片和存储器裸片,所述io裸片模组至少与部分的存储器裸片模组相互连接。

32、在一种实施方式中,所述io裸片模组的顶层裸片为所述存储器裸片,所述io裸片模组的底层裸片为所述io裸片;或者,所述io裸片模组的顶层裸片为所述io裸片,所述io裸片模组的底层裸片为所述存储器裸片。

33、在一种实施方式中,各所述存储器裸片模组与各所述io裸片模组在所述基板的一侧呈行列分布的阵列。

34、在一种实施方式中,在第一方向上所述io裸片模组位于所述阵列的边缘,所述第一方向为行方向或列方向。

35、在一种实施方式中,所述多个存储器裸片模组中存在相互连接的相邻存储器裸片模组,其中,所述相邻存储器裸片模组为第一方向上相邻的存储器裸片模组,和/或,所述相邻存储器裸片模组为第二方向上相邻的存储器裸片模组,所述第一方向为行方向或列方向,所述第二方向与所述第一方向在所述基板所在平面呈夹角。

36、在一种实施方式中,每个所述存储器裸片模组的周围分布有至少一个所述io裸片模组。

37、在一种实施方式中,每个所述存储器裸片模组的周围分布有四个所述io裸片模组,在第一方向上相邻的io裸片模组之间相互连接,所述第一方向为行方向或列方向。

38、在一种实施方式中,相邻的io裸片模组模组之间相互连接。

39、作为本技术实施例的一个方面,本技术实施例提供一种工作组件,包括本技术实施例任一种实施方式中的芯片封装体,以及pcb板,所述pcb板的一侧布置有所述芯片封装体。

40、在一种实施方式中,所述芯片封装体的数量为多个。

41、在一种实施方式中,多个所述芯片封装体中的至少部分相互连接。

42、在一种实施方式中,所述pcb板的一侧布置有存储器设备,所述芯片封装体中的裸片模组通过pcb板与所述存储器设备相互连接。

43、在一种实施方式中,所述存储器设备的数量为多个。

44、在一种实施方式中,所述存储器设备与所述芯片封装单元布置于所述pcb板的同一侧。

45、作为本技术实施例的一个方面,本技术实施例提供一种计算设备,包括本技术实施例任一种实施方式中的工作组件以及供电模块。

46、在一种实施方式中,所述工作组件的数量为多个。

47、在一种实施方式中,多个所述工作组件中的至少部分相互连接。

48、本技术实施例的技术方案通过提供一种基于chiplet的2.5d/3d封装解决方案,可以实现超大算力,超高存储带宽。

49、上述概述仅仅是为了说明书的目的,并不意图以任何方式进行限制。除上述描述的示意性的方面、实施方式和特征之外,通过参考附图和以下的详细描述,本技术进一步的方面、实施方式和特征将会是容易明白的。

本文地址:https://www.jishuxx.com/zhuanli/20240801/247826.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表