锁频环路电路及芯片的制作方法

- 国知局

- 2024-08-02 15:53:51

本发明涉及锁频,特别涉及一种锁频环路电路及芯片。

背景技术:

1、锁频环又称为自动频率控制环,是一种典型的自动控制环路,实质上就是动态运用的自动频率微调电路,利用反馈回路对输入频率变化进行调整,最后达到对频率的跟踪,锁频环一般应用在振荡器中,由于振荡器输出的方波信号的频率会被各种例如环境因素温度或磁场等影响,导致方波信号的频率发生漂移,所以振荡器一般需要锁频环对其频率进行自动调整,使其维持在一定的范围内。

2、锁频环通常被应用于需要频率稳定的信号调节和数据传输应用中。例如,电视接收机和网络通信等领域就经常利用锁频环来锁住较稳定的频率,并快速跟踪快速变化的频率。这主要得益于其基于频率控制环路的负反馈控制机制,使得在调节信号频率的过程中,锁频环既能够保持频率的稳定性,又能迅速响应频率的变化。

3、现有的锁频环一般以模拟电路检测和反馈为主,在设计的过程需要精细考量环路的稳定性以防止锁频时钟发生振荡,且由于需要测量和调整连续变化的信号,其需要做的电路分析与仿真工作量极大,导致锁频环的研发周期较长和设计复杂度较大,长时间的设计周期和复杂的设计工作意味着更高的人力投入和研发成本,这些成本最终会转嫁到产品上,导致产品售价上升,不利于市场竞争。

技术实现思路

1、本发明的主要目的是提供一种锁频环路电路及芯片,旨在通过采用数字电路与逻辑电路替换传统的模拟电路设计锁频环,以使锁频环的设计难度更低和研发周期更短。

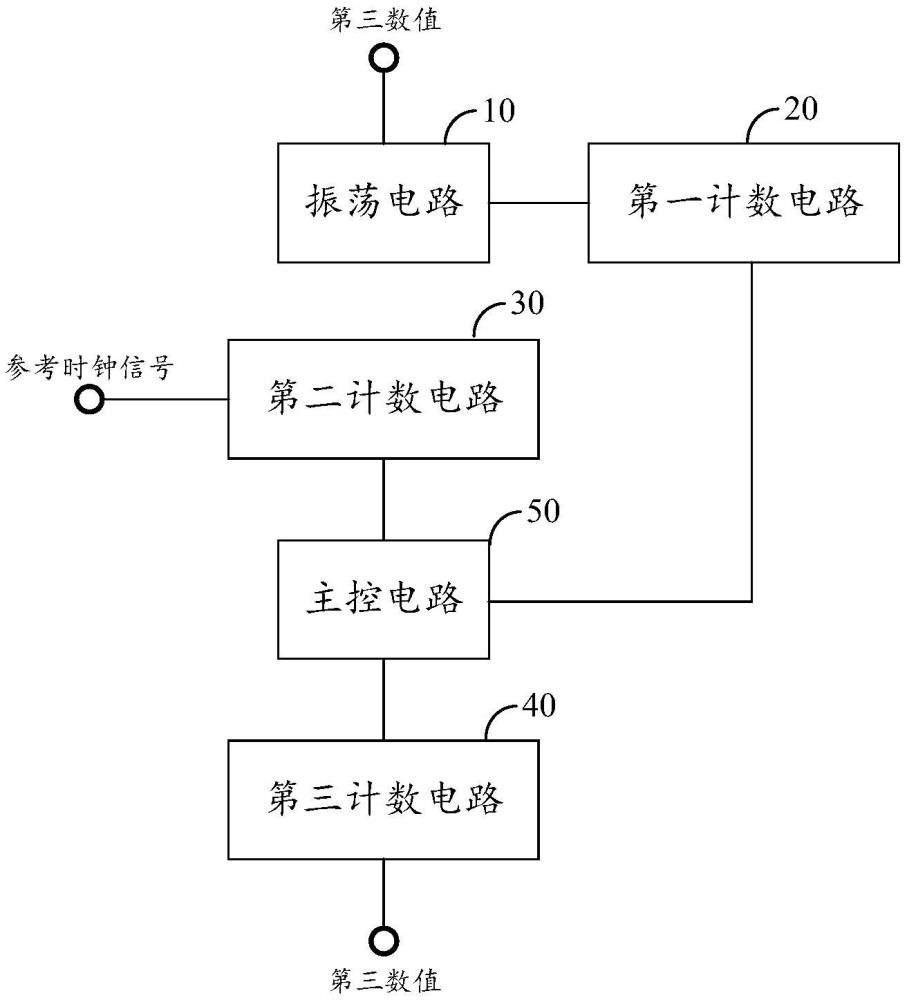

2、为实现上述目的,本发明提出的一种锁频环路电路,包括:

3、振荡电路,所述振荡电路包括至少一个信号接收端,所述振荡电路的输出端用于输出方波信号;

4、第一计数电路、第二计数电路和第三计数电路,所述第一计数电路的输入端与所述振荡电路的输出端电连接,所述第二计数电路的输入端用于接入参考时钟信号,所述第一计数电路用于根据所述方波信号进行计数,所述第二计数电路用于根据所述参考时钟信号进行计数,所述第一计数电路和所述第二计数电路还用于在第一预设时间后分别输出第一数值和第二数值;

5、主控电路,所述主控电路包括第一输入端和第二输入端,所述第一输入端与所述第一计数电路的输出端电连接,所述第二输入端与所述第二计数电路的输出端电连接,所述主控电路的输出端与所述第三计数电路的输入端电连接,所述第三计数电路的输出端与所述信号接收端电连接;

6、所述主控电路用于分析所述第一数值和所述第二数值并输出相应的第一信号至所述第三计数电路,所述第三计数电路用于根据所述第一信号进行计数并在第一预设时间后输出第三数值至所述信号接收端,所述振荡电路根据所述第三数值输出相应的方波信号。

7、可选的,所述振荡电路包括:

8、第一电流、第一电压、n个电容、n个第一开关管、第二开关管、第三开关管、施密特触发器和第一反相器,n个所述电容的第一端均用于接入所述第一电流,n个所述电容的第二端与n个所述第一开关管的输入端一一电连接,n个所述第一开关管的输出端均接地,n个所述第一开关管的受控端与所述第三计数电路的输出端电连接;所述第二开关管的输入端用于接入所述第一电压,所述第二开关管的受控端与n个所述电容的第一端电连接,所述施密特触发器的输入端与所述第二开关管的输入端电连接,所述施密特触发器的输出端与所述第一反相器的输入端电连接,所述第一反相器的输出端与所述第三开关管的受控端电连接,所述第三开关管的输入端与所述第二开关管的输出端电连接,所述第二开关管的输出端接地,所述第三开关管的输出端接地。

9、可选的,第一个所述电容的容值到第n个所述电容的容值依次等比设置,且公比值为2。

10、可选的,所述第一计数电路包括:

11、n个第一分频器和n个第一寄存器,每一所述第一分频器的d端均与其q反端电连接,第一个所述第一分频器的clk端与所述振荡电路的输出端电连接,第m个所述第一分频器的d端与第m+1个所述第一分频器的clk端电连接;n个所述第一分频器的q端分别与n个所述第一寄存器的d端一一电连接,n个所述第一寄存器的q端均与所述主控电路的第一输入端电连接;n个所述第一寄存器的q端在经所述第一预设时间后分别输出所述第一数值至所述主控电路的第一输入端;其中1<m≤n;

12、和/或,所述第二计数电路包括:

13、n个第二分频器和n个第二寄存器,每一所述第二分频器的d端均与其q反端电连接,第一个所述第二分频器的clk端用于接入参考时钟信号,第m个所述第二分频器的d端与第m+1个所述第二分频器的clk端电连接;n个所述第二分频器的q端分别与n个所述第二寄存器的d端一一电连接,n个所述第二寄存器的q端均与所述主控电路的第二输入端电连接;n个所述第二寄存器的q端在经所述第一预设时间后分别输出所述第二数值至所述主控电路的第二输入端;其中1<m≤n。

14、可选的,所述第三计数电路包括:

15、n个第三寄存器、n-1个第一全加器和第一半加器,所述主控电路的输出端分别与n-1个所述第一全加器的第一输入端和所述第一半加器的第一输入端一一电连接,所述第一半加器的第二输入端和n-1个所述第一全加器的第二输入端分别与第一个所述第三寄存器的q端到第n个所述第三寄存器的q端电连接,n-1个所述第一全加器的第一输出端和所述第一半加器的第一输出端分别与第一个所述第三寄存器的d端到第n个所述第三寄存器的d端一一电连接,所述第一半加器的第二输出端与第一个所述第一全加器的第三输入端电连接,第m个所述第一全加器的第二输出端与所述第m+1个所述第一全加器的第三输入端电连接,n个所述第三寄存器的d端均与所述主控电路的输出端电连接,n个所述第三寄存器的q端均与所述振荡电路的信号接收端电连接;其中,1≤m<n-1。

16、可选的,所述主控电路包括:

17、数字比较器和n个数字选择器,所述数字比较器的第一输入端与所述第一计数电路的输出端电连接,所述数字比较器的第二输入端与所述第二计数电路的输出端电连接,所述数字比较器的输出端与n个所述数字选择器的第二输入端电连接,所述数字比较器用于比较所述第一数值和所述第二数值的大小并输出相应的第一信号至n个所述数字选择器的第二输入端,n个所述数字选择器的第一输入端用于接入高电平,第一个所述数字选择器的第三输入端用于接入高电平,第二个所述数字选择器到第n个所述数字选择器的第三输入端均用于接入低电平,所述数字选择器用于根据所述第一信号输出高电平/低电平,n个所述数字选择器的输出端与所述第三计数电路电连接。

18、可选的,所述主控电路包括:

19、n个反相器和n个第二全加器,n个所述反相器的输入端与所述第二计数电路的输出端电连接,n个所述反相器的输出端与n个所述第二全加器的第一输入端电连接,n个所述第二全加器的第二输入端与所述第一计数电路电连接,n个所述第二全加器的输出端与所述第三计数电路的输入端电连接,第m个所述第二全加器的第二输出端与所述第m+1个所述第二全加器的第三输入端电连接;其中,1≤m<n。

20、可选的,所述锁频环路电路还包括:

21、上电复位模块、与门、第二反相器、第三反相器、第四反相器、第五反相器和或门,所述与门的第一输入端与所述振荡电路的输出端电连接,所述与门的第二输入端与所述第二反相器的输出端电连接,所述第二反相器的输入端与所述第二计数电路的输出端电连接,所述第二计数电路的输出端还与所述第三反相器的输入端电连接,所述第三反相器的输出端分别与所述第一计数电路的时钟端和所述第二计数电路的时钟端电连接;所述第四反相器的输入端与所述上电复位模块电连接,所述第四反相器的输出端分别与所述或门的第一输入端、所述第一计数电路的复位端、所述第二计数电路的复位端和所述第三计数电路的复位端电连接,所述第二计数电路的输出端还与所述或门的第二输入端电连接,所述或门的输出端分别与所述第一计数电路的复位端和所述第二计数电路的复位端电连接;所述第二计数电路的输出端还与所述第五反相器的输入端电连接,所述第五反相器与所述第三计数电路的时钟端电连接;当所述第二数值达到预定数值时,所述第二计数电路输出相应的控制信号至所述第二反相器的输入端、所述第三反相器的输入端、所述或门的第二输入端和所述第五反相器的输入端。

22、可选的,所述锁频环路电路还包括:

23、第一延时电路和第二延时电路,所述第一延时电路的输入端与所述第二计数电路的输出端电连接,所述第一延时电路的输出端与所述第三反相器的输入端电连接,所述第一延时电路的输出端还与所述第二延时电路的输入端电连接,所述第二延时电路的输出端与所述第五反相器的输入端电连接。

24、本发明还提出一种芯片,包括上述任一项所述的锁频环路电路。

25、本发明技术方案包括振荡电路、第一计数电路、第二计数电路、第三计数电路和主控电路,振荡电路的输出端用于输出方波信号,第一计数电路用于根据方波信号进行计数,第二计数电路用于根据参考时钟信号进行计数,第一计数电路和第二计数电路还用于在第一预设时间后分别输出第一数值和第二数值,主控电路用于分析第一数值和第二数值并输出相应的第一信号至第三计数电路,第三计数电路用于根据第一信号进行计数并在第一预设时间后输出第三数值至信号接收端,振荡电路根据第三数值输出相应的方波信号。第一数值代表振荡电路在第一预设时间内的频率大小,第二数值代表参考时钟信号在第一预设时间内的频率大小,主控电路将第一数值和第二数值进行分析,例如将第一数值与第二数值的大小进行比较,主控电路根据比较的结果输出相应的第一信号至第三计数电路,若第一数值比第二数值大,第三计数电路则根据第一信号控制振荡电路输出的方波信号的频率降低,若第一数值比第二数值小,第三计数电路则根据第一信号控制振荡电路输出的方波信号的频率提高,以使振荡电路输出的方波信号的频率保持在一定的范围内;再例如,主控电路用于对第一数值与第二数值进行作差并根据差值输出相应的第一信号至第三电路,第三计数电路根据差值的大小控制振荡电路输出的方波信号的频率变高或变低,如此设置,在实际应用中,用户可根据实际需求调整参考时钟信号的频率以控制振荡电路输出的方波信号的频率为所需的频率,由于计数电路可以采用触发器或芯片等现有的数字电路来直接组成,与采用模拟电路的锁频环相比,采用数字电路组成的锁频环的设计过程较为简单,且其分析和仿真工作较为简单,只需使用逻辑分析仪等工具来检查数字信号的状态,以使本发明锁频环路需要花费较短的研发周期、较低的人力成本和研发投入,有利于在市场上进行竞争。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248391.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表