一种高密度存储器及其制备方法、电子设备

- 国知局

- 2024-08-02 15:55:01

本公开涉及半导体,尤其涉及一种高密度存储器及其制备方法、电子设备。

背景技术:

1、近年来,为解决存储墙瓶颈,新型半导体存储器如阻变存储器(rram)、相变存储器(pram)、磁阻存储器(mram)和铁电存储器(feram)等开始受到广泛研究和关注。对于这些新型半导体存储器而言,目前具有工艺可行性的较为成熟的方案是“1t1r”结构,即一个晶体管与一个存储单元相连接,通过晶体管控制存储单元的状态改变。

2、“1t1r”结构通常会面临晶体管的夹断效应(pinch-off)的问题。以阻变存储器为例,夹断效应会造成栅极和漏极之间的偏压被阻断,导致晶体管进入饱和区,进而降低在偏置过程中施加到存储单元上的实际电压,导致存储单元的阻态变化结果偏低。这不仅会增加关态电流,还会降低存储单元的存储窗口。

3、在衬底上施加偏置电压能够在一定程度上改善夹断效应带来的问题。通过从衬底施加编程或擦除偏置来减轻晶体管的限制,以在不影响器件的低电阻状态的情况下实现更好的高电阻状态结果,从而增大存储窗口。然而,采用施加偏置电压的策略又容易导致漏电问题,传统技术中通常设置较大面积的掺杂类型相反的隔离阱以形成反偏的pn结来抑制漏电问题,这又限制了存储阵列密度的进一步提升。

技术实现思路

1、为了在不降低选通晶体管驱动能力的条件下提升诸如阻变存储器(rram)、相变存储器(pram)、磁阻存储器(mram)和铁电存储器(feram)等新型存储器的阵列密度,有必要针对上述背景技术中的问题,提供一种能够在改善漏电问题的同时能够使得存储阵列密度得到进一步提高的高密度存储器。

2、根据本公开的一些实施例,提供了一种存储器,其包括:

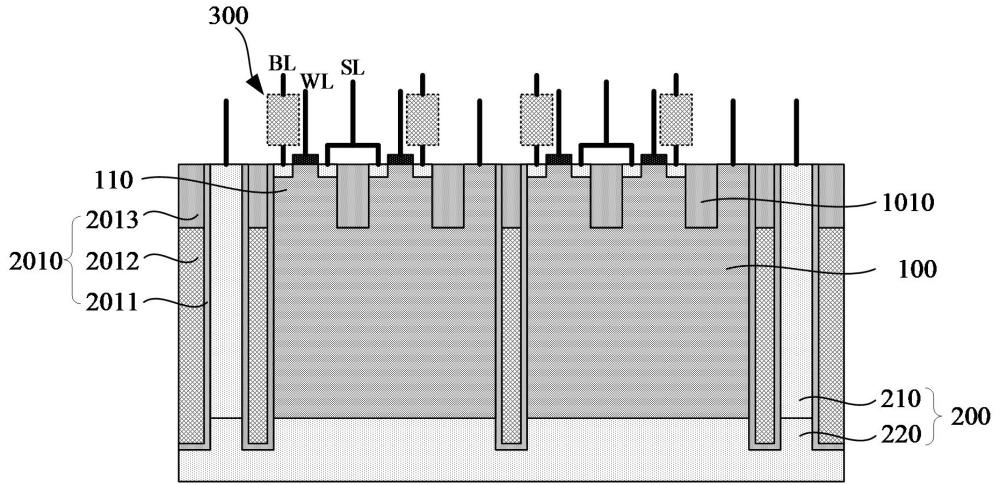

3、半导体衬底,所述半导体衬底包括深阱层和设置于所述深阱层中的多个浅阱层,所述半导体衬底中设置有多个浅沟槽隔离结构和多个深沟槽隔离结构,所述浅沟槽隔离结构设置于所述浅阱层中,所述深沟槽隔离结构的底端位于所述深阱层中,相邻的两个所述浅阱层之间以所述深沟槽隔离结构相间隔,且所述浅沟槽隔离结构和所述深沟槽隔离结构在所述浅阱层中间隔出有源区;

4、存储结构,所述存储结构耦合于所述有源区。

5、在本公开的一些实施例中,所述深阱层包括导电底部和位于所述导电底部之上的深阱电连接部,所述浅阱层设置于所述导电底部上,所述深阱电连接部设置于所述浅阱层的侧边,且所述深阱电连接部和与其相邻的所述浅阱层之间以所述深沟槽隔离结构相间隔。

6、在本公开的一些实施例中,所述深阱电连接部有多个,多个所述深阱电连接部依次间隔设置,相邻的两个所述深阱电连接部之间设置有多个所述浅阱层。

7、在本公开的一些实施例中,所述浅阱层中还设置浅阱电连接部,所述浅阱电连接部与所述有源区之间以所述浅沟槽隔离结构间隔设置。

8、在本公开的一些实施例中,所述深阱层的材料包括n型掺杂的半导体材料,所述浅阱层的材料包括p型掺杂的半导体材料。

9、在本公开的一些实施例中,所述存储结构包括存储介质层,所述存储介质层的材料选自阻变材料、相变材料、铁电材料和磁性材料中的一种或多种。

10、在本公开的一些实施例中,所述浅沟槽隔离结构填充于第一沟槽中,所述第一沟槽的深度为200nm~600nm;和/或,

11、所述深沟槽隔离结构填充于第二沟槽中,所述第二沟槽的深度为1000nm~2000nm。

12、在本公开的一些实施例中,所述深沟槽隔离结构包括设置于第二沟槽中的第一深沟槽介质层、第二深沟槽介质层和第三深沟槽介质层;

13、所述第一深沟槽介质层覆盖于所述第二沟槽的槽壁上,所述第二深沟槽介质层设置于所述第一深沟槽介质层上,且所述第二深沟槽介质层填充于部分所述沟槽中,所述第三深沟槽介质层覆盖于所述第二深沟槽介质层上。

14、在本公开的一些实施例中,所述第二深沟槽介质层的材料选自多晶硅,所述第一深沟槽介质层的材料和所述第三深沟槽介质层的材料选自绝缘材料。

15、进一步地,本公开还提供了一种上述任一实施例的存储器的制备方法,其包括如下步骤:

16、提供设置有所述深阱层和所述浅阱层的半导体衬底;

17、在所述半导体衬底中形成多个第一沟槽,在所述第一沟槽中形成浅沟槽隔离结构;

18、沿着部分所述第一沟槽进行刻蚀,以加深所述第一沟槽并形成第二沟槽,在所述第二沟槽中形成所述深沟槽隔离结构;以及,

19、制备与所述浅阱层中的有源区耦合的所述存储结构。

20、在本公开的一些实施例中,在形成多个第一沟槽的步骤之前,还包括:

21、在所述半导体衬底上形成图案化的刻蚀停止层;

22、在形成多个第一沟槽的步骤中,基于所述刻蚀停止层的开口刻蚀所述半导体衬底;

23、在形成浅沟槽隔离结构的步骤中,所述浅沟槽隔离结构的材料还填充于所述刻蚀停止层的开口中,且所述浅沟槽隔离结构的材料与所述刻蚀停止层的材料不同。

24、在本公开的一些实施例中,在所述第二沟槽中形成所述深沟槽隔离结构的步骤包括:

25、在所述第二沟槽中形成覆盖所述第二沟槽的槽壁的第一深沟槽介质层;

26、在所述第一深沟槽介质层中形成填充于部分所述第二沟槽中的第二深沟槽介质层;

27、在所述第二深沟槽介质层上形成覆盖所述第二深沟槽介质层的第三深沟槽介质层。

28、在本公开的一些实施例中,形成第二深沟槽介质层的步骤包括:在所述第二沟槽中沉积多晶硅材料,以及,对所述多晶硅材料进行回刻,露出部分所述第二沟槽并保留部分所述多晶硅材料。

29、在本公开的一些实施例中,形成浅沟槽隔离结构的步骤包括:采用高密度等离子体化学气相沉积的方式在所述第一沟槽中沉积填充材料,在形成所述浅沟槽隔离结构的步骤之后,还包括:对所述半导体衬底进行退火处理;和/或,

30、形成深沟槽隔离结构的步骤包括:采用高密度等离子体化学气相沉积的方式在所述第二沟槽中沉积填充材料,在形成所述深沟槽隔离结构的步骤之后,还包括:对所述半导体衬底进行退火处理。

31、进一步地,本公开还提供了一种电子设备,所述电子设备包括上述任一实施例所述的存储器。

32、于上述实施例提供的半导体器件结构及制备方法中,半导体衬底中设置有多个浅沟槽隔离结构和多个深沟槽隔离结构,浅沟槽隔离结构和深沟槽隔离结构在浅阱层中间隔出有源区,深沟槽隔离结构的底端位于深阱层中。其中,通过深沟槽隔离结构间隔相邻的两个浅阱层,在对深阱层施加偏置电压时,深沟槽隔离结构能够起到隔离有源区底部漏电流的作用,从而改善漏电问题,保证对该存储器中不同的存储单元施加编程或擦除偏置操作时互不影响。并且,采用深沟槽隔离结构间隔的方式能够降低有源区之间的间距,使得单位面积的深阱层上能够设置更多的晶体管结构,因此该存储器中的存储阵列密度也能够得到较为显著的提高。

33、在一些实施例中,根据结构设计和制备工艺,在40nm工艺节点下,该高密度存储器能比相同驱动能力的传统1t1r阵列至少实现65.6%的面积节省,显著提升了阵列密度。工艺上,本发明提出的自对准工艺只需在标准sti工艺步骤中,增加一张光罩及相应的工艺即实现可自对准dti,工艺简单,更有成本优势。

34、上述说明仅是本公开技术方案的概述,为了能够更清楚了解本公开的技术手段,并可依照说明书的内容予以实施,以下以本公开的较佳实施例并配合附图详细说明如后。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248504.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表