一种垂直沟道三维堆叠器件及其制备方法

- 国知局

- 2024-08-02 15:56:39

本公开涉及半导体,尤其涉及一种垂直沟道三维堆叠器件及其制备方法。

背景技术:

1、动态随机存储器(dram,dynamic random access memory)是业界应用最为广泛的随机存储器,其主流的结构为一个薄膜晶体管(tft,thin film transistor)配合一个电容(capacitance)结合的方式,即1t1c的方式。氧化物半导体以其出色的关态电流在tft中的应用愈发广泛,导致dram中2t0c技术的兴起(即通过两个tft配合实现存储,不需要电容的设置),其主要结构是沟道围绕栅极的方式(caa,channel all around),该结构的优点是便于三维堆叠集成扩大存储密度,但是由于其栅极材料覆盖在源/漏极上方,使栅极与源极或漏极之间均存在较大的寄生电容。

技术实现思路

1、本公开实施例提供了一种垂直沟道三维堆叠器件及其制备方法,主要用于解决垂直沟道的半导体器件寄生电容较大的问题。

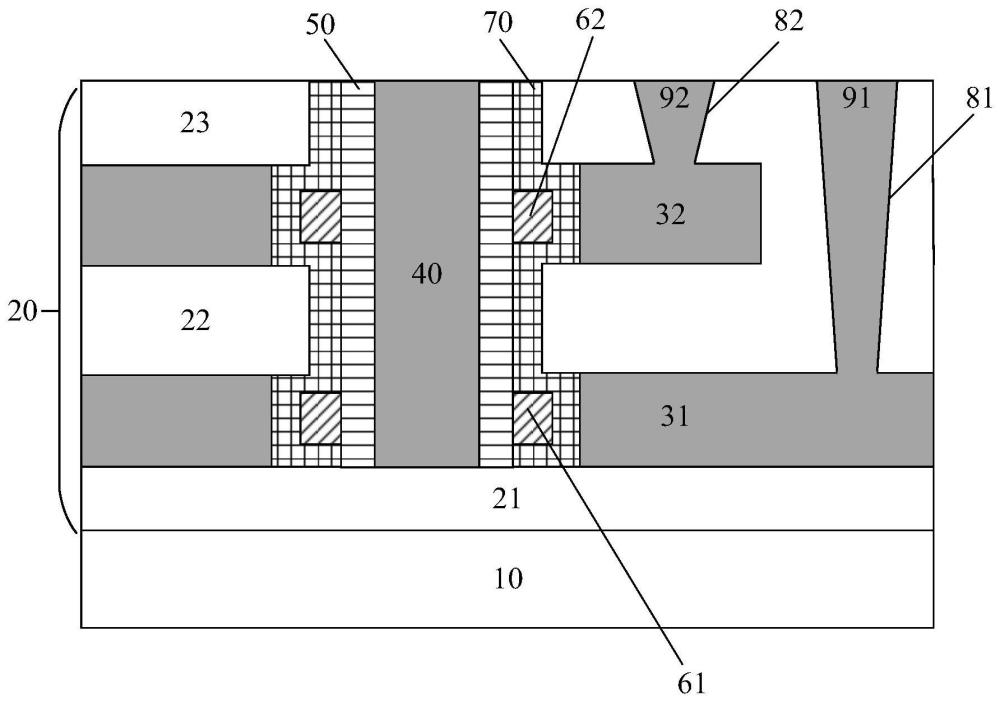

2、为解决上述问题,本公开实施例提供了一种垂直沟道三维堆叠器件,至少包括:衬底;设置在所述衬底一侧表面的膜层单元,所述膜层单元至少包括依次堆叠设置的第一绝缘层、第一电极层、第二绝缘层、第二电极层以及第三绝缘层,所述第一绝缘层位于所述膜层单元中靠近所述衬底的一侧,所述第三绝缘层位于所述膜层单元中远离所述衬底的一侧;同时贯穿所述第一电极层、所述第二绝缘层、所述第二电极层以及所述第三绝缘层的栅极结构;围绕所述栅极结构侧壁设置的栅极介质层;围绕所述栅极介质层侧壁设置的第一间隔层和第二间隔层,其中,所述第一间隔层与所述第一电极层同层设置,所述第二间隔层与所述第二电极层同层设置;围绕所述栅极介质层、所述第一间隔层以及所述第二间隔层设置的沟道层,所述沟道层还设置在所述栅极结构与所述第一绝缘层远离所述衬底一侧的表面之间。

3、在一些实施例中,所述第一间隔层和所述第二间隔层在所述衬底上的正投影的宽度在1纳米至100纳米之间。

4、在一些实施例中,所述第一间隔层和所述第二间隔基于介电常数在1至4法/米之间的材料制备而成。

5、在一些实施例中,所述第一间隔层和所述第二间隔基于以下任意一种材料制备而成:氮化硅sin、含有碳元素的氧化硅sico、氮氧化硅sion。

6、在一些实施例中,所述栅极介质层基于以下任意一种材料制备而成:氧化铝al2o3、二氧化铪hfo2、氧化铝铪hfalo、氧化锆铪hfzro、氮化硅sin、氮氧化硅sion、二氧化硅sio2。

7、在一些实施例中,所述栅极结构、第一电极层和所述第二电极层基于以下任意一种材料制备而成:钨w、钼mo、钽ta、氮化钛tin、氮化钽tan、金au、铂pt。

8、在一些实施例中,所述沟道层基于以下任意一种材料制备而成:氧化铟镓锌igzo、氧化铟锡ito、硅si、锗ge、锗化硅sige、氮化镓gan、砷化镓gaas、磷化铟inp。

9、在一些实施例中,所述第二电极层在所述衬底上的正投影小于所述第一电极层在所述衬底上的正投影;在所述膜层单元上开设有第一通孔和第二通孔;其中,所述第一通孔贯穿所述第一电极层远离所述衬底一侧的所有层级,所述第一通孔在所述衬底上的正投影与所述第一电极层在所述衬底上的正投影重合,并且所述第一通孔在所述衬底上的正投影与所述第二电极层在所述衬底上的正投影之间不重合,所述第一电极层与设置在所述第一通孔内的第一引出结构连接;所述第二通孔贯穿所述第二电极层远离所述衬底一侧的所有层级,所述第二通孔在所述衬底上的正投影与所述第二电极层在所述衬底上的正投影重合,所述第二电极层与所述设置在所述第二通孔内的第二引出结构连接。

10、本公开实施例还提供了一种如上述的垂直沟道三维堆叠器件的制备方法,包括:提供一衬底;在所述衬底一侧表面制备膜层单元,所述膜层单元至少包括依次堆叠设置的第一绝缘层、第一电极层、第二绝缘层、第二电极层以及第三绝缘层,所述第一绝缘层位于所述膜层单元中靠近所述衬底的一侧,所述第三绝缘层位于所述膜层单元中远离所述衬底的一侧;在所述膜层单元上刻蚀栅极孔,所述栅极孔贯穿所述第一电极层、所述第二绝缘层、所述第二电极层以及所述第三绝缘层;在所述栅极孔内横向刻蚀所述第一电极层和所述第二电极层;在所述栅极孔内生长沟道层;在所述栅极孔内形成第一间隔层和第二间隔层;在所述栅极孔内生长栅极介质层和栅极结构。

11、在一些实施例中,,还包括:刻蚀掉所述第二电极层和所述第三绝缘层的部分层级结构,形成引出台阶;在所述引出台阶处生长绝缘材料使第二绝缘层与所述第三绝缘层连接;在所述膜层单元上开设第一通孔和第二通孔,所述第一通孔贯穿所述第一电极层远离所述衬底一侧的所有层级,所述第一通孔在所述衬底上的正投影与所述第一电极层在所述衬底上的正投影重合,并且所述第一通孔在所述衬底上的正投影与所述第二电极层在所述衬底上的正投影之间不重合;所述第二通孔贯穿所述第二电极层远离所述衬底一侧的鄋层级,所述第二通孔在所述衬底上的正投影与所述第二电极层在所述衬底上的正投影重合;在所述第一通孔内制备第一引出结构使所述第一电极层与所述第一引出结构连接,在所述第二通孔内制备第二引出结构使所述第二电极层与所述第二引出结构连接。

12、本公开实施例的有益效果在于:利用垂直沟道内设置的第一间隔层和第二间隔层来增加栅极结构和第一电极层、第二电极层之间的间距,进而达到降低寄生电容的目的。

技术特征:1.一种垂直沟道三维堆叠器件,其特征在于,至少包括:

2.根据权利要求1所述的垂直沟道三维堆叠器件,其特征在于,所述第一间隔层和所述第二间隔层在所述衬底上的正投影的宽度在1纳米至100纳米之间。

3.根据权利要求1所述的垂直沟道三维堆叠器件,其特征在于,所述第一间隔层和所述第二间隔基于介电常数在1至4法/米之间的材料制备而成。

4.根据权利要求3所述的垂直沟道三维堆叠器件,其特征在于,所述第一间隔层和所述第二间隔基于以下任意一种材料制备而成:

5.根据权利要求1所述的垂直沟道三维堆叠器件,其特征在于,所述栅极介质层基于以下任意一种材料制备而成:

6.根据权利要求1所述的垂直沟道三维堆叠器件,其特征在于,所述栅极结构、第一电极层和所述第二电极层基于以下任意一种材料制备而成:

7.根据权利要求1所述的垂直沟道三维堆叠器件,其特征在于,所述沟道层基于以下任意一种材料制备而成:

8.根据权利要求1至7中任一项所述的垂直沟道三维堆叠器件,其特征在于,所述第二电极层在所述衬底上的正投影小于所述第一电极层在所述衬底上的正投影;

9.一种如权利要求1至8中任一项所述的垂直沟道三维堆叠器件的制备方法,其特征在于,包括:

10.根据权利要求9所述的制备方法,其特征在于,还包括:

技术总结本公开提供了一种垂直沟道三维堆叠器件及其制备方法,该器件包括:衬底;膜层单元,膜层单元包括依次堆叠设置的第一绝缘层、第一电极层、第二绝缘层、第二电极层以及第三绝缘层;栅极结构;围绕栅极结构侧壁设置的栅极介质层;围绕栅极介质层侧壁设置的第一间隔层和第二间隔层,第一间隔层与第一电极层同层设置,第二间隔层与第二电极层同层设置;围绕栅极介质层、第一间隔层以及第二间隔层设置的沟道层,沟道层还设置在栅极结构与第一绝缘层远离衬底一侧的表面之间。本公开利用垂直沟道内设置的第一间隔层和第二间隔层来增加栅极结构和第一电极层、第二电极层之间的间距,进而达到降低寄生电容的目的。技术研发人员:李俊杰,高建峰,周娜,张琛琛,杨涛,李俊峰,罗军,陈睿受保护的技术使用者:中国科学院微电子研究所技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240801/248580.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表