一种芯粒延迟故障测试电路及方法

- 国知局

- 2024-08-05 11:44:01

本发明涉及超大规模集成电路可测性设计,具体是公开一种芯粒延迟故障测试电路及方法,属于测量、测试的。

背景技术:

1、芯粒(chiplet)技术通过内部互连技术将多个小芯片集成到一个封装中,形成专用功能芯片,从而解决芯片规模不能无限扩大、开发成本高、制造周期长等问题。chiplet采用2.5d、3d等先进封装技术,实现了高性能片上互连,提高了芯片系统的集成度,扩大了其性能和功耗的优化空间,克服了目前ic开发的物理和材料限制。

2、3d chiplet使用基于硅通孔(through silicon vias,tsv)的互连结构取代了过长的全局布线,减少了传输延迟,降低了功耗,提高了系统性能,但与任何半导体工艺一样,在制造、芯片键合和组装过程中,空洞缺陷、漏电缺陷、tsv微衬底未对齐缺陷的引入会引发延时故障,因此有必要检测tsv中的延迟故障,但是由于这些延迟量足够小,无法在常规逻辑测试中检测到。此外,tsv测试包括绑定前和绑定后阶段,由于绑定后阶段对于tsv的访问资源有限,测试更加困难。

3、3d chiplet的互连依赖tsv而不是过长的全局布线,具有传输延迟更低、集成度更高、体积更小、系统性能更好的优点。然而,在tsv的制造和粘接过程中,如微空洞、针孔、微错位等许多缺陷都会导致延迟故障。因此,迫切需要一种检测tsv延迟故障的技术。然而,传统的逻辑测试方法无法检测到这些延迟故障,因为这些故障在低速测试时钟下无法显露出来。此外,绑定前和绑定后阶段均应进行tsv测试,绑定后测试阶段的测试难度更大。因为与2d ic相比,3d chiplet连接到tsv的外部i/o端口数量非常少,并且能够用于测试的端口更少,而且延迟故障在很小的范围内可测,如果测试方法的精度较差,很可能无法检测到延迟故障。因此,迫切需要高精度的绑定后阶段tsv延迟测试方法。

技术实现思路

1、本发明的发明目的是针对上述背景技术的不足,提供一种芯粒延迟故障测试电路及方法,通过双延迟链结构将来自tsv的传输延迟转换为数字信号后输出观测,定量地计算出具体的延迟时间,实现在较高精度内对堆叠后芯粒中tsv延迟故障的进行测试的发明目的,解决现有延迟故障测试方法不能精确测量芯粒绑定后阶段tsv延迟故障的技术问题。

2、本发明为实现上述发明目的采用如下技术方案:

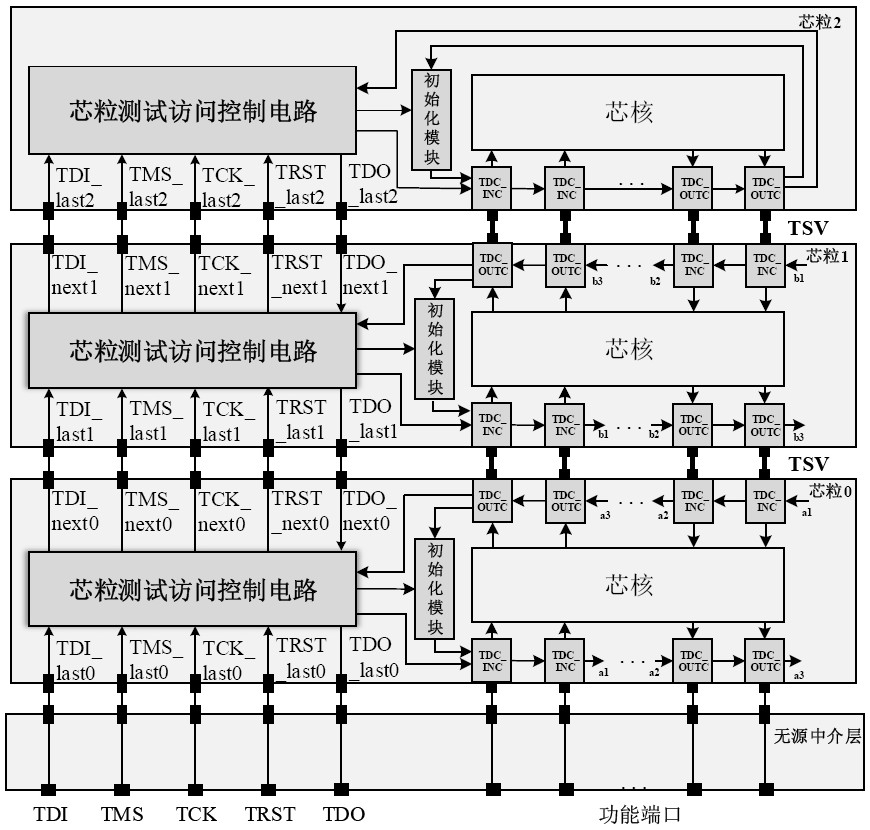

3、一种芯粒延迟故障测试电路,用于对包含至少两层芯粒的chiplet系统进行延时故障测试,每层芯粒插入一个测试电路;其中,

4、每层芯粒插入的测试电路均包括:

5、至少一个与芯粒功能输出引脚相连的时间数字转换输入单元,各时间数字转换输入单元串联连接组成时间数字转换输入扫描链,时间数字转换输入扫描链首端的时间数字转换输入单元的串行输入端口连接芯粒测试访问控制电路,

6、至少一个与芯粒功能输入引脚相连的时间数字转换输出单元,各时间数字转换输出单元串联连接组成时间数字转换输出扫描链,时间数字转换输出扫描链的首端与时间数字转换输入扫描链的末端连接构成时间数字转换扫描链,时间数字转换输出扫描链末端的时间数字转换输出单元的串行输出端口连接芯粒测试访问控制电路,时间数字转换扫描链包含两条延迟链,

7、初始化模块,分别与两条延迟链首尾相连,构成一条用于测试激励在待测硅通孔开始传播时传播高电平的环路延迟链a,以及一条用于测试激励在待测硅通孔结束传播时传播高电平的环路延迟链b,及,

8、芯粒测试访问控制电路,通过硅通孔连接下一层芯粒的测试数据输入端口、测试模式选择信号输入端口、时钟信号输入端口、复位控制信号输入端口、测试响应信号输出端口;在各控制周期的测试控制信号下处理下一层芯粒的测试数据,获取测试路径配置信号、测试指令以及本层芯粒各控制周期的测试响应数据;根据测试指令控制本层芯粒接入的时间数字转换扫描链传播来自下一层芯粒的测试数据;根据测试路径配置信号传输下一层芯粒的测试模式选择信号至上一层芯粒测试电路中的芯粒测试访问电路并回传上一层芯粒的测试响应数据至下一层芯粒测试电路中的芯粒访问电路,传输下一层芯粒的测试数据至上一层芯粒测试电路中的芯粒测试访问电路并选择本层芯粒一个控制周期的测试响应数据输出。

9、作为一种芯粒延迟故障测试电路的进一步优化方案,芯粒测试访问控制电路包括:测试状态转换电路、测试路径配置电路、测试指令电路、测试数据电路以及副测试接口电路;其中,

10、测试状态转换电路,接收下一层芯粒的测试模式选择信号、时钟信号和复位控制信号,用于产生测试路径配置电路控制周期、测试指令电路控制周期、测试数据电路控制周期的测试控制信号;

11、测试路径配置电路,接收到测试路径配置电路控制周期的测试控制信号后,对下一层芯粒的测试数据进行处理,输出是否将上一层芯粒添加进测试路径的控制信号、测试路径是否需要跳过本层芯粒的控制信号以及本层芯粒测试路径配置电路控制周期的测试响应数据;

12、测试指令电路,接收到测试指令电路控制周期的测试控制信号后,对下一层芯粒的测试数据进行处理,输出本层芯粒测试指令电路控制周期的测试响应数据,根据选中的延迟测试指令解码得到测试指令,所述延迟测试指令包括:发送0-1跳变信号指令、发送1-0跳变信号指令、传播1信号指令和传播0信号指令;

13、测试数据电路,接收到测试数据电路控制周期的测试控制信号后,在发送0-1跳变信号指令对应的sending01测试指令下选择sending01寄存器,传输sending01测试指令至待测tsv连接的时间数字转换输出单元,将下一层芯粒的测试数据作为本层芯粒测试数据电路控制周期的测试响应数据直接输出;在发送1-0跳变信号指令对应的sending10测试指令下选择sendign10寄存器,传输sending10测试指令至待测tsv连接的时间数字转换输出单元,将下一层芯粒的测试数据作为本层芯粒测试数据电路控制周期的测试响应数据直接输出;在传播1信号指令对应的propagation1测试指令或传播0信号指令对应的propagation0测试指令下选择本层芯粒接入的时间数字转换扫描链,propagation1测试指令或propagation0测试指令传输至待测硅通孔连接的时间数字转换输入单元,下一层芯粒的测试数据经本层芯粒接入的时间数字转换扫描链传播后,输出本层芯粒测试数据电路控制周期的测试响应数据;

14、副测试接口电路,传输下一层芯粒、复位控制信号和时钟信号至上一层芯粒的复位控制信号输入端口和时钟信号输入端口;是否将上一层芯粒添加进测试路的径控制信号有效时,下一层芯粒的测试模式选择信号传入上一层芯粒的测试模式选择信号输入端口,上一层芯粒的测试响应数据传回本层芯粒测试电路的芯粒测试访问控制电路并经下一层芯粒的测试响应信号输出端口传输至下一层芯粒测试电路的芯粒测试访问控制电路;是否需要跳过当层芯粒的控制信号有效时,下一层芯粒的测试数据跳过本层芯粒测试电路并经上一层芯粒的测试数据输入端口直接传入上一层芯粒测试电路;是否需要跳过当层芯粒的控制信号无效时,在本层芯粒测试路径配置电路控制周期的测试响应数据、本层芯粒测试指令电路控制周期的测试响应数据、本层芯粒测试数据电路控制周期的测试响应数据中选择一个传入下一层芯粒的测试响应信号输出端口。

15、作为一种芯粒延迟故障测试电路的再进一步优化方案,时间数字转换输入单元均包括:延迟模块a、延迟模块b以及扫描测试模块;

16、时间数字转换扫描链首端时间数字转换输入单元以外的其它时间数字输入单元中:

17、延迟模块a,通过硅通孔与芯粒功能引脚输出端相连,用于测试激励经待测硅通孔传播到达时传播高电平,其a延时信号输入端连接上一级时间数字输入转换单元的a延时信号输出端,其a延时信号输出端连接下一级时间数字输入转换单元的a延时信号输入端或下一级时间数字输出转换单元的a延时信号输入端,

18、延迟模块b,用于在测试激励经待测硅通孔开始发送时传播高电平,其b延时信号输入端连接上一级时间数字输入转换单元的b延时信号输出端,其b延时信号输出端连接下一级时间数字转换输入单元的b延时信号输入端或下一级时间数字转换输出单元的b延时信号输入端,

19、扫描测试模块,用于捕获环路延迟链b的传播结果、更新测试响应,传输来自待测硅通孔的测试激励或更新的测试响应至芯核;

20、时间数字转换扫描链首端的时间数字转换输入单元中,延迟模块a的a延时信号输入端连接初始化模块,延迟模块b的b延时信号输入端连接初始化模块。

21、作为一种芯粒延迟故障测试电路的再进一步优化方案,时间数字转换输出单元均包括:延迟模块a、延迟模块b、扫描测试模块及输出模块;

22、时间数字转换扫描链末端时间数字转换输出单元以外的其它时间数字转换输出单元中:

23、延迟模块a,用于测试激励经待测硅通孔传播到达时传播高电平,其a延时信号输入端连接上一级时间数字输入转换单元的a延时信号输出端或上一级时间数字输出转换单元的a延时信号输出端,其a延时信号输出端连接下一级时间数字输出转换单元的a延时信号输入端,

24、延迟模块b,用于测试激励经待测硅通孔开始发送时传播高电平,其b延时信号输入端连接上一级时间数字输入转换单元的b延时信号输出端或上一级时间数字输出转换单元的b延时信号输出端,其b延时信号输出端连接下一级时间数字输出转换单元的b延时信号输入端,

25、扫描测试模块,用于捕获环路延迟链b的传播结果、更新测试响应,输出来自芯核的数据或更新的测试响应,

26、输出模块,用于接收来自芯核的数据或更新的测试响应,其输出端通过待测硅通孔与芯粒功能输入引脚相连,根据数据电路捕获信号生成测试激励;

27、时间数字转换扫描链末端的时间数字转换输出单元中,延迟模块a的a延时信号输出端连接初始化模块,延迟模块b的b延时信号输出端连接初始化模块。

28、作为一种芯粒延迟故障测试电路的更进一步优化方案,延迟模块a包括:第一异或门、第一与门、第二异或门以及第一多路复用器;其中,

29、第一异或门的第一输入端通过硅通孔连接芯粒功能引脚输出端口,第一异或门的第二输入端接入传播模式测试指令;

30、第一与门的第一输入端连接第一异或门的输出端,第一与门的第二输入端接入本级时间数字转换输入单元测试响应的更新信号;

31、第二异或门的第一输入端作为本级时间数字转换输入单元的a延时信号端,第二异或门的第二输入端连接第一与门的输出端,第二异或门的输出端作为本级时间数字转换输入单元的a延时信号输出端;

32、第一多路复用器的0端接入数据电路时钟信号,第一多路复用器的1端连接所述第二异或门的输出端,第一多路复用器的控制端接入延迟测试控制信号。

33、作为一种芯粒延迟故障测试电路的更进一步优化方案,延迟模块b包括:第二与门、第三异或门以及第二多路复用器;其中,

34、第二与门的第一输入端接入数据电路捕获信号,第二与门的第二输入端接入本级时间数字转换输入单元测试响应的更新信号;

35、第三异或门的第一输入端作为本级时间数字转换输入单元的b延时输入信号输入端,第三异或门的第二输入端连接所述第二与门的输出端,第三异或门的输出端作为本级时间数字转换输入单元的b延时信号输出端;

36、第二多路复用器的0端接入上一级时间数字转换输入单元传输来的测试响应或待测硅通孔接收的测试激励,第二多路复用器的1端连接所述第三异或门的输出端,第二多路复用器的选择输入端接入延迟测试控制信号。

37、作为一种芯粒延迟故障测试电路的更进一步优化方案,扫描测试模块包括:第三多路复用器、第一d触发器、第二d触发器以及第四多路复用器;其中,

38、第三多路复用器的0端通过待测硅通孔连接芯粒功能引脚输入端口,第三多路复用器的1端接入上一级时间数字转换输入单元传输来的测试响应,第三多路复用器的选择输入端接入输出选择信号;

39、第一d触发器的d输入端连接所述第二多路复用器的输出端,第一d触发器的时钟输入端连接第一多路复用器的输出端,第一d触发器的输出端作为本级时间数字转换输入单元测试响应的输出端口;

40、第二d触发器的d输入端连接所述第一d触发器的输出端,第二d触发器的时钟输入端接入数据电路时钟信号的更新信号,第二d触发器的输出端输出本级时间数字转换输入单元测试响应的更新信号;

41、第四多路复用器的0端通过待测硅通孔连接芯粒功能引脚输入端口,第四多路复用器的1端连接所述第二d触发器的输出端,第四多路复用器的选择输入端连接输入内核选择信号,第四多路复用器的输出端连接芯粒内的芯核。

42、作为一种芯粒延迟故障测试电路的更进一步优化方案,输出模块包括:非门和第五多路复用器;其中,

43、非门的输入端接入数据电路捕获信号;

44、第五多路复用器的00输入端连接所述扫描测试模块输出端,其01输入端接入数据电路捕获信号,第五多路复用器的10输入端连接所述非门的输出端,第五多路复用器的11输入端接低电平,第五多路复用器的选择0输入端接入sending01测试指令,第五多路复用器的选择1输入端接入sending10测试指令,其输出端连接待测硅通孔。

45、一种芯粒延迟故障测试方法,基于上述电路实现,该方法包括如下步骤:

46、步骤1,选择待测硅通孔和延迟故障检测类型:选择连接第n层芯粒和第n+1层芯粒的第m个硅通孔作为待测tsv进行跳变延迟故障检测,n、m均为大于或等于0的整数;

47、步骤2,将第n层芯粒的下层芯粒全部添加至测试路径:遍历底层芯粒至第n-1层芯粒中每层芯粒测试电路中的副测试接口电路,使能当前配置芯粒测试电路的测试路径配置电路控制周期有效,配置是否将上一层芯粒添加进测试路径的控制信号、测试路径是否需要跳过当层芯粒的控制信号均有效,打开当前配置芯粒测试电路中的副测试接口电路,允许下一层芯粒的测试数据跳过当前配置芯粒而传输到上一层芯粒;

48、步骤3,配置第n层芯粒测试电路中的副测试接口电路:使能第n层芯粒测试电路的测试路径配置电路控制周期有效,配置是否将上一层芯粒添加进测试路径的控制信号有效且测试路径是否需要跳过当层芯粒的控制信号无效,开启从第n层芯粒到第n+1层芯粒的测试数据传输通道而无需跳过第n层芯粒;

49、步骤4,配置测试指令:使能第n层和第n+1层芯粒测试电路中的测试指令电路控制周期有效,为第n层芯粒的测试电路配置sending01测试指令或sending10测试指令,为第n+1层芯粒配置propagation1测试指令或propagation0测试指令;

50、步骤5,移入测试数据:使能第n层和第n+1层芯粒测试电路中的测试数据电路控制周期有效,通过底层芯粒的外部端口传输测试数据,向与待测硅通孔连接的时间数字转换输入单元移入测试数据1,向时间数字转换扫描链上的其它时间数字转换单元移入测试数据0;

51、步骤6,更新测试数据:在测试数据电路控制周期的更新状态下,第二d触发器更新测试响应数据,并将第层n+1芯粒测试电路中的两条环路延迟链初始化为0;

52、步骤7、捕获测试响应:在测试数据电路控制周期捕获状态下,在数据电路捕获信号上升沿,第n+1层芯粒的延迟链b开始传播高电平,同时第n层芯粒的时间数字转换输出单元输出测试激励,当测试激励到达第n+1层芯粒时,环路延迟链a开始传播高电平,使能第一d触发器时钟信号有效,并且捕获环路延迟链b的值;

53、步骤8、移出测试响应:在测试数据电路控制周期的移位状态下,移出前一组测试响应,移入下一组测试数据,返回步骤1。

54、作为一种芯粒延迟故障测试方法的进一步优化方案,步骤1进行跳变延迟故障检测为0-1跳变延迟故障检测或1-0跳变延迟故障检测。

55、本发明采用上述技术方案,具有以下有益效果:

56、(1)本发明所提芯粒延时故障测试电路,通过时间数字转换模块构建每层芯粒的tdc扫描链,采用双环路双延迟链的结构将跳变信号在tsv上的传输延迟在极高的精度内转变为数字信号,定量计算出tsv传输延迟时间,从而判断是否存在延迟故障,能够在较高精度内对堆叠后芯粒中tsv延迟故障的进行测试。

57、(2)本发明所提芯粒延时故障测试电路,通过芯粒测试访问控制电路配置测试路径并生成测试指令,对基于时间数字转换模块的芯粒测试电路进行控制,实现下一层芯粒的测试数据的上传、上一层芯粒的测试响应数据的回传以及本层芯粒测试响应数据的选择输出,显著减少有效测试路径的配置时间,提高配置效率,能够在不增加外部测试端口的情况下实现对芯粒系统的测试访问和控制。

58、(3)本发明所提芯粒延时故障测试方法,通过芯粒测试访问电路中设计的的14位测试状态转换状态机,有效减少了测试配置步骤,提升了测试效率。

本文地址:https://www.jishuxx.com/zhuanli/20240802/259089.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表