基于三端口非易失性器件的不等式条件判断求解器及其操作方法

- 国知局

- 2024-08-22 14:22:30

本发明涉及存储和不等式条件判断领域,尤其涉及一种基于三端口非易失性器件的不等式条件判断求解器的工作原理和操作方法。

背景技术:

1、组合优化问题广泛应用于物流、资源分配、通信网络设计、金融、药物发现和交通系统等各个领域。这些问题通常属于非确定性多项式时间难题(np-hard),代表了np领域中一些最具挑战性的计算任务。

2、使用基于冯·诺伊曼体系结构的数字计算机来解决组合优化问题存在困难,因为随着问题规模的增加,所需的资源在计算能力和延迟方面呈指数增长。因此,迫切需要探索新的硬件设计,采用替代架构和算法,以有效地解决组合优化问题。

3、目前,有多种基于ising模型和qubo模型的求解器来求解这些组合优化问题,然而,这些求解器的实现大多局限于处理简单无约束的组合优化问题,而对于具有一般性的不等式约束的组合优化问题研究较少,缺少对于不等式部分条件判断的处理器。

4、基于上述问题,为了减少求解器的资源成本,提高可拓展性和增加可求解的组合优化问题范围,申请人提出了一种基于三端口非易失性器件的不等式条件判断求解器的工作原理和操作方法。

技术实现思路

1、本发明的目的在于针对目前基于ising模型和qubo模型的求解器无法直接处理不等式约束、仅限于求解部分类型的组合优化问题的问题,提供一种基于三端口非易失性器件的不等式条件判断求解器及其操作方法。

2、本发明的目的是通过以下技术方案实现的:

3、一种基于三端口非易失性器件的不等式条件判断求解器,包括两个阵列和电压比较器,所述两个阵列的输出信号线连接至电压比较器的两个输入端,两个阵列分别为阵列1和阵列2,所述阵列包括m×n个不等式单元、pmos和电容cml,每个不等式单元包括一个三端口非易失性器件,所述三端口非易失性器件的栅极与输入信号g相连,漏极与ml相连,源极与地相连,同一阵列的三端口非易失性器件共用一根信号线ml,同一列三端口非易失性器件共用一根输入线g,所述pmos的栅极与输入信号vpre相连,漏极与ml相连,源极与电源相连,所述电容cml与ml和地相连。

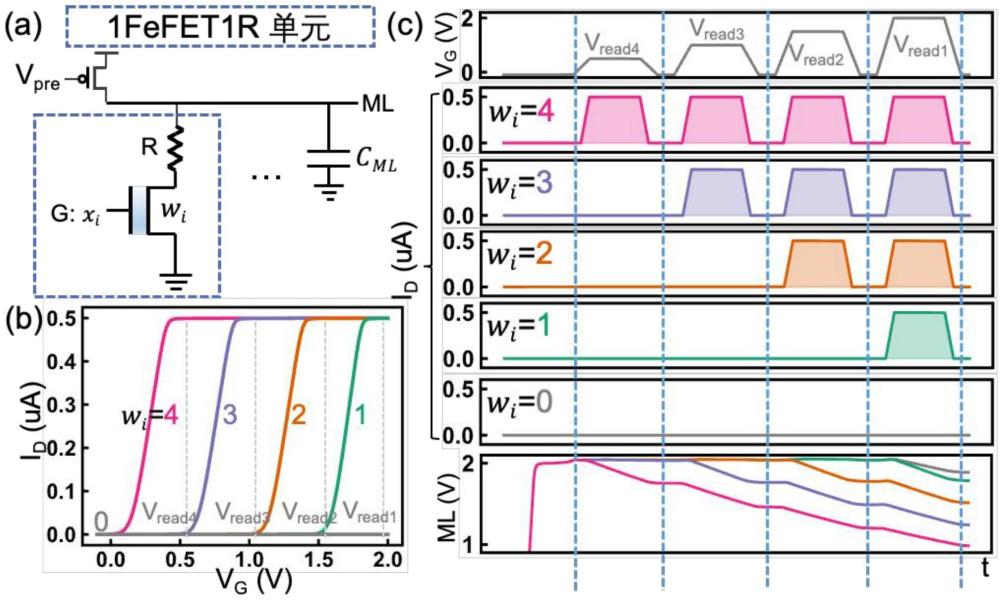

4、进一步地,所述三端口非易失性器件为fefet或1fefet-1r或由1reram-1t构成的不等式单元。

5、进一步地,所述电压比较器为一个二级比较器。

6、本发明还提供一种如上所述不等式条件判断求解器的操作方法,包括:

7、准备阶段:在所述阵列开始工作前,将不等式的参数存储到两个阵列中,假设需要判断的不等式为其中输入变量的每个元素xi只能取0或者1,;同时,预设一个输入变量满足

8、工作阶段:

9、a)通过pmos对ml上的电容cml进行预充电,即将阵列1和阵列2的ml都充电至电源电压vdd;

10、b)根据不等式的输入变量对阵列1进行输入:如果xi=0,则给第i列的信号线g施加0v电压,如果xi=1,则施加一个阶梯状电压,每一级阶梯的电压值为三端口非易失性器件所可能存储的相应电压阈值;当所施加电压超过三端口非易失性器件的电压阈值时,三端口非易失性器件导通,使得ml对地放电,反之,三端口非易失性器件关断,ml上的电压维持不变;同时,根据准备阶段中预设好的对阵列2进行输入:如果x'i=0,则给第i列的信号线g施加0v电压,如果x'i=1,则施加一个阶梯状电压,每一级阶梯的电压值为三端口非易失性器件所可能存储的相应电压阈值;当所施加电压超过三端口非易失性器件的电压阈值时,三端口非易失性器件导通,使得ml对地放电,反之,三端口非易失性器件关断,ml上的电压维持不变;由于整体工作时间短,可以近似认为放电电流恒定,阵列1的ml上的电压与成负相关阵列2的ml上的电压与成负相关(ml∝-c);

11、c)将两个阵列的ml送入电压比较器进行对比,即可得知和c的相对大小关系,进而判断不等式是否成立。

12、进一步地,所述准备阶段具体包括:

13、假设不等式为首先需要将n个参数wi存储到三端口非易失性器件中,考虑到单个三端口非易失性器件的存储数据范围有限,可以用一列上多个三端口非易失性器件来存储单个参数wi,并用n列来存储n个参数参数wi;同时,准备一种合适的输入变量满足

14、与现有技术相比,本发明的有益效果如下:

15、本发明中的基于三端口非易失性器件的不等式条件判断求解器能够加速不等式条件判断过程。该架构充分利用了三个端口的特性,通过对除了接地端口外的另外两个端口进行操作,使得非易失性器件的状态同时受到两个信号的控制,进而满足不等式运算。

技术特征:1.一种基于三端口非易失性器件的不等式条件判断求解器,其特征在于,包括两个阵列和电压比较器,两个所述阵列的输出信号线连接至电压比较器的两个输入端,两个阵列分别为阵列1和阵列2,所述阵列包括m×n个不等式单元、pmos和电容cml,每个不等式单元包括一个三端口非易失性器件,所述三端口非易失性器件的栅极与输入信号g相连,漏极与ml相连,源极与地相连,同一阵列的三端口非易失性器件共用一根信号线ml,同一列三端口非易失性器件共用一根输入线g,所述pmos的栅极与输入信号vpre相连,漏极与ml相连,源极与电源相连,所述电容cml与ml和地相连。

2.根据权利要求1所述的一种基于三端口非易失性器件的不等式条件判断求解器,其特征在于,所述三端口非易失性器件为fefet或1fefet-1r或由1reram-1t构成的不等式单元。

3.根据权利要求1所述的一种基于三端口非易失性器件的不等式条件判断求解器,其特征在于,所述电压比较器为一个二级比较器。

4.一种如权利要求1或2或3所述不等式条件判断求解器的操作方法,其特征在于,包括:

5.根据权利要求4所述的操作方法,其特征在于,所述准备阶段具体包括:

技术总结本发明公开了发明公开了一种基于三端口非易失性器件的不等式条件判断求解器及其操作方法,包括两个阵列和电压比较器,阵列包括m×n个不等式单元、PMOS和电容C<subgt;ML</subgt;,不等式单元包括三端口非易失性器件,三端口非易失性器件的栅极与输入信号G相连,漏极与ML相连,源极与地相连,PMOS的栅极与输入信号V<subgt;pre</subgt;相连,漏极与ML相连,源极与电源相连,电容C<subgt;ML</subgt;与ML和地相连。本发明充分利用了非易失性器件的存储特性和三端口特性,实现了将不等式的参数存储在阵列中,并根据不等式输入进行不等式是否成立的条件判断功能。技术研发人员:尹勋钊,钱煜,卓成受保护的技术使用者:浙江大学技术研发日:技术公布日:2024/8/20本文地址:https://www.jishuxx.com/zhuanli/20240822/278413.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表