一种PXIe总线集成重构系统

- 国知局

- 2024-08-22 14:23:34

本发明涉及电子,特别是涉及一种pxie总线集成重构系统。

背景技术:

1、pxie总线自动测试系统因为被测对象的不同,可能用到rs422、rs485、s232这三种接口中的任意组合。自动测试系统的通用化和小型化是工业界一直以来追求的目标。通常这三种总线都集成在不同的pxie总线电路板上,为了通用性就必须集成3种板卡,增大了测试系体积,这就和小型化相矛盾;同时外部接口也需要三种接口并列,浪费接口资源,不够灵活。

技术实现思路

1、为了克服现有技术的不足,本发明的目的是提供一种pxie总线集成重构系统,本发明解决了现有技术中rs422、rs485、s232这三种总线集成在不同的pxie总线电路板上,导致测试系统体积大和成本过高的问题。

2、为实现上述目的,本发明提供了如下方案:

3、一种pxie总线集成重构系统,包括:

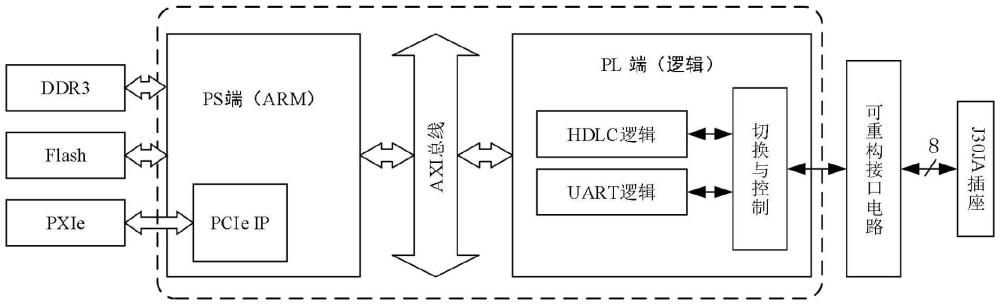

4、依次连接的通讯接口、ps端、axi总线、pl端和可重构接口电路;

5、所述通讯接口用于将上位机命令传输到所述ps端,所述ps端用于利用pcie硬核对接收到的上位机命令进行解析和回执,所述axi总线将解析后的命令传输到所述pl端,所述pl端用于对解析后的命令进行逻辑控制,输出控制信号和电气特性,所述可重构接口电路用于根据所述控制信号和电气特性选择串口通道,其中,所述串口通道设置为8个,每个串口通道均配置为rs422、rs485或rs232。

6、优选地,所述ps端为内嵌arm的fpga芯片。

7、优选地,所述rs485为半双工设备。

8、优选地,所述rs422为全双工设备。

9、优选地,所述每个串口通道均包括一个rs422/485收发器。

10、优选地,所述每个串口通道的通讯协议均配置成同步/异步/hdlc。

11、优选地,所述pl端包括:

12、uart协议,hdlc协议,选择单元;

13、uart协议用于波特率和字结构设置逻辑、数据读写控制逻辑、数据发送逻辑和数据接收逻辑,所述hdlc协议用于根据协议插入“0x7e”、插0、crc校验的逻辑、发送数据逻辑和接收数据逻辑,所述选择单元用于完成协议选择以及输出控制信号选择接口的电气特性。

14、本发明公开了以下技术效果:

15、本发明提供了一种pxie总线集成重构系统,包括:依次连接的通讯接口、ps端、axi总线、pl端和可重构接口电路;所述通讯接口用于将上位机命令传输到所述ps端,所述ps端用于利用pcie硬核对接收到的上位机命令进行解析和回执,所述axi总线将解析后的命令传输到所述pl端,所述pl端用于对解析后的命令进行逻辑控制,输出控制信号和电气特性,所述可重构接口电路用于根据所述控制信号和电气特性选择串口通道,其中,所述串口通道设置为8个,每个串口通道均配置为rs422、rs485或rs232。本发明通过一个模块上集成了8个通道,覆盖常用的rs232、rs422、rs485,通用性强且体积小;每个通道都可以配置成rs232、rs422、rs485中任意一种电气接口,每个通道的通讯协议都可以选择是异步通讯还是同步通讯;在主控板上集成了arm,可以自主处理数据。

技术特征:1.一种pxie总线集成重构系统,其特征在于,包括:

2.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述ps端为内嵌arm的fpga芯片。

3.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述rs485为半双工设备。

4.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述rs422为全双工设备。

5.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述每个串口通道均包括一个rs422/485收发器。

6.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述每个串口通道的通讯协议均配置成同步/异步/hdlc。

7.根据权利要求1所述的一种pxie总线集成重构系统,其特征在于,所述pl端包括:

技术总结本发明提供了一种PXIe总线集成重构系统,涉及电子技术领域,包括:依次连接的通讯接口、PS端、AXI总线、PL端和可重构接口电路;所述通讯接口用于将上位机命令传输到所述PS端,所述PS端用于利用PCIe硬核对接收到的上位机命令进行解析和回执,所述AXI总线将解析后的命令传输到所述PL端,所述PL端用于对解析后的命令进行逻辑控制,输出控制信号和电气特性,所述可重构接口电路用于根据所述控制信号和电气特性选择串口通道,其中,所述串口通道设置为8个,每个串口通道均配置为RS422、RS485或RS232。本发明解决了现有技术中RS422、RS485、S232这三种总线集成在不同的PXIe总线电路板上,导致测试系统体积大和成本过高的问题。技术研发人员:许永辉,鹿翔,彭双威受保护的技术使用者:哈尔滨工业大学技术研发日:技术公布日:2024/8/20本文地址:https://www.jishuxx.com/zhuanli/20240822/278523.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。