针对循环冗余码级联极化码连续消除译码算法的纠错方法、系统

- 国知局

- 2024-08-22 14:52:13

本技术涉及编码解码,尤其涉及一种针对循环冗余码级联极化码连续消除译码算法的纠错方法、系统。

背景技术:

1、在5g极化码通信技术中,"et"(early termination)是一种优化极化码解码过程的技术,它允许解码器在确定最终解码结果之前就终止解码过程。这种方法的重要性在于它显著提高了解码效率和处理速度,这对于满足5g网络对高速率和低延迟的要求至关重要。通过et,可以减少不必要的计算,加快数据传输,同时保持高解码准确性,从而使5g网络能够支持更快速和响应更敏捷的通信服务。

2、物联网设备的数量正在迅速增加,这包括智能家居设备、工业传感器、医疗设备等。这些设备通过互联网相互连接,实现数据共享。在物联网领域,数据传输的准确性至关重要,尤其是在关键应用如医疗保健、交通管理和工业自动化中。传输错误可能导致重大后果,因此采用高效且可靠的数据传输协议和技术是必须的。然而与传统计算设备相比,物联网设备的存储空间通常较小。这限制了它们存储数据的能力,尤其是在需要长期存储或处理大量数据的场景中。许多物联网设备是电池驱动的,特别是那些部署在无线和远程环境中的设备。因此,能源效率成为设计和操作物联网设备的一个重要考虑因素。

技术实现思路

1、针对以上问题,本发明提出了一种针对循环冗余码级联极化码连续消除译码算法的纠错方法、系统。

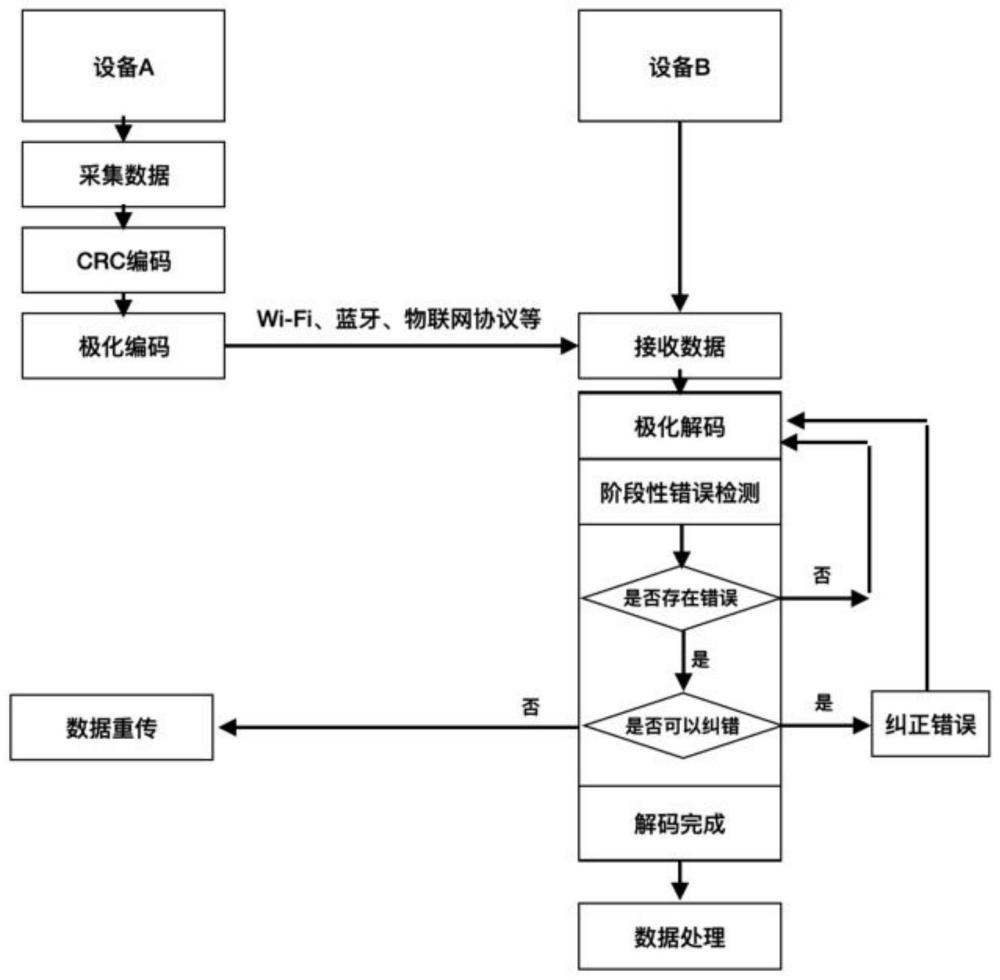

2、所述方法应用的系统包括数据采集设备、数据接收设备;

3、所述方法包括数据采集设备采集数据,将数据划分为固定大小的数据块,对每个数据块进行crc编码生成crc码,对crc码进行极化编码,并将极化编码后数据发送给数据接收设备的步骤;

4、以及

5、数据接收设备接收极化编码后数据,并对数据同步进行解码、检错,然后纠错的步骤。

6、进一步的,crc编码的流程包括确定循环冗余码生成多项式g(x)及其阶、生成crc码的奇偶校验矩阵h、生成校验位,将crc校验位添加到每个对应的数据块指定位置。

7、进一步的,极化编码是对crc码进行序列交织,交织过程,对奇偶校验矩阵h执行如下步骤:

8、步骤3.1:从左至右遍历该矩阵第1行各个元素,若遇到元素为1,则将该元素所在列移动至矩阵最左侧元素不为1的列,原来的列往后平移,依次类推,直到该行所有元素遍历完;

9、步骤3.2:针对3.1执行完后形成的新的矩阵的第1行,从第一列开始遍历该行元素值为1的列,如果某列下一行元素为1,则将该列移动到矩阵最左侧上下两行不同时为1的位置,其他列向后平移,依次类推,直到该行元素值为1的列都遍历完;

10、步骤3.3:继续对后续各行进行遍历操作,操作时将当前行当做前述各个步骤s3.1和s3.2所述的的第一行,最后得到变换后矩阵hc。

11、进一步的,极化编码流程执行完成后,生成位置标记数组,该数组有两行元素,第一行各元素表示变换后矩阵hc各列在原始的奇偶校验矩阵h中的位置,第二行各元素表示变换后矩阵hc各行最后一个1出现的位置,该位置为校验位,即需要检错的位置。

12、进一步的,数据接收设备对数据同步进行解码、检错的流程,具体为:

13、利用连续消除译码算法解码,假定变换后校验矩阵hc第i行元素所构成向量为h'i=(hi,1,hi,2,hi,3,…,hi,j,0,0,0…),当连续消除译码算法解码第i行的校验位时,假定该行已经解码的序列为info_partial_decoded=(b1,b2,b3,…,bj,0,0,0…),如果h'i*info_partial_decoded≠0,则说明该校验位存在错误,否则不存在错误。

14、进一步的,当校验位检测到错误后,还需要执行确定重复区和非重复区的流程,具体为:将变换后矩阵hc中,当前校验位对应的行及下一行分别称为局部第一行、局部第二行;局部第一行中,从左到右,假定最后一个元素1所在列为第q列,局部第二行中,从q+1列开始,假定该行最后一个1元素所在第w列;将局部第一行位于第一列至第q列的区域,以及局部第二行位于第一列至第w列的区域作为特定区域,在特定区域范围内:如果某个区域内同一列上下两行元素均为1,则称该区域为重复区;重复区外,同一行元素连续为1的区域构成非重复区。

15、进一步的,数据接收设备执行的纠错流程,具体为:

16、步骤1:确定错误模式:假定检错流程中,在变换后矩阵hc第i行的校验位检测到错误,则继续对第i+1行的校验位进行检错,若第i+1个校验位校验结果为0,则为第一错误模式,执行步骤2,若第i+1个校验位校验结果不为0,则为第二错误模式,执行步骤3;

17、步骤2:先执行第一单比特错误纠错流程,不成功再执行第一双比特错误纠错;

18、第一单比特错误纠错流程是根据第i行非重复区各比特位的可靠性排序情况进行错误校验,或者预先设置阈值,将可靠性低于阈值的比特进行错误校验,进而完成纠错;

19、第一双比特错误纠错流程是根据第i行非重复区各比特位两两组合的可靠性乘积排序情况进行错误校验,或者预先设置阈值,将可靠性乘积低于阈值的比特进行错误校验,进而完成纠错;

20、步骤3:先执行第二单比特错误纠错流程,不成功再执行第二双比特错误纠错;

21、第二单比特错误纠错流程是根据第i行位于重复区内的各比特位的可靠性排序情况进行错误校验,或者预先设置阈值,将可靠性低于阈值的比特进行错误校验,进而完成纠错;

22、第二双比特错误纠错流程是对第i行重复区比特位进行两两组合、在第i行重复区和非重复区各随机挑选一个比特位进行两两组合、在第i行非重复区和第i+1行非重复区各随机挑选一个比特位进行两两组合;根据各组合的可靠性乘积排序情况进行错误校验,或者预先设置阈值,将可靠性乘积低于阈值的比特进行错误校验,进而完成纠错。

23、进一步的,当第一错误模式根据可靠性排序情况进行纠错时,具体如下:

24、第一单比特错误纠错流程包括步骤a1-1、a1-2:

25、步骤a1-1:从第i行非重复区选出信道可靠性最低比特位,对该位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则执行步骤a1-2;

26、步骤a1-2:从第i行非重复区选出信道可靠性倒数第z低的所有比特位,对这些位置进行逐一比特翻转,并重新对该行进行错误校验,若检验结果为0,则纠错完成,否则执行第一双比特错误纠错流程;其中,z大于1,小于n;

27、第一双比特错误纠错流程包括步骤b1-1、b1-2:

28、步骤b1-1:对第i行非重复区比特位进行两两组合,从中选取信道可靠性乘积倒数第一的比特位组合,对这两个位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则继续纠错;

29、步骤b1-2:选取比特位信道可靠性乘积倒数第r低的所有比特位组合,对这些组合的两个位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则纠错失败,结束纠错,其中r大于1,小于n为码字长度。

30、进一步的,当第二错误模式根据可靠性排序情况进行纠错时,具体如下:

31、第二单比特错误纠错流程包括步骤a2-1、步骤a2-2:

32、步骤a2-1:从第i行重复区选出信道可靠性最低比特位,对该位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则继续纠错;

33、步骤a2-2:从第i行重复区选出信道可靠性倒数第z低的所有比特位,对这些位置进行逐一比特翻转,并重新对该行进行错误校验,若检验结果为0,则纠错完成;否则继续从第i行重复区选择其他比特位继续纠错,如果出现检验结果为0,则纠错成功,否则纠错失败,执行第二双比特模式;

34、第二双比特错误纠错流程包括步骤b2-1、b2-2:

35、步骤b2-1:对第i行重复区比特位进行两两组合;在重复区和非重复区各随机挑选一个比特位进行两两组合;在第i行非重复区和第i+1行非重复区各随机挑选一个比特位进行两两组合;计算所有组合的信道可靠性乘积,从中选出乘积最低的组合,对这两个位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则执行步骤b2-2;

36、步骤b2-2:选取可靠性倒数第r低的所有比特位组合,对这些组合的两个位置进行比特翻转,重新对该行进行错误校验,若检验结果为0,则纠错完成;否则结束纠错,其中

37、(过程中z和r的具体值根据设备应用环境设定)

38、一种针对循环冗余码级联极化码连续消除译码算法的纠错系统,包括数据采集设备、数据接收设备,所述系统用于执行针对循环冗余码级联极化码连续消除译码算法的纠错方法。

39、本发明的技术效果是:

40、本发明提出一种针对循环冗余码级联极化码连续消除译码算法的纠错方案,在提前终止之前进行错误检测和纠错,从而实现更高效的检测数据传输;相较于传统的循环冗余码级联极化码检错方案,本方案的检错过程和解码过程是同步进行的,从而能够及时检测到错误并进行处理,以尽量减少物联设备的能源消耗和传输时延,确保数据传输的完整性、有效性。

41、本发明可广泛的应用于5g通信、卫星通信、物联网领域内。

本文地址:https://www.jishuxx.com/zhuanli/20240822/280182.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表