一种集成电路测试系统及方法与流程

- 国知局

- 2024-09-05 14:48:29

本发明属于集成电路检测,具体涉及一种集成电路测试系统及方法。

背景技术:

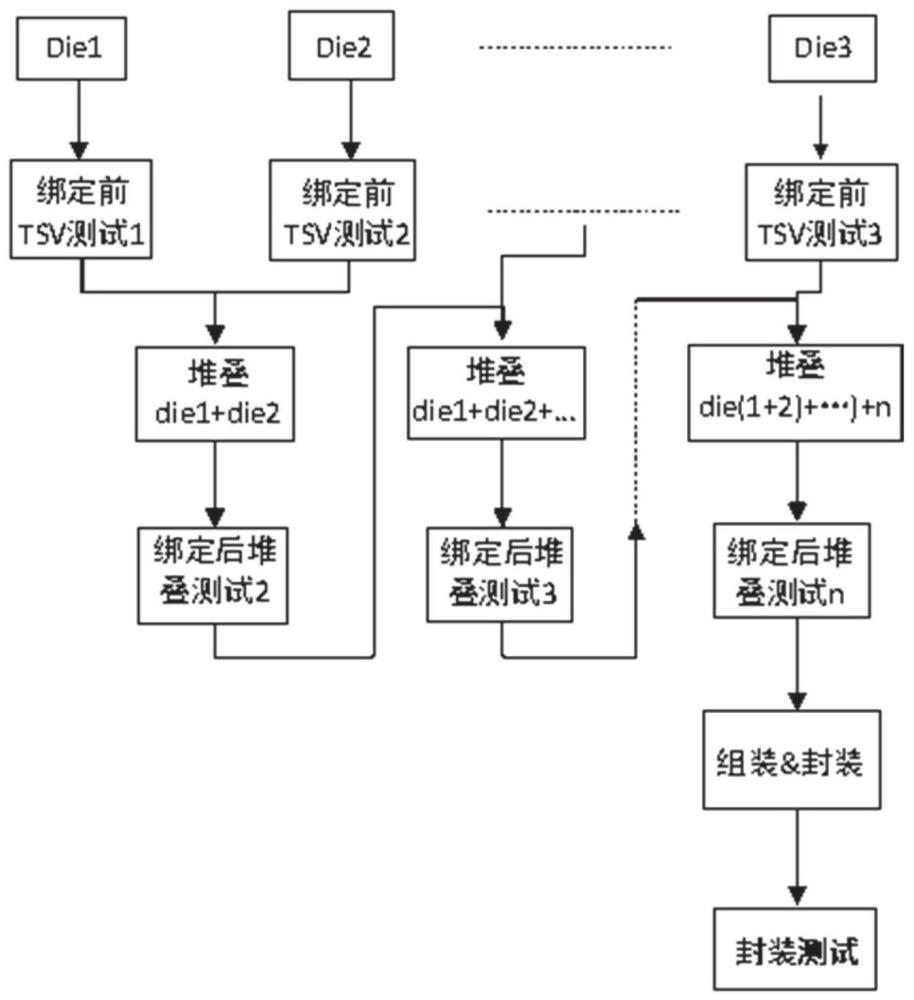

1、随着集成电路规模的增大,其特征尺寸不断缩小,但是互连线尺寸,尤其是全局互连线尺寸却没有同比例缩小,因此在二维环境下布线越来越拥挤,线上延时增加,线上功耗增加,都成为芯片性能提升的瓶颈。2.5d设计并不能解决走线和性能的问题;当将一个原本很大的模具分割成更小的部件以创建一个2.5d的设计时,走线不能由于水平排列而减少,在这种情况下,性能也没有提高,因为导线长度没有减少,每个模间信号都必须通过介质层,因此,与大型平面芯片相比,全局导线的平均长度甚至会增加;然而,由于如此大的平面芯片,产率低,成本高,可能不可行;而基于tsv的3d设计可有效缩短平均互连线的长度,降低了信号延时,使芯片整体性能得到显著提升,互连线上的功耗显著降低,3d多层堆栈结构显著提高了芯片的集成度。

2、作为所有的微电子产品,3d芯片由于短、开、空形成等原因,不同节点的多die之间通过连接出现的不可预见的缺陷,即使与已知的好晶圆叠加,仍有不可避免的缺陷,失败可能发生在tsv键的叠加过程中,进而导致丢弃完整的多模芯片,将贡献巨大的产量损失和总soc生产成本,因为所有堆叠成芯片的晶圆都是在预结合tsv测试之后进行的,堆叠过程后造成的故障,需要一个可行的解决方案来修复芯片之间失效的连接,因此需要进行测试,现有的相关技术中对于3d集成电路的通常采用单一测试时机,且对于新的基于tsv的互连器和由于额外的3d处理步骤而产生的新的内部缺陷,无法进行检测和修复。

技术实现思路

1、针对现有技术中存在的问题,本发明提供一种集成电路测试系统及方法,用以解决现有相关技术中对于3d多层堆栈结构检测不全面的技术问题。

2、本发明是通过以下技术方案来实现:

3、一种3d集成电路测试系统,包括环形晶振测试电路、tsv bist修复机制电路和3ddft测试电路;所述环形晶振测试电路用于检测绑定前tsv结构的故障,所述tsv bist修复机制电路用于绑定后的tsv bist测试,所述3d dft测试电路用于封装级3d集成电路进行检测。

4、进一步的,所述环形晶振测试电路包括第一多路选择器和第二多路选择器,所述第一多路选择器的输入端接入func_in1信号,并通过多个串联的第一逆变器连接tsv1,所述第二多路选择器的输入端接入func_in2信号,并通过和前述相同数量的多个串联的第二逆变器连接tsv2,所述tsv1和tsv2之间至少连接晶粒die1和晶粒die2,所述tsv1还连接第二多路选择器的的输入端,所述tsv2还连接第三逆变器的输入端和detector,所述第三逆变器的输出端连接第一多路选择器输入端。

5、进一步的,所述detector包括连接tsv2的电阻r1和二极管d1,所述电阻r1另一端接地,所述二极管d1另一端连接pad。

6、进一步的,所述tsv bist修复机制电路的写组包括设置于主模master die的多路复用器mux1和多路复用器mux2,所述多路复用器mux1的输入端接入tsv bist 1数据和本地输入数据,其输出端连接多路复用器mux2的输入端,多路复用器mux2的输入端还连接有修复数据1,其输出端经触发器sdff1和缓冲器tx_buf连接主模master die的tsv发射端tsvtx1;

7、还包括设置于从模slave die的多路复用器mux3,所述从模slave die的tsv接收端tsv rx依次连接有缓冲器rx_buf1和触发器sdff2,触发器sdff2连接多路复用器mux3的输入端,多路复用器mux3的输入端还连接有repair数据,其输出端接入从模slave die的逻辑块。

8、进一步的,所述tsv bist修复机制电路的读组包括设置于从模slave die的多路复用器mux4和多路复用器mux5,所述多路复用器mux4的输入端接入tsv bist 2数据和逻辑信号,其输出端连接多路复用器mux5的输入端,所述多路复用器mux5的输入端也接入tsvbist修复数据repair2数据,其输出端经触发器sdff3和缓冲器rx_buf2连接从模slave die的tsv发射端tsv rx;

9、还包括设置于用于连接从模slave die的tsv发射端tsv rx的主模master die的tsv发射端tsv tx,所述主模master die的tsv发射端tsv tx还连接缓冲器tx_buf2和触发器sdff4,所述触发器sdff4的输出端接入多路复用器mux6。

10、进一步的,所述3d dft测试电路包括用于在芯片堆栈中上下传输信息的灵活并行端口fpp,所述灵活并行端口fpp用于贯通多层晶粒die;

11、进一步的,所述灵活并行端口fpp被定义为一个关键元素是一个车道模板,车道模板设置有六个终端,所述六个终端包括:终端fpp pri与终端fpp sec、终端fpp to sideoutput与终端fpp from side、终端fpp to core output与终端fpp from core,所述终端fpp pri与终端fpp sec作为输入和输出;

12、所述车道模板包括五条信息传输路径,所述五条信息传输路径包括:

13、终端fpp pri至终端fpp sec;

14、终端fpp pri至终端fpp to side;

15、终端fpp pri至终端fpp to core;

16、终端fpp from core至终端fpp sec;

17、以及终端fpp from core至终端fpp to side。

18、所述灵活并行端口fpp均包括第一传输电路和第二传输电路,所述第一传输电路和第二传输电路均包括依次连接的寄存器和多路复用器mux7。

19、进一步的,所述ptap控制电路包括控制器ptap 1,所述控制器ptap1用于接收tdi信号、tms信号和tck信号,输出tdo信号;

20、所述控制器ptap1连接有段插入位sib1和段插入位sib2,段插入位sib1连接有测试数据寄存器tdr1和段插入位sib3,段插入位sib2连接有测试数据寄存器tdr2,段插入位sib3连接有测试数据寄存器tdr3;

21、所述测试数据寄存器tdr1、测试数据寄存器tdr2和测试数据寄存器tdr3均连接控制器ptap2和晶粒die的晶圆包装寄存器dwr。

22、进一步的,所述测试数据寄存器tdr1、测试数据寄存器tdr2和测试数据寄存器tdr3均连接同一旁路寄存器bypass reg和指令寄存器instructing reg,旁路寄存器bypass reg接入多路复用器mux7,多路复用器mux7分别连接晶粒die a的晶圆包装寄存器dwr和多路复用器mux8,多路复用器mux输入侧接入指令寄存器instructing reg,输出侧经tsv结构接入下一层晶粒die b的控制器ptap2。

23、一种3d集成电路测试方法,包括以下步骤:

24、所述环形晶振测试电路基于tsv的震荡频率检测绑定前tsv结构的故障;

25、所述tsv bist修复机制电路采用后连接测试对绑定后的tsv bist测试;

26、所述3d dft测试电路采用整合异质ip的ip测试模式重用方法对封装级3d集成电路进行检测。

27、与现有技术相比,本发明具有以下有益的技术效果:

28、本发明提供一种集成电路测试系统及方法,包括环形晶振测试电路、tsv bist修复机制电路和3d dft测试电路;所述环形晶振测试电路用于检测绑定前tsv结构的故障,所述tsv bist修复机制电路用于绑定后的tsv bist测试,所述3d dft测试电路用于封装级3d集成电路检测;本技术基于环形晶振测试电路、tsv bist修复机制电路和3d dft测试电路分别在每次工艺步骤进行后,执行一个后续的测试,使得在出现下游成本之前,尽可能的捕获缺陷,对于绑定前的tsv测试,通过接入环形晶振测试电路基于tsv的震荡频率,从而判断出对应的故障tsv;采用tsv bist修复机制电路基于读写逻辑分析和判断故障tsv并进行修复,3d dft测试电路采用整合异质ip的ip测试模式重用方法对封装级3d集成电路进行统一性检测,提高了测试的效率和简易性。

本文地址:https://www.jishuxx.com/zhuanli/20240905/288180.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表