一种高速控制的偏转器驱动的制作方法

- 国知局

- 2024-09-11 14:39:18

本发明涉及偏转器驱动领域。更具体地说,它涉及一种高速控制的偏转器驱动装置和方法。

背景技术:

1、偏转器广泛应用于精密加工、等工业用途,而偏转器驱动在运用上通常都是mcu直接连接到dds产生频率,产生频率的速率一般为us级且都是一路一路的频率输出,达不到目前偏转器驱动的使用需求。

2、因此,如何能够进一步提高频率的速率,并且实现并行控制多路的偏转器驱动成为目前亟需解决的技术问题。

技术实现思路

1、本发明的目的在于提供提出一种能够快速控制多路dds同步生成频率,且频率的速率可以达到ns级别的偏转器驱动装置和驱动方法。

2、为达此目的,本发明采用以下技术方案:

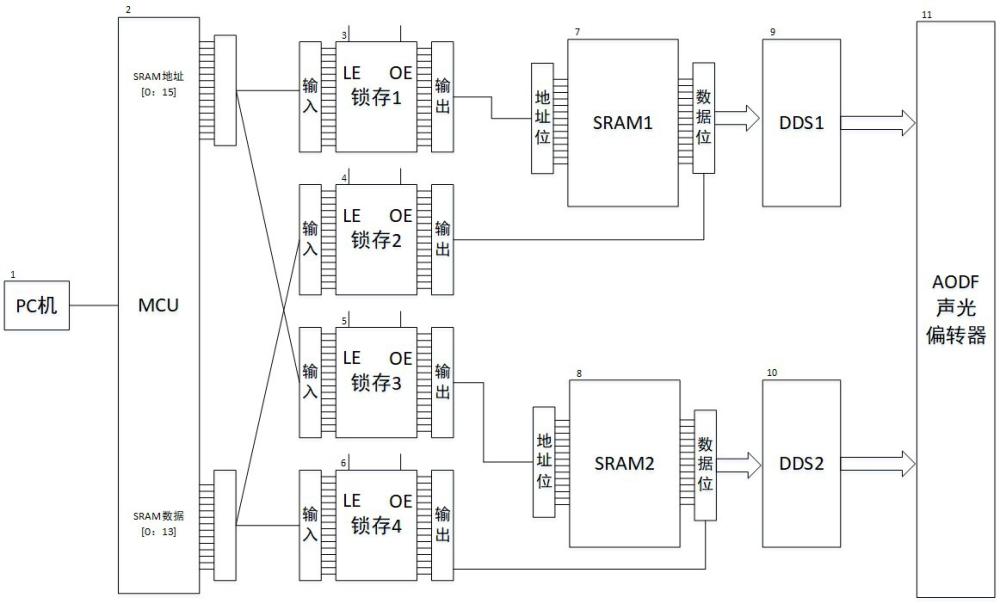

3、一种高速控制的偏转器驱动装置,包括微处理器mcu、四个锁存器锁存1,锁存2,锁存3和锁存4、存储器sram1和sram2、数字式频率合成器dds1和dds2,以及二维声光偏转器aodf;

4、所述mcu生成用于控制sram1和sram2的地址数据和用于控制所述aodf的频率数据;

5、所述锁存1和锁存3的输入连接所述mcu的地址输出口,用于将mcu输出的地址数据分别提供给所述sram1和sram2的地址端口;所述锁存2和锁存4的输入连接所述mcu的数据输出口,用于将mcu输出的频率数据分别提供给所述sram1和sram2的数据端口;

6、所述sram1和sram2分别连接至dds1和dds2,用于同时将所述频率数据传输出dds1和dds2;

7、所述dds1和dds2用于将所述频率数据注入所述aodf;

8、所述aodf,用于接收所述dds1、dds2输出的频率数据,从而输出用户需要的二维图案。

9、其中,还包括pc机,用于根据用户输入的位置数据生成频率数据并将所述频率数据下载到所述mcu。

10、其中,所述mcu 用于设置sram1和sram2为写入模式,以将频率数据分别写入到sram1和sram2中;所述mcu还用于设置sram1和sram2为读取模式,并共用mcu的地址控制以将所述频率数据从sram1和sram2分别传输给dds1和dds2。

11、其中,所述dds1和dds2均连接至所述aodf,并在同一时钟信号控制下根据所述频率数据形成频率阵列注入所述aodf。

12、其中,所述地址数据为16位地址数据,所述频率数据为14位频率数据,所述14位频率数据包括6个地址位和8个数据位。

13、一种驱动所述偏转器驱动装置的方法,包括如下步骤:

14、s1,mcu设置sram1和sram2均为写入模式,以将频率数据分别写入到sram1和sram2中;

15、s2,通过锁存1和锁存2将频率数据写入到sram1;

16、s3,通过锁存3和锁存4将频率数据写入到sram2;

17、s4,sram1和sram2均被写入数据后,通过mcu设置sram1和sram2均为读取模式;

18、s5,通过mcu控制sram1和sram2同步将频率数据传输给dds1和dds2;

19、s6,dds1和dds2在同一时钟信号的控制下,根据所述频率数据形成频率阵列注入所述aodf;

20、s7,所述aodf接收所述频率阵列,从而输出用户需要的二维图案。

21、其中,在步骤s1之前还包括:

22、s1’,在pc机中,根据用户输入的位置数据生成频率数据并将所述频率数据下载到所述mcu。

23、其中,步骤s2包括:

24、s21,mcu设置四个锁存器的oe使能,并设置锁存3和锁存4的le使能,使得锁存3和锁存4为锁存状态;

25、s22,设置锁存1和锁存2的le使能,mcu进行数据配置,以准备要写入到sram1的频率数据和该频率数据被写入到的sram1的地址;

26、s23,mcu数据配置完成后,设置锁存1和锁存2的le不使能,mcu输出的地址数据和频率数据分别通过锁存1和锁存2被提供给sram1;

27、s24,判断sram1的数据是否写入完毕,如未写入完毕,则返回步骤s22向sram1写入下一组数据。

28、其中,步骤s3包括:

29、s31,mcu保持控制四个锁存器的oe使能,并且设置锁存1和锁存2的le使能,使得锁存1和锁存2为锁存状态;

30、s32,设置锁存3和锁存4的le使能,mcu进行数据配置,以准备要写入到sram2的频率数据和该频率数据被写入的sram2的地址;

31、s33,mcu数据配置完成后,设置锁存3和锁存4的le不使能,mcu输出的地址数据和频率数据分别通过锁存3和锁存4被提供给sram2;

32、s34,判断sram2的数据是否写入完毕,如未写入完毕,则返回步骤s32向sram2写入下一组数据。

33、其中,步骤s5包括:

34、s51,mcu控制锁存2和锁存4的oe不使能,输出口为高阻状态;

35、s52,设置锁存1和锁存3的le使能,使得锁存1和锁存3为锁存状态,mcu生成地址控制位,使其对准要在sram1和sram2中寻址的初始地址;

36、s53,mcu数据配置完成后,设置锁存1和锁存3的le不使能,mcu输出的地址控制位分别通过锁存1和锁存3同时被提供给sram1和sram2;

37、s54,sram1和sram2根据所述地址在sram1和sram2中分别寻址各获得一组频率数据并分别发送给dds1和dds2。

38、本发明具有如下优点:

39、1、通过采用常见的mcu、sram、dds等元器件进行电路设计,实现并行控制多路的偏转器驱动,频率切换速率可以达到ns级别;

40、2、通过增加地址位,可快速形成频率阵列、注入aodf的频率。

技术特征:1.一种高速控制的偏转器驱动装置,包括微处理器mcu、四个锁存器锁存1,锁存2,锁存3和锁存4、存储器sram1和sram2、数字式频率合成器dds1和dds2,以及二维声光偏转器aodf;

2.根据权利要求1所述偏转器驱动装置,其特征在于:

3.根据权利要求1或2所述偏转器驱动装置,其特征在于:

4.根据权利要求1-3任一项所述偏转器驱动装置,其特征在于:

5.根据权利要求1-4任一项所述偏转器驱动装置,其特征在于:

6.一种驱动如权利要求1-5任一项所述偏转器驱动装置的方法,包括如下步骤:

7.根据权利要求6所述方法,其中,在步骤s1之前还包括:

8.根据权利要求6或7所述方法,其中,步骤s2包括:

9.根据权利要求6-8任一项所述方法,其中,步骤s3包括:

10.根据权利要求6-9任一项所述方法,其中,步骤s5包括:

技术总结一种高速控制的偏转器驱动装置和方法,所述装置包括微处理器MCU、四个锁存器锁存1,锁存2,锁存3和锁存4、存储器SRAM1和SRAM2、数字式频率合成器DDS1和DDS2,以及二维声光偏转器AODF。通过采用常见的MCU、SRAM、DDS等元器件进行电路设计,实现并行控制多路的偏转器驱动,频率切换速率可以达到ns级别,并通过增加地址位,可快速形成频率阵列、注入AODF的频率。技术研发人员:王辉,陈秋华,翁文栋,林楷文,王城强,陈伟,张星受保护的技术使用者:福建福晶科技股份有限公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/291711.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表