具有时序控制器的扩频视频传输集成的制作方法

- 国知局

- 2024-09-11 15:14:11

本发明一般而言涉及在显示设备的显示面板上显示视频。更具体而言,本发明涉及一种与编码器集成的时序控制器,该编码器将数字信号编码成模拟信号以用于显示器。

背景技术:

1、图像传感器、显示面板和视频处理器不断竞相实现更大的格式、更大的色深、更高的帧速率和更高的分辨率。本地站点视频传输包括性能缩放瓶颈,这些瓶颈限制吞吐量并损害性能,同时消耗更多的成本和功率。消除这些瓶颈可以提供优势。

2、例如,随着显示分辨率的增加,从视频源传送到显示屏的视频信息的数据速率呈指数增加:从十年前的用于全hd的3gbps到用于新的8k屏幕的160gbps。通常,具有4k显示分辨率的显示器在60hz时要求大约20gbps的带宽,而在120hz时要求40gbps。而且,8k显示器在60hz时要求80gbps,在120hz时要求160gbps。

3、目前,常规的列(或源极)驱动器依赖于显示设备内的接线器(wiring loom),出于多种原因,该接线器可以限制缩放到更大的格式和更高的帧速率。一方面,复杂接线器所需的面积和体积变得太大,这意味着实现接线器的印刷电路的尺寸和成本超出了实际限制。另外,源极驱动器的dac限于8位的分辨率;进一步的增加将导致过高的数据速率并消耗过多的功率。这些限制迫使显示设备行业出现体系架构中断,从而增加成本和风险。

4、到目前为止,使用低电压差分信令(lvds)数据传送的变体以数字方式传送数据,使用每个信号对16gbps的位速率(取决于体系架构),并并行化信号对以实现所需的总位速率。然后需要在显示器的源极驱动器处使用数模转换将这个数字信息动态转换成模拟像素信息。

5、如今,大多数源极驱动器数模转换器要求8位;很快,数模转换可能需要10位甚至12位,然后维持足够快的数据速率将变得非常困难。因此,显示器必须在非常短的时间内对数字数据进行计时,从而导致数字信号传输的不稳定。由于现有数字传输的限制引起的另一个问题是并非每个样本的所有12位或10位甚至8位都在显示面板内被输送;现代显示器内压缩方案每个样本仅携带6位,从而限制了显示器的色深。

6、因而,期望新的装置和技术来消除在显示器的源极驱动器处进行数模转换的需要,增加带宽,并利用在显示单元内生成的模拟视频信号。

技术实现思路

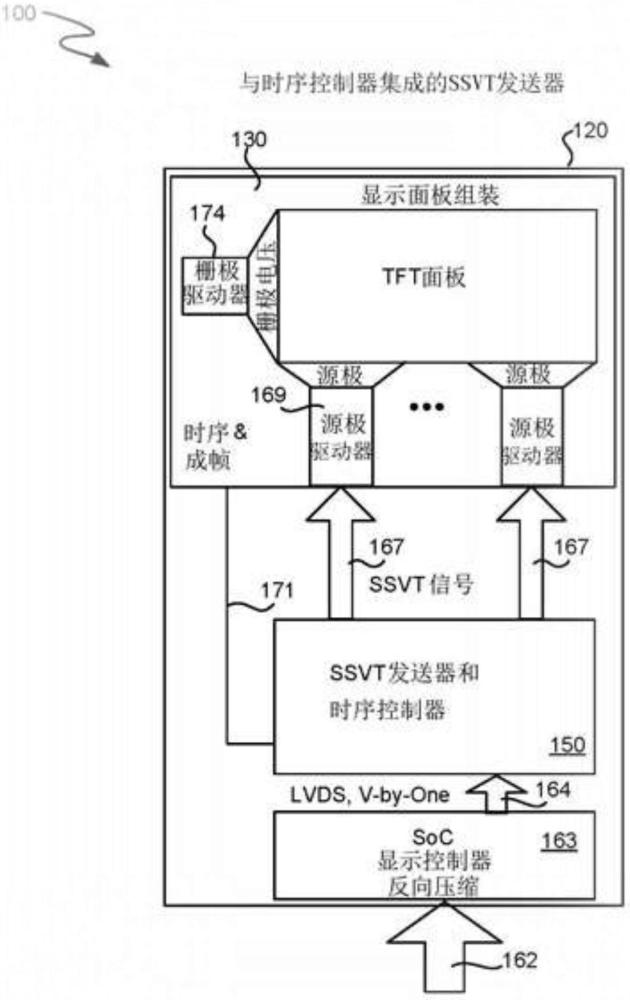

1、为了实现前述,并且根据本发明的目的,显示设备的时序控制器与具有至少一个编码器的ssvt发送器集成以允许在显示设备的显示控制器与显示面板的源极驱动器之间传输模拟信号。

2、认识到像素亮度水平的数字表示(例如,8位或10位数字)是视频数据的差的表示,尤其是在视频传输期间,而表示那些亮度水平的模拟电压是更好的表示并具有更大的分辨率。因此,本发明提出使用表示像素亮度水平的电压在模拟域中在显示设备内传输视频数据。

3、本发明的优点包括降低功耗。在现有技术中,功耗显著地制约了显示性能;使用本发明,显示电子器件消耗的功率更少。下面描述的本发明的实施例可以缩放到任意大的格式和帧速率,面板驱动消耗的功率减少多达50%,并提供大于十倍的噪声抑制。另外,实施例提供抗噪性和em隐蔽性,因为显示设备的emi/rfi发射将远低于规定的限制。还有,新型模拟信号的传输距离可以远大于常规的以太网或hdbaset信号的传输距离。并且,虽然常规的传输对高速数字电路使用昂贵的混合信号处理,但本发明的实施例利用成熟的模拟处理以获得更大的灵活性和更低的生产成本。另外,接线器的尺寸减小,因此在显示面板的边缘区域中占用更少的空间。

4、另外,使用扩频视频传输(ssvt)在显示面板的显示控制器和源极驱动器之间的显示设备内进行数据传送可以减小硅面积,从而减少与视频传输相关联的芯片成本,对于4k60hz面板可减少高达3倍,而对于8k 120hz面板可减少高达10倍。

5、在具体实施例中,ssvt发送器(及其编码器)和集成的时序控制器在单个集成电路内。这种集成的主要优点是数字视频传送发生在芯片上,因此将数字信号从tcon带到编码器并不困难。也会有功率和成本益处。另一个优点是,由于节省引脚和共享部件,组合的芯片面积将会更小。在变体中,发送器、tcon和soc都在集成电路中。将ssvt发送器集成到tcon中也符合现有的行业惯例,其中tcon具有集成的数字视频传输(如ceds)。在另一个具体实施例中,ssvt发送器和时序控制器芯片(或发送器、tcon和soc)是显示面板驱动芯片组的一部分,一个或多个其它半导体芯片接收ssvt信号并实现显示器的源极驱动器。

技术特征:1.一种将时序控制器与发送器集成的装置,所述装置包括:

2.如权利要求1所述的装置,其中所述装置被集成在所述显示设备的单个集成电路内。

3.如权利要求1所述的装置,其中每个所述编码器的所述一系列模拟值被传递到所述显示设备的源极驱动器的对应解码器。

4.如权利要求1所述的装置,还包括:

5.如权利要求1所述的装置,其中所述装置位于所述片上系统的大约10cm内。

6.如权利要求1所述的装置,其中所述栅极驱动器控制器还被布置为接收源自解包器的成帧标志并基于所述成帧标志输出所述栅极驱动器控制信号。

7.如权利要求6所述的装置,其中所述解包器从所述片上系统接收数字视频信号并产生所述数字视频样本的所述多个流。

8.如权利要求1所述的装置,其中所述分发器以第一时钟频率输入所述流的所述数字视频样本并以比所述第一时钟频率慢的第二时钟频率将所述输入向量输出到所述输入向量的所述dac,从而影响时钟域交叉。

9.如权利要求1所述的装置,其中每个输入向量具有长度n,其中每个编码器参考每个长度为l的n个相互正交的码的预定码集将所述编码器对应的n个模拟视频样本的输入向量编码成一系列l个模拟值,所述码中的每个码用于对所述n个模拟视频样本中的一个进行编码。

10.如权利要求1所述的装置,其中每个所述编码器的多个所述一系列模拟值在所述显示器的源极驱动器处被多路复用。

11.如权利要求1所述的装置,其中所述片上系统(soc)与所述装置内的所述时序控制器和所述发送器集成,并且其中所述soc接收所述显示设备外部的数字视频信号,数字视频样本的所述流从所述数字视频信号得出。

12.如权利要求9所述的装置,其中l>=n>=2。

13.如权利要求9所述的装置,其中n>l>=2。

14.如权利要求1所述的装置,其中所述显示器包括至少一个源极驱动器,所述源极驱动器被布置为从每个所述编码器接收所述一系列模拟值并且解码所述一系列模拟值以产生多个模拟样本用于在所述源极驱动器的输出端上输出,从而数字视频样本的所述流被显示在所述显示设备的所述显示器上。

15.一种将时序控制器与发送器集成的装置,所述装置包括:

16.如权利要求15所述的装置,其中所述装置被集成在所述显示设备的单个集成电路内。

17.如权利要求15所述的装置,其中所述每个编码器的所述一系列模拟值被传递到所述显示设备的源极驱动器的对应解码器。

18.如权利要求15所述的装置,还包括:

19.如权利要求15所述的装置,其中所述装置位于所述片上系统的大约10cm内。

20.如权利要求15所述的装置,其中所述栅极驱动器控制器还被布置为接收源自解包器的成帧标志并基于所述成帧标志输出所述栅极驱动器控制信号。

21.如权利要求20所述的装置,其中所述解包器从所述片上系统接收数字视频信号并产生所述数字视频样本的所述多个流。

22.如权利要求15所述的装置,其中所述分发器以第一时钟频率输入所述流的所述数字视频样本并以比所述第一时钟频率慢的第二时钟频率将所述输入向量输出到所述编码器,从而影响时钟域交叉。

23.如权利要求15所述的装置,其中每个输入向量具有长度n,其中每个编码器参考每个长度为l的n个相互正交的码的预定码集将所述编码器对应的n个数字视频样本的输入向量编码成一系列l个数字值,所述码中的每个码用于对所述n个数字视频样本中的一个进行编码。

24.如权利要求15所述的装置,其中所述每个编码器的多个所述一系列模拟值在所述显示器的源极驱动器处被多路复用。

25.如权利要求15所述的装置,其中所述片上系统(soc)与所述装置内的所述时序控制器和所述发送器集成,并且其中所述soc接收所述显示设备外部的数字视频信号,数字视频样本的所述流从所述数字视频信号得出。

26.如权利要求23所述的装置,其中l>=n>=2。

27.如权利要求23所述的装置,其中n>l>=2。

28.如权利要求15所述的装置,其中所述显示器包括至少一个源极驱动器,所述源极驱动器被布置为从所述每个编码器接收所述一系列模拟值并且解码所述一系列模拟值以产生多个模拟样本用于在所述源极驱动器的输出端上输出,从而数字视频样本的所述流被显示在所述显示设备的所述显示器上。

29.一种将ddic-tcon(显示驱动器集成电路-时序控制器)与发送器集成的装置,所述装置包括:

30.如权利要求29所述的装置,其中所述装置被集成在所述移动电话的单个集成电路内。

31.如权利要求29所述的装置,其中所述一系列模拟值被传递到所述移动电话的源极驱动器的对应解码器。

32.如权利要求29所述的装置,还包括:

33.如权利要求29所述的装置,其中所述装置位于所述片上系统的大约2cm内。

34.如权利要求29所述的装置,其中所述栅极驱动器控制器还被布置为接收源自解包器的成帧标志并基于所述成帧标志输出所述栅极驱动器控制信号。

35.如权利要求34所述的装置,其中所述解包器从所述片上系统接收数字视频信号并产生所述数字视频样本的所述至少一个流。

36.如权利要求29所述的装置,其中所述分发器以第一时钟频率输入所述数字视频样本并以比所述第一时钟频率慢的第二时钟频率将所述输入向量输出到所述dac,从而影响时钟域交叉。

37.如权利要求29所述的装置,其中所述输入向量具有长度n,其中所述编码器参考每个长度为l的n个相互正交的码的预定码集将n个模拟视频样本的所述输入向量编码成一系列l个模拟值,所述码中的每个码用于对所述n个模拟视频样本中的一个进行编码。

38.如权利要求37所述的装置,其中l>=n>=2。

39.如权利要求37所述的装置,其中n>l>=2。

40.如权利要求29所述的装置,其中所述显示面板包括源极驱动器,所述源极驱动器被布置为从所述每个编码器接收所述一系列模拟值并且解码所述一系列模拟值以产生多个模拟样本以用于在所述源极驱动器的输出端上输出,从而数字视频样本的所述流被显示在所述移动电话的所述显示面板上。

41.一种将ddic-tcon(显示驱动器集成电路-时序控制器)与发送器集成的装置,所述装置包括:

42.如权利要求41所述的装置,其中所述装置被集成在所述显示设备的单个集成电路内。

43.如权利要求41所述的装置,其中所述一系列模拟值被传递到所述移动电话的源极驱动器的对应解码器。

44.如权利要求41所述的装置,还包括:

45.如权利要求41所述的装置,其中所述装置位于所述片上系统的大约2cm内。

46.如权利要求41所述的装置,其中所述栅极驱动器控制器还被布置为接收源自解包器的成帧标志并基于所述成帧标志输出所述栅极驱动器控制信号。

47.如权利要求46所述的装置,其中所述解包器从所述片上系统接收数字视频信号并产生所述数字视频样本的所述至少一个流。

48.如权利要求41所述的装置,其中所述分发器以第一时钟频率输入所述数字视频样本并以比所述第一时钟频率慢的第二时钟频率将所述输入向量输出到所述编码器,从而影响时钟域交叉。

49.如权利要求41所述的装置,其中所述输入向量具有长度n,其中所述编码器参考每个长度为l的n个相互正交的码的预定码集将n个数字视频样本的所述输入向量编码成一系列l个模拟值,所述码中的每个码用于对所述n个数字视频样本中的一个进行编码。

50.如权利要求49所述的装置,其中l>=n>=2。

51.如权利要求49所述的装置,其中n>l>=2。

52.如权利要求41所述的装置,其中所述显示面板包括源极驱动器,所述源极驱动器被布置为从所述每个编码器接收所述一系列模拟值并且解码所述一系列模拟值以产生多个模拟样本用于在所述源极驱动器的输出端上输出,从而数字视频样本的所述流被显示在所述移动电话的所述显示面板上。

53.一种用于将视频传输到显示设备的显示面板的系统,所述系统包括:

54.如权利要求53所述的系统,其中所述发送器还包括:

55.如权利要求53所述的系统,其中所述编码是数字编码,并且其中所述发送器还包括将所述编码的输出转换成所述多个一系列模拟值的至少一个数模转换器(dac)。

56.如权利要求53所述的系统,其中所述发送器还包括:

57.如权利要求53所述的系统,其中所述发送器还包括:

58.一种用于将视频传输到移动电话的显示面板的系统,所述系统包括:

59.如权利要求58所述的系统,其中所述发送器还包括:

60.如权利要求58所述的系统,其中所述编码是数字编码,并且其中所述发送器还包括将所述编码的输出转换成所述多个一系列模拟值的至少一个数模转换器(dac)。

61.如权利要求58所述的系统,其中所述发送器还包括:

62.如权利要求58所述的系统,其中所述发送器还包括:

技术总结显示设备的时序控制器与编码器集成,用于在显示面板的显示控制器和源极驱动器之间传输模拟信号。时序控制器和集成的编码器位于集成电路内,并且是芯片组的一部分。集成电路紧接着位于显示设备的SoC之后或集成在SoC内。发送到时序控制器芯片的视频信号被解包为样本值,这些样本值被排列为样本的向量,每个编码器一个向量。每个向量被转换成模拟的、被编码,并且模拟电平被发送到源极驱动器,源极驱动器将其解码为模拟样本。或者,每个数字向量被编码,然后被转换成模拟的。行缓冲器使用存储器将一行像素信息呈现给编码器。移动电话具有带SSVT发送器的集成TCON。技术研发人员:埃亚尔·弗里德曼,托德·E·洛克夫受保护的技术使用者:HYPHY美国有限公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/293662.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。