针对像素驱动器存储器单元格的阵列的高效图像数据递送的制作方法

- 国知局

- 2024-09-14 14:22:45

本公开涉及以在位平面的持续时间内建立调制状态所需的与位平面相对应的单个数据位形式将图像数据高效地递送到像素驱动器存储器单元格(memory cell)。更具体地,这涉及将图像数据递送到脉宽调制显示器的像素。

背景技术:

1、半导体背板作为用于空间光调制器的组件的使用在本领域中是众所周知的。用于生成要由人类观看者观察的图像的微型显示器已被提供来销售达20多年,并且在公布的和专利文献中得到了充分证实。后来的应用已出现在电信装置中,其中相位对齐空间光调制器可用于通过使用通过调制液晶层而实现的合适相息图(相位掩模)将相干光束引导到所需位置。用于这两个类别的装置的背板技术通常是相同的。大画幅硅基液晶微显示器具有特定价值。它们见于用于商务会议支持的投影系统以及用于数字影院的投影仪。基于相同硅设计的大画幅相位对齐空间光调制器(slm)可用于扩展可引导到电信路由器中的不同传出端口的传入束的数量。

2、硅基液晶装置已经使用基于存储器装置的硅背板设计来实现。在早期示例中,timothy drabik博士在其博士论文《optically interconnected parallel processor arrays》,(佐治亚理工学院,佐治亚州亚特兰大,1989年12月) (以下简称drabik 1989),第125页中公开了使用sram作为脉宽调制64 × 64液晶阵列(通常称为硅基液晶(或lcos)装置)的基础。drabik 1989指出,sram可通过使用字节宽操作来写入,其中包括8个位的数据字节可被写入到所选择的行的8个存储器单元格,或者通过使用行页模式来写入,其中当所选择的行线(字线)保持为高时,包括64个存储器单元格的行上的所有八个字节可被写入。电子设计领域的那些普通技术人员将认识到,字节宽模式要求个别列可寻址,而行页模式并不明确要求该能力,但行页模式肯定可与将数据寻址到列的该手段兼容。

3、在关于drabik 1989的另一点中,同一页的论文指出如旨在提高操作速度而实现的sram的两个具体方面。第一方面是先前描述的行页模式,因为它将行的字线必须被拉高的次数从8次减少到1次。第二方面是增加逆变器电路以将每个像素驱动器的6晶体管sram电路与来自像素驱动器镜的负载隔离。drabik 1989报告称,这允许设定sram电路的状态所需的保持时间从几微秒(μsec)减少到几纳秒(nsec)。申请人指出,自硅基液晶显示器和空间光调制器最早期以来,人们一直在努力减少完成必要动作诸如写入数据所需的时间。

4、申请人先前已开发出纵横比为4096 × 2400 (128 × 75比例)的背板,其由水平和竖直方向上节距均为3.74微米(μm)的方形像素驱动器构成。用于此开发的目标过程是130纳米(nm)过程,其在铝像素镜下方使用铜电路和晶体管,其中具有可选的插入层以防止两个不同金属层之间的不希望的交互。像素镜不仅用来反射光,而且由底层电路所供应的与所需调制相对应的电压驱动。背板的阵列的图像对角线为0.70英寸(0.70”)。此解决方案和过程选取的一个限制在于像素镜的最大电压范围散布为近似4伏。5伏或更大的散布尤其对于相位对齐装置而言是理想得多的,在相位对齐装置中液晶单元格必须更厚,因为所需相位调制范围是振幅对齐显示器所需范围的至少两倍。此电压限制是由所选择的过程内可用的晶体管库以及将像素驱动器阵列面积保持在近似等于像素显示器节距的平方的面积内的需要造成的。附加地,行驱动器的高度和列驱动器的宽度必须符合针对该尺寸的像素节距。

5、申请人当前拥有美国专利7,443,374,其全部内容以引用方式并入,该专利公开了包括6晶体管sram和其他元件的像素驱动器设计,该像素驱动器设计已在250 nm过程、180nm过程和130 nm过程中实现。(特别参见图5至图8,包括对图6的修正。)

6、存在可接收本发明的益处的其他像素驱动器。例如,美国专利6,005,558中描述的像素驱动器(其全部内容以引用方式并入本文)也依赖于一位sram存储器单元格来建立像素驱动器的调制状态。6,005,558的像素驱动器和7,443,374的像素驱动器对相关联液晶层具有近似相同的影响,但是通过在其他方面基本上不同的手段实现这一点。依赖于一位sram或dram装置的其他像素驱动器可受益于本文所述的实现方式。

7、在本申请中,术语“导线(wire)”、“导体”和“线(line)”被假定意指导电介质,诸如铝、铜或多晶硅,但其他导电介质也在本公开的范围内。词语“端子”的使用意指一种导电介质,该导电介质可操作以连接到电路元件的节点,诸如逻辑门,或晶体管的源极、栅极或漏极,或者连接到半导体的块体。术语“字线(word line)”、“字线(wordline)”和“wline”全部由本领域的从业者使用,并且应被认为彼此等效。术语“行驱动器”和“字线驱动器”应被认为彼此等效。术语“位线(bit line)”、“位线(bitline)”和“列线”应被认为彼此等效。术语“列驱动器”和“位线驱动器”应被认为彼此等效。

技术实现思路

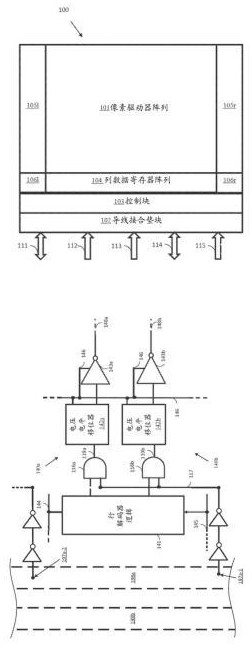

1、因此,本文所述的实现方式的目的是通过减少将数据平面加载到形成显示系统的一部分的背板的像素驱动器所需的时间来改进该背板。具体地,相对于其他设计可减少设置和保持时间要求的装置设计将使得能够更快地将数据写入每个像素驱动器的存储元件,并且还使得能够更快地写入整个像素驱动器阵列。这将意指总体数据速率比原本可能的更高。

技术特征:1.一种设备,包括:

2.如权利要求1所述的设备,其中所述第一多个虚设像素驱动器适于对所述字线的配置进行镜像。

3.如权利要求1或2中任一项所述的设备,其中所述第一多个虚设像素驱动器由多个所禁用的数据存储元件模拟。

4.如权利要求3所述的设备,其中所述多个所禁用的数据存储元件适于将沿着使能线的rc特性引入到触发启动电路的触发源。

5.如权利要求4所述的设备,其中沿着所述使能线的所述rc特性被确定为所述数据加载触发路径的rc特性。

6.如权利要求1所述的设备,其中所述列驱动器包括所禁用的数据存储元件。

7.如权利要求1至6中任一项所述的设备,其中所述行选择路径与所述字线正交对齐并且与所述位线平行对齐。

8.如权利要求1至7中任一项所述的设备,其中所述字线沿循所述字线路径内的所述行选择路径,并且所述位线沿循所述位线路径内的所述数据加载触发路径。

9.如权利要求1至8中任一项所述的设备,其中所述行选择路径设置在所述像素驱动器阵列外部,并且所述字线设置在所述像素驱动器阵列内。

10.如权利要求1至9中任一项所述的设备,其中所述数据加载触发路径设置在所述像素驱动器阵列外部,并且所述位线设置在所述像素驱动器阵列内。

11.如权利要求1至10中任一项所述的设备,其中所述字线路径内的所述行选择路径与所述位线平行对齐。

12.如权利要求1至11中任一项所述的设备,其中所述位线路径内的所述数据加载触发路径与所述字线平行对齐。

13.如权利要求1至12中任一项所述的设备,进一步包括:

14.如权利要求1至13中任一项所述的设备,其中所述行选择路径包括与第二行选择路径部分平行的第一行选择路径部分。

15.如权利要求14所述的设备,其中所述第一行选择路径部分包括具有虚设像素驱动器的行驱动器区段和不具有行驱动器的虚设像素驱动器区段。

16.如权利要求1至15中任一项所述的设备,其中所述行选择路径和所述数据加载触发路径包括在与所述像素驱动器阵列相关联的背板内。

17.如权利要求1至16中任一项所述的设备,其中所述像素驱动器阵列包括多个字线和多个位线,以及适于对所述多个字线和所述多个位线的配置进行镜像的虚设像素驱动器的阵列。

技术总结一种用于以高效方式将图像数据递送到形成像素驱动器的一部分的存储器单元格的背板设计包括速度匹配的字线设计和列数据寄存器释放信号递送设计,以及与行解码器信号电路速度匹配的互补位线递送设计,该行解码器信号电路操作以将字线驱动器拉到用以使得该行的存储器电路能够从每个列的列驱动器接收数据的状态。因为电路设计基本上相同,所以速度匹配在一定操作温度范围内是有效的。技术研发人员:李波,考希克·舍斯,埃德温·莱勒·哈德森受保护的技术使用者:谷歌有限责任公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/293707.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表