一种基于形式化验证的FPGA缺陷检查方法与流程

- 国知局

- 2024-09-14 14:40:29

本发明涉及fpga测试验证领域,适用于fpga中vhdl和verilog代码的缺陷检查,特别涉及一种基于形式化验证的fpga缺陷检查方法。

背景技术:

1、目前,在国内商业上目前基本还没有一家成熟的国内eda 软件公司研制出硬件描述语言缺陷检查软件;国内目前使用的缺陷检查软件大多是与国外相关企业合作或提供代理服务。德国onespin solutions公司的onespin 360产品是一套完整的fpga验证解决方案,可以帮助工程师确保其项目符合规范和标准。该软件提供了一系列功能强大的工具,包括形式化验证、逻辑等价性检查、异步时序分析等。这些工具以它强大且高效的形式化验证引擎为基础,帮助设计团队发现和解决硬件设计中的错误和安全漏洞,提高设计的可靠性和安全性。美国mentor graphics公司的questa是一个集成电路设计和验证工具套件,主要用于数字和模拟电路设计验证和仿真。它提供了一系列工具用于设计流程的不同阶段,其中questa formal是一款形式化验证工具。questa fromal 的功能包括定理证明、模型检查、约束随机验证等。它可以自动分析设计规范,并生成相应的数学表达式,然后使用形式化验证推理技术验证这些规范是否得到满足。但上述这些技术的缺陷是软件界面不支持中文,软件会出现卡死状态,规则描述不易理解。

技术实现思路

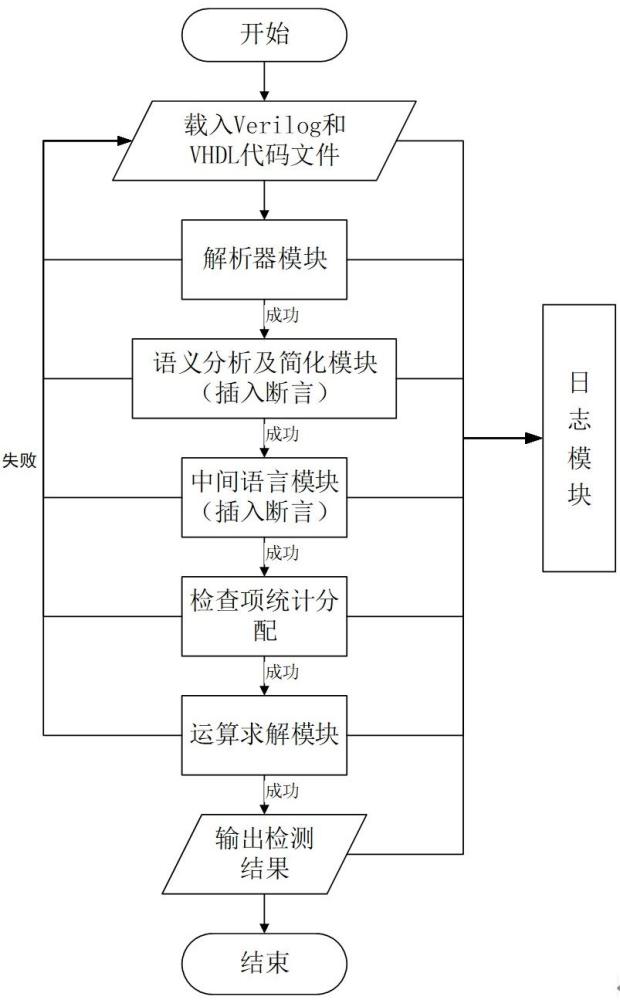

1、为了能够快速、自动、全面地检查rtl代码的结构,使用形式化验证的方法检查代码中的设计缺陷,使设计者可以更早的定位、验证、修复设计中可能存在的问题,加快项目进度,真正提高产品的可靠性。本发明提出了一种基于形式化验证的fpga缺陷检查方法,该方法包括以下步骤:

2、s1. 载入代码文件,其中,所述代码文件为verilog和vhdl;

3、s2.对所述代码文件进行语法分析,生成语法树;并对所述语法树进行优化,扫描所述语法树并插入断言; 例如除零检查,断言生成器会扫描出语法树中所有除法的节点,再对每个节点生成一个除数不等于零的断言,并将断言插入该节点所在位置;

4、s3. 生成中间语言,扫描所述中间语言并插入断言信息;统计出步骤s2生成并插入设计的断言信息,

5、s4. 扫描所述断言信息,生成检查项列表;具体的再通过断言信息生成相应缺陷检查项信息,并将缺陷检查项信息根据缺陷类型和所属模块进行分类标记,生成带有代码信息的待测缺陷检查项列表;

6、s5.动态规划调度运行检查任务,并生成对应任务输入数据、收集任务结果;

7、s6. 根据任务属性生成运算输入数据,进行检查项分析求解运算,生成结果和波形序列文件。

8、进一步的,所述s3中,将所述代码文件转换为rtl中间语言并插入断言,统计生成检查项信息。

9、进一步的,所述s2中,先将所述代码文件进行词法分析,再利用词法分析生成的token符号进行语法分析,生原始成抽象语法树。

10、进一步的,再对所述原始抽象语法树进行优化,其中,将原始抽象语法树中包括的无用信号和器件进行清理,得到优化后的抽象语法树;根据所述优化后的抽象语法树生成中间语言。

11、进一步的,所述生成中间语言过程中,根据断言信息识别出的检查点插入相应断言信息。

12、进一步的,所述插入断言信息的方法包括,

13、对除零检查的插入断言;

14、扫描到语法树中的block3语句块下存包括的一个除法(c=a÷b);

15、分析出除数为b,随即生成一个除数不为零的断言(assert(b != 0));

16、再将其插入到block3语句块下。

17、进一步的,所述s5中,还包括得到配置数据和检查项信息后,所述动态规划调度运行检查任务;其中,

18、将传入检查项按照检查类型和任务属性进行分类,再按计算机处理器荷属进行分组,分组后生成独立的检查任务,为每个分配相应的算法和求解引擎;

19、分配完成后根据计算机cpu使用情况进行任务数量动态规划,对每个任务的运行进行监测,任务完成后收集检测结果和数据。

20、进一步的,所述s6中具体步骤包括,

21、收到分配的检查项后,读入相应的输入数据,提取和分析检查项断言信息;

22、对缺陷检查项生成求解算法;

23、求解引擎根据所述求解算法和所述输入数据进行求解,得到的求解结果经过分析即可得到检查项的检查结果。

24、本发明可用于实现一款基于形式化验证的fpga缺陷检查软件,支持对xilinx \altera\lattice\actel芯片中的rtl代码进行全面深入的缺陷检查。基于形式化验证方法的检查对于静态检查拥有更严格的数学证明、更具体的检查结果、可复现验证的缺陷路径。

技术特征:1.一种基于形式化验证的fpga缺陷检查方法,其特征在于,该方法包括以下步骤:

2.根据权利要求1所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述s3中,将所述代码文件转换为rtl中间语言并插入断言,统计生成检查项信息。

3.根据权利要求1所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述s2中,先将所述代码文件进行词法分析,再利用词法分析生成的token符号进行语法分析,生原始成抽象语法树。

4.根据权利要求3所述的基于形式化验证的fpga缺陷检查方法,其特征在于,再对所述原始抽象语法树进行优化,其中,将原始抽象语法树中包括的无用信号和器件进行清理,得到优化后的抽象语法树;根据所述优化后的抽象语法树生成中间语言。

5.根据权利要求4所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述生成中间语言过程中,根据断言信息识别出的检查点插入相应断言信息。

6.根据权利要求5所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述插入断言信息的方法包括,

7.根据权利要求1所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述s5中,还包括得到配置数据和检查项信息后,所述动态规划调度运行检查任务;其中,

8.根据权利要求7所述的基于形式化验证的fpga缺陷检查方法,其特征在于,所述s6中具体步骤包括,

技术总结本发明公开了一种基于形式化验证的FPGA缺陷检查方法,该方法首先载入Verilog和VHDL代码文件,通过语法语义分析,生成语法树,进行逻辑优化和综合,扫描设计并插入断言,基于形式化验证方法进行缺陷检查,并生成检测结果。本发明可用于实现一款基于形式化验证的FPGA缺陷检查软件,支持对Xilinx\Altera\Lattice\Actel芯片中的RTL代码进行全面深入的缺陷检查。基于形式化验证方法的检查对于静态检查拥有更严格的数学证明、更具体的检查结果、可复现验证的缺陷路径。技术研发人员:周勋受保护的技术使用者:成都迪真计算机科技有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/295450.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表