一种鳍型三相忆阻器单元及其制备方法

- 国知局

- 2024-09-14 14:43:38

本发明涉及三相忆阻器单元制备,具体涉及一种鳍型三相忆阻器单元及其制备方法。

背景技术:

1、阻器被称为第四类基本电子元件,是一个描述磁通量和电荷相关的无源电路元件。早在1971年,蔡少棠从理论上预言了忆阻器的存在。2008年,惠普实验室首次在工业界制造了第一个忆阻器原型器件,证实了蔡少棠对忆阻器的理论预测。忆阻器具备尺寸小、能耗低、速度快和高非线性度的特点,主要应用于存储和处理信息单元、类脑单元以及真随机数发生器、谐振器等领域。近些年来,随着摩尔定律逐渐走到尽头,被认为是发展下一代新型非易失性内存器的理想方案。然而,为了制备出更高集成度且更适配性的忆阻器单元,国内外领域及亟需一种新型忆阻器单元结构。

2、现阶段,本技术领域的研究人员对利用忆阻器单元及阵列已经做了相关研究,这包括利用单元忆阻器,十字交叉阵列忆阻器等结构。其中,对于高密度阵列结构的研究还停留在忆阻器十字交叉阵列的阶段,结构较为单一,神经网络及电路应用适配性低,相对于应用专门的神经网络功能函数及应用电路有较高的适配度和冗余。

3、本发明中,设计一种鳍型的三相忆阻器单元结构,提出了一种小尺寸高密度忆阻器单元结构的设计和制备方案,通过设计一整套的鳍型三相忆阻器单元的工艺方法,形成忆阻器新型复合单元结构,关键的工艺在于通过原子层沉积纳米量级厚度的阻变层薄膜在其侧面,将三相忆阻器单元的各个阻变层垂直制备,通过物理气相沉积蒸镀接触电极并完成忆阻器的片上制备。利用该技术可以制备具备小尺寸高密度三相忆阻器单元结构,本发明提出的硅基工艺方法适合工业化生产,制作成本低,对忆阻器的发展具备一定的推动作用,实现适配神经网络的单元架构,高密度且高适配度的忆阻器基本单元。本发明工艺简单且成本较低,同时对研究忆阻器的电路原理以及基于忆阻器的硬件神经网络有一定的指导意义。

技术实现思路

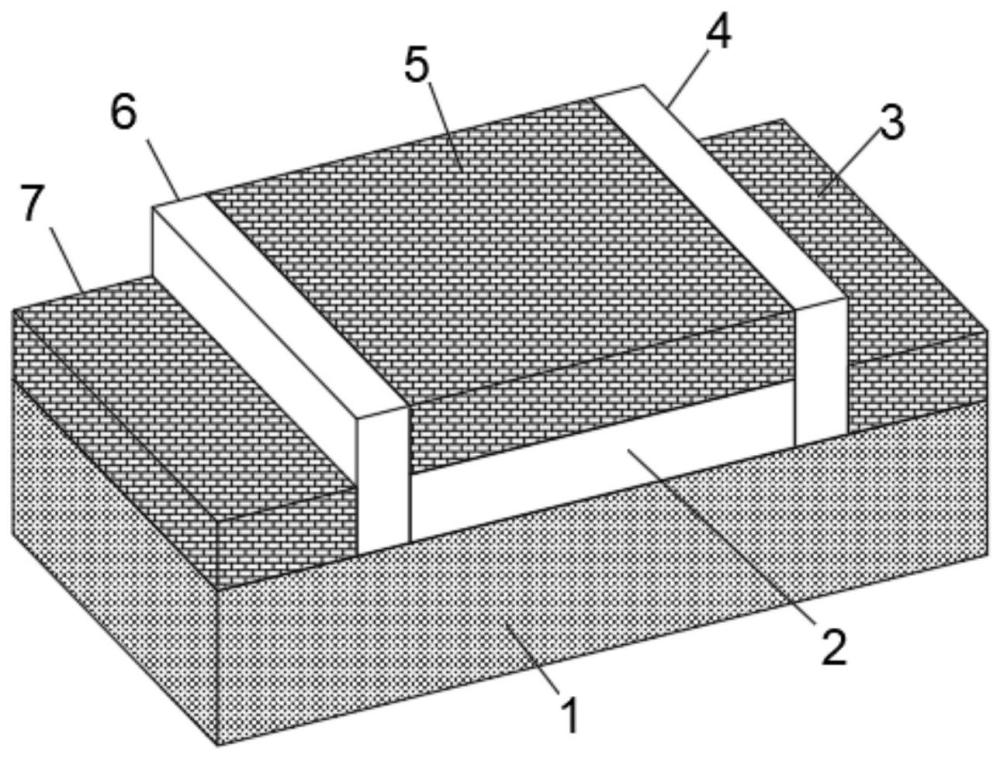

1、针对上述缺陷,本发明所要解决的技术问题在于提供一种鳍型三相忆阻器单元,包括:位于底部的非晶硅衬底、设置在非晶硅衬底顶部上的一号阻变层、以及固定在一号阻变层两侧表面上的二号阻变层和三号阻变层;

2、其中,二号阻变层和三号阻变层相互远离的一侧分别设置有固定在非晶硅衬底顶部表面上的二号忆阻器电极和三号忆阻器电极,且二号阻变层和三号阻变层相互靠近的一侧设置有固定在一号阻变层顶部表面上的一号忆阻器电极。

3、一种鳍型三相忆阻器单元制备方法的技术方案中,优选地,包括有如下的制备流程:

4、s1:对于一号忆阻器电极和一号阻变层的制备:对非晶硅衬底进行20-30分钟紫外光照射后,放置在厚度为360μm的4英寸硅片上,利用磁控溅射在该硅片上溅射一层厚度为80-100nm的忆阻器阻变层;随后在基底4寸硅片表面上一整层惰性金属薄膜作为忆阻器电极,厚度为80-100nm,此处操作不需要掩模版;

5、s2:制备鳍型结构:在s1步骤基础上,刻蚀出附图1形状的鳍型结构,此时为立体鳍型方块形状,立方体尺寸为:5×15×0.2μm(长×宽×高),同时忆阻器电极在鳍型方块的正上方;

6、s3:制备二号阻变层和三号阻变层:在s2步骤基础上,用化学气相沉积的方式,在立方体某一侧面生长忆阻器的阻变层材料如:氧化物、二维材料、过渡金属氧化物等,厚度为3-10nm,此过程中需要掩模版准确遮盖s2步骤中的底电极部分;

7、s4:制备二号忆阻器电极和三号忆阻器电极:在s3步骤基础上,紧密贴合掩模版,掩模版的图形为本发明忆阻器的顶电极图形,厚度为50-80nm,低于s1中一号阻变层的厚度,防止忆阻器单元内部短接;在这一层的制备中,二号忆阻器电极和三号忆阻器电极需要紧密贴合s3中的二号阻变层和三号阻变层,至此完成鳍型三相忆阻器单元的制备。

8、在上述的一种鳍型三相忆阻器单元制备方法的技术方案中,优选地,所述步骤s3中关于二号阻变层和三号阻变层的制备,具体有:将一定形状的掩模版紧密贴合在制备完衬底的硅片上,为了制备出厚度薄且致密的高质量薄膜,采用化学气相沉积的方式。

9、在上述的一种鳍型三相忆阻器单元制备方法的技术方案中,优选地,所述步骤s3中的阻变层的制备中,立方体某一侧面生长忆阻器的阻变层材料如:氧化物、二维材料、过渡金属氧化物等,厚度为3-10nm。

10、在上述的一种鳍型三相忆阻器单元制备方法的技术方案中,优选地,所述鳍型三相忆阻器单元适用于于市面上的半导体分析仪,以及普遍性忆阻器测试探针台,其中采用三通道的smu模块,将smu1设置为ch1通道,smu2设置为ch2通道,smu3设置为ch3通道,分别对应连接探针台的探针1、2和3,半导体参数分析仪输入电压激励信号,两两探针测试均为一个忆阻器,因此构成了三相忆阻器单元。

11、述技术方案可知,本发明提供一种鳍型三相忆阻器单元及其制备方法与现有技术相比,本发明具有以下有益效果:

12、在本发明中,解决了如何将制备鳍型忆阻器单元的工艺技术问题,增加了忆阻器单元的类型;与现有技术生产出来的三明治忆阻器的单元相比成本低、尺寸更小且集成度更高,通过设计并制备鳍型忆阻器单元构建三相忆阻器的设计,实现适配神经网络的单元架构,高密度且高适配度的忆阻器基本单元,发明工艺简单且成本较低,同时对研究忆阻器的电路原理以及基于忆阻器的硬件神经网络有一定的指导意义,适用于忆阻器的电路应用研究以及实现大规模硬件神经网络开发,总体涉及的材料与cmos工艺兼容性强,基本适合于工业化生产。

技术特征:1.一种鳍型三相忆阻器单元,其特征在于,包括有位于底部的非晶硅衬底(1)、设置在非晶硅衬底(1)顶部上的一号阻变层(2)、以及固定在一号阻变层(2)两侧表面上的二号阻变层(4)和三号阻变层(6);

2.一种鳍型三相忆阻器单元制备方法,其特征在于,包括有如下的制备流程:

3.根据权利要求2所述的一种鳍型三相忆阻器单元制备方法,其特征在于,所述步骤s3中关于二号阻变层(4)和三号阻变层(6)的制备,具体有:将一定形状的掩模版紧密贴合在制备完衬底的硅片上,为了制备出厚度薄且致密的高质量薄膜,采用化学气相沉积的方式。

4.根据权利要求2所述的一种鳍型三相忆阻器单元制备方法,其特征在于,所述步骤s3中的阻变层的制备中,立方体某一侧面生长忆阻器的阻变层材料如:氧化物、二维材料、过渡金属氧化物等,厚度为3-10nm。

5.根据权利要求2所述的一种鳍型三相忆阻器单元制备方法,其特征在于,所述鳍型三相忆阻器单元适用于于市面上的半导体分析仪,以及普遍性忆阻器测试探针台,其中采用三通道的smu模块,将smu1设置为ch1通道,smu2设置为ch2通道,smu3设置为ch3通道,分别对应连接探针台的探针1、2和3,半导体参数分析仪输入电压激励信号,两两探针测试均为一个忆阻器,因此构成了三相忆阻器单元。

技术总结本发明公开了一种鳍型三相忆阻器单元及其制备方法,本发明涉及三相忆阻器单元制备技术领域,现提出如下方案,位于底部的非晶硅衬底、设置在非晶硅衬底顶部上的一号阻变层、以及固定在一号阻变层两侧表面上的二号阻变层和三号阻变层;在本发明中,解决了如何将制备鳍型忆阻器单元的工艺技术问题,增加了忆阻器单元的类型;与现有技术生产出来的三明治忆阻器的单元相比成本低、尺寸更小且集成度更高,通过设计并制备鳍型忆阻器单元构建三相忆阻器的设计,实现适配神经网络的单元架构,高密度且高适配度的忆阻器基本单元,适用于忆阻器的电路应用研究以及实现大规模硬件神经网络开发,总体涉及的材料与CMOS工艺兼容性强,基本适合于工业化生产。技术研发人员:黄予,童祎受保护的技术使用者:南京邮电大学技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/295692.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。