一种基于拥塞度的FPGA布局方法及装置与流程

- 国知局

- 2024-09-14 14:42:40

本发明涉及数字集成电路中现场可编程门阵列(fpga)的,尤其涉及一种基于拥塞度的fpga布局方法,以及一种基于拥塞度的fpga布局装置。

背景技术:

1、fpga(field-programmable gate array,现场可编程门阵列)是一种通用的逻辑电路,与cpu,dsp并称为三大通用信号处理器件。

2、当前fpga已经成为数字电路领域一种不可或缺的实现途径,在开发周期和可编程灵活性方面有着明显的优势,其应用领域也日趋广泛,涉及到通信、航天、医疗、数学计算、图像处理、消费产品等诸多领域。fpga cad(computer aided design,计算机辅助设计)流程中,通常都是先布局后布线,布局若不将拥塞度因素考虑进去,将可能会导致布线拥塞,造成布线失败,因此布局上迫切需要一种高效实用的基于拥塞度驱动布局的方法。

技术实现思路

1、为克服现有技术的缺陷,本发明要解决的技术问题是提供了一种基于拥塞度的fpga布局方法,其能够合理调整布局块的位置,使得布线时不会因为信号聚集于一处而造成布线拥塞,避免布线失败,使得信号太分散区域布局能更紧凑,提升性能。

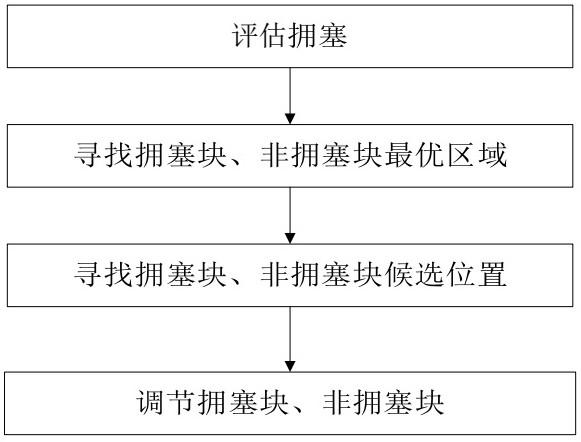

2、本发明的技术方案是:这种基于拥塞度的fpga布局方法,其包括以下步骤:

3、(1)评估拥塞:根据公式(1)评估

4、(1)

5、将fpga板子划分为n个箱子,箱子中包含多个簇,i代表第i个箱子,代表穿过第i个箱子的所有线网,nw为线网的权重,其值与线网m的管脚数量有关,hpwl是线网m的边界框的半周线长,代表线网m在第i个箱子中管脚的数量,代表线网m总的管脚数量,通过所有穿过箱子i的线网在箱子i中的总线长模拟箱子i的拥塞度;

6、(2)寻找拥塞块、非拥塞块最优区域:当块在关键路径上时,以块所在关键路径上的前一个块和后一个块所构成的边界框所在区域作为最优区域;

7、(3)寻找拥塞块、非拥塞块候选位置:对于拥塞块,搜寻其候选位置中的拥塞度小于其自身拥塞度的位置作为候选位置;对于非拥塞块,搜寻其候选位置中的拥塞度大于其自身拥塞度的位置作为候选位置;

8、(4)调节拥塞块、非拥塞块:调节顺序为先拥塞块后非拥塞块,拥塞块根据拥塞度由大到小依次调节,非拥塞块根据拥塞度由小到大依次调节,每个块从候选位置中寻找一个位置进行放置或交换。

9、本发明通过评估拥塞,寻找拥塞块、非拥塞块最优区域,寻找拥塞块、非拥塞块候选位置,调节拥塞块、非拥塞块,从而能够合理调整布局块的位置,使得布线时不会因为信号聚集于一处而造成布线拥塞,避免布线失败,使得信号太分散区域布局能更紧凑,提升性能。

10、还提供了一种基于拥塞度的fpga布局装置,其包括:

11、评估单元,其配置来评估拥塞:根据公式(1)评估

12、(1)

13、将fpga板子划分为n个箱子,箱子中包含多个簇,i代表第i个箱子,代表穿过第i个箱子的所有线网,nw为线网的权重,其值与线网m的管脚数量有关,hpwl是线网m的边界框的半周线长,代表线网m在第i个箱子中管脚的数量,代表线网m总的管脚数量,通过所有穿过箱子i的线网在箱子i中的总线长模拟箱子i的拥塞度;

14、第一寻找单元,其配置来寻找拥塞块、非拥塞块最优区域:当块在关键路径上时,以块所在关键路径上的前一个块和后一个块所构成的边界框所在区域作为最优区域;

15、第二寻找单元,其配置来寻找拥塞块、非拥塞块候选位置:对于拥塞块,搜寻其候选位置中的拥塞度小于其自身拥塞度的位置作为候选位置;对于非拥塞块,搜寻其候选位置中的拥塞度大于其自身拥塞度的位置作为候选位置;

16、调节单元,其配置来调节拥塞块、非拥塞块:调节顺序为先拥塞块后非拥塞块,拥塞块根据拥塞度由大到小依次调节,非拥塞块根据拥塞度由小到大依次调节,每个块从候选位置中寻找一个位置进行放置或交换。

技术特征:1.一种基于拥塞度的fpga布局方法,其特征在于:其包括以下步骤:

2.根据权利要求1所述的基于拥塞度的fpga布局方法,其特征在于:所述步骤(1)中,根据每个块的拥塞度对块进行由大到小排序,取最拥塞的j%的块作为待调节的拥塞区域的块,对最不拥塞的k%的块作为待调节的非拥塞区域的块,j、k是可调节的。

3.根据权利要求2所述的基于拥塞度的fpga布局方法,其特征在于:所述步骤(2)中,当块不在关键路径上时,遍历与块连接的所有线网,并计算它们的边界框,这里的边界框为剔除此块的边界框,对于n个线网,得到边界框的水平集合((1),(1),(2),(2),...(n),(n))和垂直集合((1),(1),(2),(2),...(n),(n))

4.根据权利要求3所述的基于拥塞度的fpga布局方法,其特征在于:所述步骤(3)中,候选位置符合结构建模的合法可用位置,类型与块的类型一致。

5.根据权利要求4所述的基于拥塞度的fpga布局方法,其特征在于:所述步骤(4)中,调节后,根据公式(6)得到,若<0,则保留调节后的结果,否则重新从候选位置中选择位置,直至找到第一个使<0的位置;若整个候选位置未找到使<0的位置,进行下一个块调节;

6.根据权利要求5所述的基于拥塞度的fpga布局方法,其特征在于:所述步骤(4)中,当所有待调节块都调节后,当前轮次调节完成,在每轮次调节过程中记录是否存在<0的情况,若存在则进行下一轮调节,否则结束调节。

7.一种基于拥塞度的fpga布局装置,其特征在于:其包括:

8.根据权利要求7所述的基于拥塞度的fpga布局装置,其特征在于:所述评估单元中,根据每个块的拥塞度对块进行由大到小排序,取最拥塞的j%的块作为待调节的拥塞区域的块,对最不拥塞的k%的块作为待调节的非拥塞区域的块,j、k是可调节的。

9.根据权利要求8所述的基于拥塞度的fpga布局装置,其特征在于:所述第一寻找单元中,当块不在关键路径上时,遍历与块连接的所有线网,并计算它们的边界框,这里的边界框为剔除此块的边界框,对于n个线网,得到边界框的水平集合((1),(1),(2),(2),...(n),(n))和垂直集合((1),(1),(2),(2),...(n),(n))

10.根据权利要求9所述的基于拥塞度的fpga布局装置,其特征在于:所述调节单元中,调节后,根据公式(6)得到,若<0,则保留调节后的结果,否则重新从候选位置中选择位置,直至找到第一个使<0的位置;若整个候选位置未找到使<0的位置,进行下一个块调节;

技术总结一种基于拥塞度的FPGA布局方法及装置,能够合理调整布局块的位置,使得布线时不会因为信号聚集于一处而造成布线拥塞,避免布线失败,使得信号太分散区域布局能更紧凑,提升性能。方法包括:(1)评估拥塞;(2)寻找拥塞块、非拥塞块最优区域;(3)寻找拥塞块、非拥塞块候选位置;(4)调节拥塞块、非拥塞块。技术研发人员:景加慧,刘洋,蔡刚,魏育成受保护的技术使用者:中科亿海微电子科技(苏州)有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/295596.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表