基于分时复用的FPGA多通道DDC实现方法与流程

- 国知局

- 2024-09-14 15:00:48

本发明属于数字信号处理,尤其涉及基于分时复用的fpga多通道ddc实现方法。

背景技术:

1、数字下变频(ddc)是广泛应用于数字无线电接收机中的一种数字信号处理技术。数字下变频指在采集卡中,对adc采集到的中频信号进行混频,得到比中频信号频率更低的信号。

2、数字下变频通常包含数控振荡(nco)模块、混频模块、抽取滤波模块三个模块,其中数控振荡器产生正余弦本振信号,然后分别与输入信号相乘完成混频,最后进行抽取滤波得到输出信号。

3、现有的技术方案是主要是通过adc采集原始中频信号,得到原始采样数据,此时的数据的带宽等于数据的采样率。然后控制nco产生与原始中频信号相同频率的正余弦本振信号,然后分别与采样数据相乘完成混频,得到差频与合频,其中合频会在后续滤波模块中被滤掉,此处会得到差频。

4、由于nco产生的频率与原始中频信号的频率相等,混频后的差频信号频谱会关于原点对称,实现将频谱搬移到基带,可以实现最大抽取比例,最大程度降低信号采样率。

5、混频后的信号数据采样率仍然等于adc的采样频率,此时信号的带宽远小于数据的采样率,所以需要进行抽取滤波。混频后的信号通过抗混叠低通滤波器,然后再经过半带滤波器、fir滤波器进行抽取,完成降采样率。

6、现有的技术方案搭建的ddc流水线在同一时间只能处理一路数据对单个目标频率进行下变频,如果需要在同一时间内对多个目标频率进行下变频,则需要搭建多级流水线,会消耗大量的dsp以及lut资源。

7、但是在ddc流水线中,数据输出的速率远小于数据输入的频率,输出信号的带宽也远小于输入信号的带宽。在对数据进行抽取降采样率的同时,浪费大量的算力。由于数据采样率的降低,在后续的滤波通路中,滤波器绝大多数时间是处于等待数据的状态。在时间轴上,此处的资源利用率极低。

技术实现思路

1、本发明的目的在于,为克服现有技术缺陷,提供了基于分时复用的fpga多通道ddc实现方法,将ddc流水线中,降采样后的滤波通路的空闲时间利用起来,通过分时复用的方法处理多个通道的数据。提高资源的利用率,在消耗相同资源的情况下,实现对多个目标频率进行下变频。

2、本发明目的通过下述技术方案来实现:

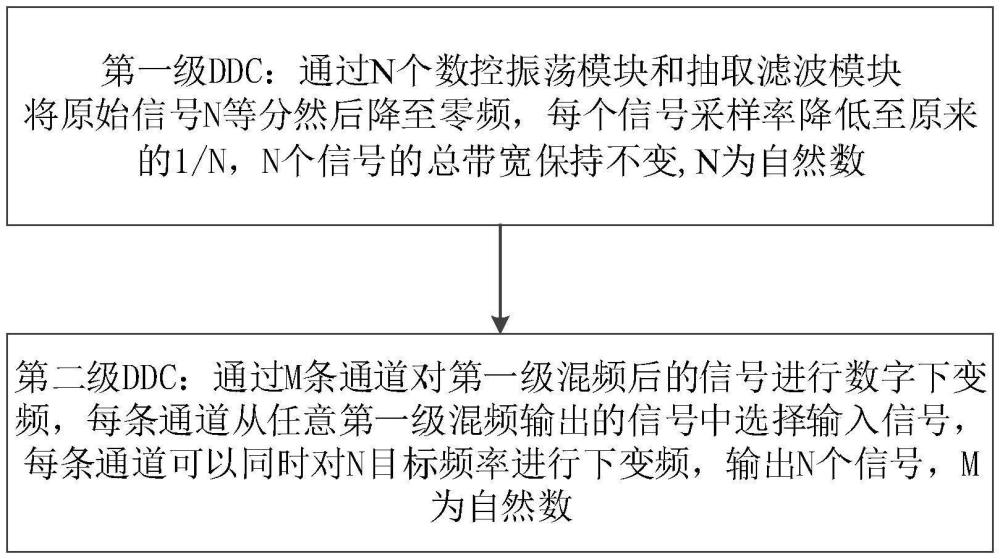

3、一种基于分时复用的fpga多通道ddc实现方法,所述方法包括通过两级混频实现数字下变频,具体包括:

4、第一级ddc:通过n个数控振荡模块和抽取滤波模块将原始信号n等分然后降至零频,每个信号采样率降低至原来的1/n,n个信号的总带宽保持不变,n为自然数;

5、第二级ddc:通过m条通道对第一级混频后的信号进行数字下变频,每条通道从任意第一级混频输出的信号中选择输入信号,每条通道可以同时对n目标频率进行下变频,输出n个信号,m为自然数。

6、进一步的,所述第一级混频具体包括:

7、将adc采样后的数据分别与n个数控振荡模块相乘,将原始频谱n等分,n为数控振荡模块数量,每个数控振荡模块的频率分别为(2n-1)*fs/2n,,n为数控振荡模块序号;

8、将n等分后的频谱搬移至零频,再分别将信号采样率降至信号输入时的1/n。

9、进一步的,所述第二级混频具体包括:

10、从第一级混频输出的n个信号中选择目标频率所在的信号作为输入,通过数控振荡模块和滤波器依次处理每一个通道的数据。

11、进一步的,所述第二级混频还包括:

12、当一个通道的数据处理完成后,将数控振荡模块和滤波器的参数缓存,然后加载下一组工作参数,处理下一个通道的数据。

13、进一步的,所述第一级混频基于第一级混频单元实现,所述第一级混频单元包括n个数控振荡模块和n个低通滤波器,通过低通滤波器将信号采样率降低。

14、进一步的,所述第二级混频基于第二级混频单元实现,所述第二级混频单元依据fpga芯片资源及需求搭建任意数目信号处理通道,第二级混频单元包括m个数控振荡模块和m个滤波器。

15、本发明的有益效果在于:

16、本发明以分时复用的原理,将fpga的nco和滤波器在时间轴上进行复用,以达到利用有限资源搭建更多ddc通道的目的,相较于传统的ddc流水线结构,以相同的资源搭建了远超传统结构的通道数目,资源利用率大幅提升的同时,大幅度降低了对fpga资源的消耗,给fpga后续的功能拓展留下了更多的可能性。

技术特征:1.一种基于分时复用的fpga多通道ddc实现方法,其特征在于,所述方法包括通过两级混频实现数字下变频,具体包括:

2.如权利要求1所述的基于分时复用的fpga多通道ddc实现方法,其特征在于,所述第一级混频具体包括:

3.如权利要求1所述的基于分时复用的fpga多通道ddc实现方法,其特征在于,所述第二级混频具体包括:

4.如权利要求3所述的基于分时复用的fpga多通道ddc实现方法,其特征在于,所述第二级混频还包括:

5.如权利要求2所述的基于分时复用的fpga多通道ddc实现方法,其特征在于,所述第一级混频基于第一级混频单元实现,所述第一级混频单元包括n个数控振荡模块和n个低通滤波器,通过低通滤波器将信号采样率降低。

6.如权利要求3所述的基于分时复用的fpga多通道ddc实现方法,其特征在于,所述第二级混频基于第二级混频单元实现,所述第二级混频单元依据fpga芯片资源及需求搭建任意数目信号处理通道,第二级混频单元包括m个数控振荡模块和m个滤波器。

技术总结本发明公开了基于分时复用的FPGA多通道DDC实现方法,该方法通过第一级DDC将信号的采样率初步降低,在保持第二级DDC工作速率的同时,降低输入信号的速率,实现第二级混频中的数控振荡模块和滤波器的复用。本发明以相同的资源搭建了远超传统结构的通道数目,提高资源的利用率,在消耗相同资源的情况下,实现对多个目标频率进行下变频。技术研发人员:杨涛,刘超受保护的技术使用者:成都众志天成科技有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296670.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表