MCU芯片功能测试集成复用系统及方法与流程

- 国知局

- 2024-09-14 15:14:27

本发明涉及芯片测试,具体涉及一种mcu芯片功能测试集成复用系统及方法。

背景技术:

1、在当前芯片行业迅猛发展的背景下,芯片类型的更新换代速度日益加快。为确保每款芯片成功上市并实现量产,对流片阶段的芯片进行详尽的功能与性能测试显得至关重要。目前市场上已有多种成熟的ate测试产品,这些产品在芯片的批量测试中发挥了显著作用。然而,对于新设计的芯片而言,在流片阶段仅需对少量样本进行功能验证和性能指标测试,以识别潜在缺陷。在这一环节中,ate测试机往往难以充分展现其优势。

2、鉴于上述情况,申请号为cn202311790081.5的发明提出了一种创新的自动测试方法,该方法利用矩阵开关实现控制被测单元信号线的连接。矩阵开关在ate测试机中扮演着至关重要的角色,但其体积庞大,给便携测试系统平台的搭建带来了挑战。此外,矩阵开关的控制方式相对复杂,控制程序较为繁琐,特别是在被测芯片端口设计较多的情况下,矩阵开关的连接问题愈发凸显。

3、因此,本文提出了一种可替代ate测试机在芯片流片阶段进行功能验证的新方案。该方案通过主控芯片控制本系统,实现将芯片引脚连接至对应功能测试的信号线的功能,从而实现对芯片功能的精准验证。这一方案有助于简化测试流程,提高测试效率,并为芯片研发过程中的功能验证提供了更为便捷、高效的解决方案。

技术实现思路

1、针对现有技术的不足,本发明公开了一种mcu芯片功能测试集成复用系统及方法,使用常用的通信协议对系统进行控制,通过fpga的外部引脚连接外部电路,或者在fpga上开发功能测试模块,以此实现外部电路通过fpga进行内部复用互连。

2、本发明通过以下技术方案予以实现:

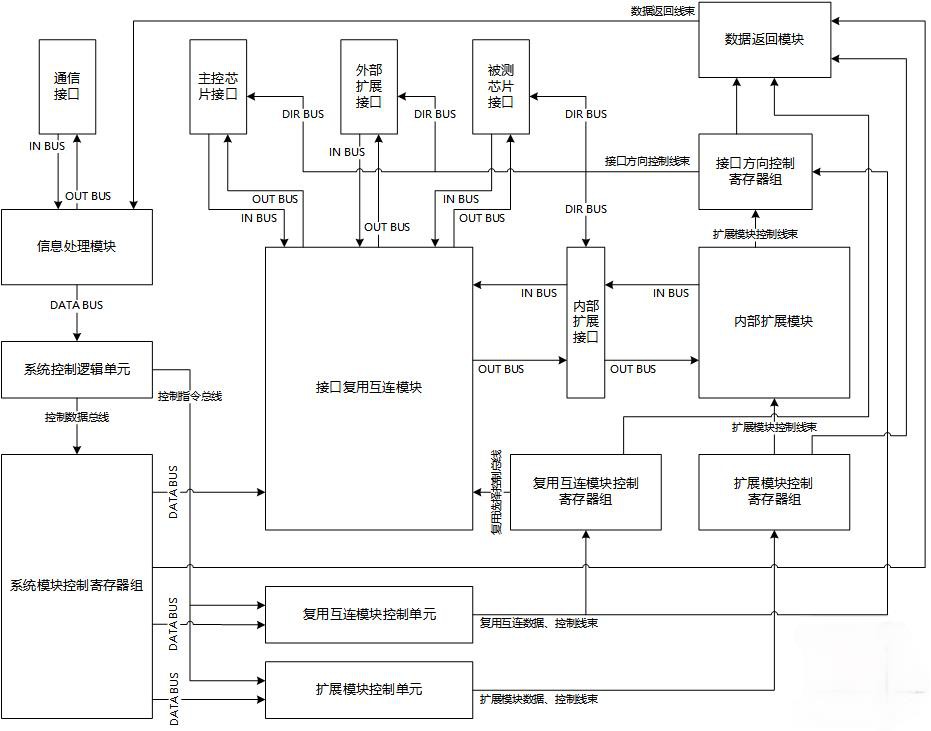

3、第一方面,本发明提供了一种mcu芯片功能测试集成复用系统,包括

4、寄存器组,包括系统模块控制寄存器组、复用互连模块控制寄存器组、扩展模块控制寄存器组、接口方向控制寄存器组,用于控制相对应子模块的动作或线路的连接;

5、接口复用互连模块,集成互连接口模块,并根据所述寄存器组的值实现所述接口模块中各接口之间的复用互连控制;

6、控制模块,通过系统控制逻辑单元依据指令写数据至所述统模块控制寄存器组,并借助所述统模块控制寄存器组组合控制子单元控制模块的逻辑输出;

7、子单元控制模块,接收所述控制模块及系统模块控制寄存器组控制信号,产生对连接的子单元寄存器组的控制信号,进而控制所述寄存器组相对应子模块的动作或线路的连接。

8、更进一步的,所述系统模块控制寄存器组负责同步管理接口复用互连模块、复用互连模块控制单元、扩展模块控制单元以及数据返回模块,其控制权限仅限于系统控制逻辑单元,确保控制的严谨性与权威性。

9、更进一步的,所述子单元控制模块涵盖复用互连模块控制单元与扩展模块控制单元两大组成部分。其中,复用互连模块控制单元,依托系统控制逻辑单元和系统模块控制寄存器组所传递的信号,精准调控复用互连模块控制寄存器组以及接口方向控制寄存器组,确保其正常运作;

10、与此同时,扩展模块控制单元则根据系统控制逻辑单元和系统模块控制寄存器组所发出的信号,对扩展模块控制寄存器组进行精细化的管理与控制,以保障整个系统的稳定运行与高效协作。

11、更进一步的,所述接口模块涵盖了通信接口、主控芯片接口、外部扩展接口、被测芯片接口以及内部扩展接口。具体而言:

12、主控芯片接口、外部扩展接口与被测芯片接口均属外部接口范畴,它们均与fpga的引脚相连,从而实现了外部主控芯片、扩展电路以及被测芯片与集成复用系统的有效连接。

13、内部接口则用于快速接入所开发的扩展模块,确保系统的灵活性与可扩展性。

14、此外,通信接口亦与fpga的引脚相连,并内部连接至信息处理模块,以保障数据传输的可靠性与高效性。

15、更进一步的,信息处理模块负责信息的接收、发送以及对接收到的信息进行处理,它与通信接口、系统控制逻辑单元以及数据返回模块紧密相连。当接收到信息时,信息处理模块会对其进行解码处理,并将解码后的信息传输至系统控制逻辑单元进行进一步的处理。对于需要发送的信息,信息处理模块会从数据返回模块接收相关信息,进行编码后,再将编码后的信息发送给外部设备或系统。这一模块在整个信息交互过程中起到了关键的桥梁作用,确保了信息的准确传输与高效处理。

16、更进一步的,所述集成复用系统还涵盖一个系统通信模块,该模块与信息处理模块实现有效连接。系统通信模块负责从外部接收数据,并将其存储至信息处理模块中,确保数据的完整性与准确性。同时,系统通信模块亦能从信息处理模块中读取需要发送的数据,以满足系统内部及外部通信的需求,实现数据的顺畅传输与共享。

17、更进一步的,所述系统通信模块在接收到完整的16位外部数据后,将发出接收完成信号,随后数据将在in bus的数据位上进行传输。一旦接收到准备发送信号,通信模块将从out bus的数据位上读取数据,并将其加载至发送数据移位寄存器中,进而将数据发送至外部设备。

18、更进一步的,所述集成复用系统亦涵盖一数据返回模块,该模块依据所接收到的指令,自寄存器组中精准地获取对应数据,并将其传输至信息处理模块,以完成数据处理的连贯性与准确性。

19、更进一步的,所述集成复用系统,尚包含内部扩展模块。此内部扩展模块旨在根据实际需求,针对性地开发对应的功能测试激励产生模块。该模块通过内部扩展接口,实现与接口复用互联模块的紧密连接,从而确保系统功能的全面覆盖与高效运作。

20、第二方面,本发明提供了一种mcu芯片功能测试集成复用方法,所述方法使用第一方面所述的mcu芯片功能测试集成复用系统,包括以下步骤:

21、s1:检测并接收外部信息,随即启动流程对接收到的信号进行解码处理,输出解码数据;

22、s2:对解码数据进行判断,若判定为有效数据,则进入下一步s3;若判定为无效数据,则将错误代码记录至信息处理模块的发送缓冲区,并返回至步骤s1重新执行;

23、s3:进一步判断解码数据中是否包含控制状态信息,若不存在控制状态,则直接进入步骤s4;若存在控制状态,则对寄存器是否符合既定规则进行判断,若符合规则,则根据寄存器地址写入相应数据,并进入步骤s5;若不符合规则,则将失败代码传送至信息处理模块,并返回至步骤s1重新执行;

24、s4:对解码数据判断其是否为查询寄存器指令,若判定为否,则存储当前控制状态及相关数据;若判定为是,则对寄存器是否符合既定规则进行判断,若符合规则,则进入步骤s5;若不符合规则,则将失败代码传送至信息处理模块,并返回至步骤s1重新执行;

25、s5:通过数据返回模块,将寄存器数据传送至信息处理模块,并启动数据发送流程。

26、本发明的有益效果为:

27、本发明设计精巧,只需一颗fpga芯片即可构建完整系统架构,具有出色的可移植性,可轻松适应不同mcu芯片测试板,实现快速移植。开发方面,采用verilog语言进行开发,无需复杂修改外部电路,提高开发效率。

28、此外,本发明预留丰富扩展接口,用户可根据需求设计新增扩展模块,并通过接口快速接入系统,增强系统扩展性和灵活性。使用便捷,无需特定操作环境,可接受外部主控控制,简化测试流程。

29、本发明还能返回内部控制信息,实时观察已写入的控制信息,校验准确性,确保测试可靠性。应用上,简化对流片芯片测试板绘制过程,优化不同测试项线路连接,减少繁琐重复工作。规范被测芯片测试程序,降低开发成本。

30、同时,本发明极大便利被测芯片覆盖性测试程序开发。通过扩展,实现通信模块快速测试,给出测试信号,全面快速测试被测芯片数字功能。方便测试外围扩展,实现测试结果可视化显示,提升测试直观性和便捷性。

本文地址:https://www.jishuxx.com/zhuanli/20240914/297487.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表