运算放大器电路的制作方法

- 国知局

- 2024-10-09 15:53:12

本公开涉及集成电路设计,尤其涉及一种运算放大器电路。

背景技术:

1、在高精度的电路系统中,对运放指标有着严格的要求,其中比较关键的指标就是直流增益和失调电压。

2、传统运算放大器电路一般由两级运放组成,第一级运放提供大部分增益,第二级运放主要提供驱动能力,并在第一级运放的基础上进一步提供增益,最终可以提供80-120db(分贝)的直流增益。传统运算放大器电路的失调电压主要由第一级运放的mos管(金属-氧化物半导体场效应晶体管)的尺寸决定,失调电压往往在mv(毫伏)级别。

3、在高精度的电路系统中,往往需要更高的直流增益或uv(微伏)级别的失调电压,而传统的运算放大器电路难以达到标准。

技术实现思路

1、本公开要解决的技术问题是为了克服现有技术中运算放大器电路无法达到预设失调电压的缺陷,提供一种运算放大器电路。

2、本公开是通过下述技术方案来解决上述技术问题:

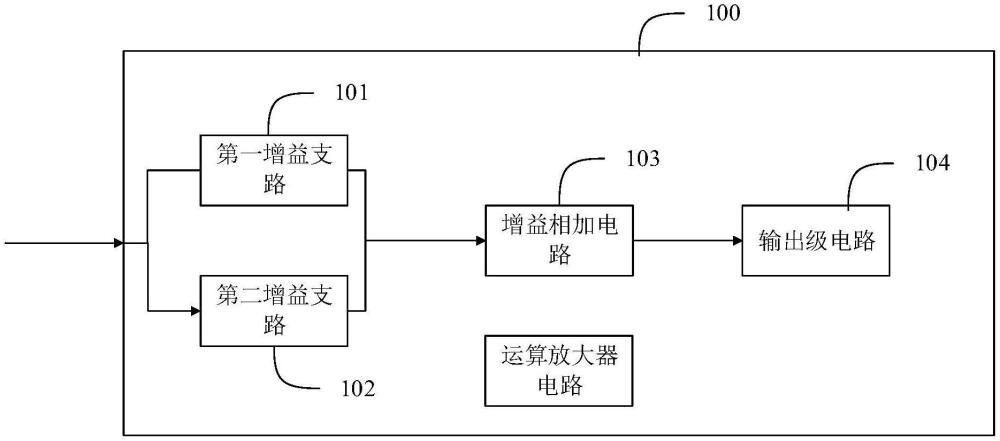

3、根据本公开的第一方面,提供了一种运算放大器电路,所述运算放大器电路包括依次电连接的增益支路、增益相加电路和输出级电路;其中,所述增益支路以及所述增益相加电路具有不同增益;

4、所述增益支路的输入端分别连接所述运算放大器电路的输入端;

5、所述增益相加电路用于将各个所述增益支路的输出信号相加,并输出至所述输出级电路。

6、较佳地,所述运算放大器电路包括并联连接的第一增益支路和第二增益支路;

7、所述第一增益支路包括第一放大模块和第二放大模块;

8、所述第二增益支路包括第三放大模块;

9、所述第一增益支路的输出端与所述第二增益支路的输出端分别连接所述增益相加电路。

10、较佳地,所述第一增益支路还包括第一斩波器和第二斩波器;

11、所述第一斩波器设于所述第一增益支路的输入端与所述第一放大模块之间;

12、所述第二斩波器设于所述第一放大模块与所述第二放大模块之间。

13、较佳地,所述第一增益支路还包括预设滤波器,所述预设滤波器设于所述第二斩波器与所述第二放大模块之间,所述预设滤波器用于对所述第二斩波器的输出信号进行滤波。

14、较佳地,所述第一放大模块包括:第一nmos管(n-channel-oxide-semiconductor,n沟道金属-氧化物-半导体)、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第一pmos管(p-channel-oxide-semiconductor,p沟道金属-氧化物-半导体)、第二pmos管、第三pmos管、第四pmos管、第一放大器以及第二放大器;

15、所述第一nmos管的栅极与第一输入端相连接,所以第一nmos管的漏极与所述第一放大器电连接,所述第一nmos管的源极与所述第五nmos管的漏极电连接;

16、所述第二nmos管的栅极与第二输入端相连接,所以第二nmos管的漏极与所述第一放大器电连接,所述第二nmos管的源极与所述第五nmos管的漏极电连接;

17、所述第三nmos管的栅极与所述第一放大器电连接,所以第三nmos管的漏极与第一输出端相连接,所述第三nmos管的源极与所述第一nmos管的漏极电连接;

18、所述第四nmos管的栅极与所述第一放大器电连接,所以第四nmos管的漏极与第二输出端相连接,所述第四nmos管的源极与所述第二nmos管的漏极电连接;

19、所述第五nmos管的栅极与外部电源电连接,所述第五nmos管的漏极与所述第二nmos管的源极电连接,所述第五nmos管的源极接地;

20、所述第一pmos管的栅极与所述第二放大器电连接,所述第一pmos管的源极与所述第三pmos管的漏极电连接,所述第一pmos管的漏极与所述第一输出端相连接;

21、所述第二pmos管的栅极与所述第二放大器电连接,所述第二pmos管的源极与所述第四pmos管的漏极电连接,所述第二pmos管的漏极与所述第二输出端相连接;

22、所述第三pmos管的栅极与第一电压电连接,所述第三pmos管的源极与电源电压电连接,所述第三pmos管的漏极与所述第二放大器电连接;

23、所述第四pmos管的栅极与所述第一电压电连接,所述第四pmos管的源极与所述电源电压电连接,所述第四pmos管的漏极与所述第二放大器电连接。

24、较佳地,所述增益相加电路包括:第六nmos管、第七nmos管、第八nmos管、第九nmos管、第十nmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第九pmos管以及共模反馈单元;

25、其中,所述第六nmos管的栅极与第二电压电连接,所述第六nmos管的漏极与所述共模反馈单元电连接,所述第六nmos管的源极与所述第八nmos管的漏极电连接;

26、所述第七nmos管的栅极与所述第二电压电连接,所述第七nmos管的漏极与所述第二输出端相连接,所述第七nmos管的源极与所述第九nmos管的漏极电连接;

27、所述第八nmos管的栅极与第三电压电连接,所述第八nmos管的漏极与所述第六nmos管的源极电连接,所述第八nmos管的源极接地;

28、所述第九nmos管的栅极与所述第三电压电连接,所述第九nmos管的漏极与所述第七nmos管的源极电连接,所述第九nmos管的源极接地;

29、所述第十nmos管的栅极与第四电压电连接,所述第十nmos管的漏极与所述第一输出端相连接,所述第十nmos管的源极与所述第七nmos管的漏极电连接;

30、所述第五pmos管的栅极与所述第五电压电连接,所述第五pmos管的源极与所述第一输出端相连接,所述第五pmos管的漏极与所述第七nmos管的漏极电连接;

31、所述第六pmos管的栅极与第六电压电连接,所述第六pmos管的源极与所述第八pmos管的漏极电连接,所述第六pmos管的漏极与所述第六nmos管的漏极电连接;

32、所述第七pmos管的栅极与所述第六电压电连接,所述第七pmos管的源极与所述第九pmos管的漏极电连接,所述第七pmos管的漏极与所述第五pmos管的源极电连接;

33、所述第八pmos管的栅极与所述共模反馈单元的输出端电连接,所述第八pmos管的源极与所述电源电压电连接,所述第八pmos管的漏极与所述第六pmos管的源极电连接;

34、所述第九pmos管的栅极与所述共模反馈单元的输出端电连接,所述第九pmos管的源极与所述电源电压电连接,所述第九pmos管的漏极与所述第七pmos管的源极电连接。

35、较佳地,所述第二放大模块包括:第十pmos管以及第十一pmos管;

36、其中,所述第十pmos管的栅极与第一正输入端相连接,所述第十pmos管的源极与第一电流源电连接,所述第十pmos管的漏极与所述第八nmos管的漏极电连接;

37、所述第十一pmos管的栅极与第一负输入端相连接,所述第十一pmos管的源极与所述第一电流源电连接,所述第十一pmos管的漏极与所述第九nmos管的漏极电连接。

38、较佳地,所述第三放大模块包括:第十二pmos管以及第十三pmos管;

39、其中,所述第十二pmos管的栅极与第二正输入端相连接,所述第十二pmos管的源极与第二电流源电连接,所述第十二pmos管的漏极与所述第八nmos管的源极电连接;

40、所述第十三pmos管的栅极与第二负输入端相连接,所述第十三pmos管的源极与所述第二电流源电连接,所述第十三pmos管的漏极与所述第九nmos管的源极电连接。

41、较佳地,所述运算放大器电路还包括:

42、第一补偿电容,所述第一补偿电容的输入端设于所述第二斩波器与所述预设滤波器之间,所述第一补偿电容的输出端连接所述输出级电路的输出端;

43、和/或,

44、第二补偿电容,所述第二补偿电容的输入端连接所述输出级电路的输入端,所述第二补偿电容的输出端连接所述输出级电路的输出端。

45、较佳地,所述运算放大器电路还包括:

46、第三补偿电容,所述第三补偿电容的输入端设于所述预设滤波器与所述第二放大模块之间,所述第三补偿电容的输出端连接所述输出级电路的输出端。

47、在符合本领域常识的基础上,上述各优选条件,可任意组合,即得本公开各较佳实例。

48、本公开的积极进步效果在于:

49、本公开所提供的运算放大器电路包括具有不同增益的增益支路,采用不同增益的增益支路对运算放大器电路的输入信号进行增益,并通过增益相加电路将各个增益支路的输出信号相加,使得运算放大器电路不仅可以通过其中一条支路实现高增益、低漂移,还可以通过另一条支路实现低增益、高速输出,同时还可提高运放响应速度。

本文地址:https://www.jishuxx.com/zhuanli/20240929/310629.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表