电压调节电路和方法、运算系统、集成模块和电路与流程

- 国知局

- 2024-08-22 14:48:29

本技术涉及集成电路,尤其涉及一种电压调节电路和方法、运算系统、集成模块和电路。

背景技术:

1、随着半导体工艺朝着深亚微米发展,半导体器件的逻辑运算速度也随之逐渐提升。根据工艺角(process corner)类型的不同,可以将半导体器件分为快快角(fast fastcorner,ff corner)器件、慢慢角(slow slow corner,ss corner)器件和典型典型角(typical typical corner,tt corner)器件。其中,tt corner器件为标准的半导体器件。相较于tt corner器件,ff corner器件的时延较小,逻辑运算速度较快,而ss corner器件的时延较大,逻辑运算速度较慢。

2、在多个半导体器件的基础上,可以进一步形成逻辑电路。其中,逻辑电路的工艺角类型也可以分为tt corner、ff corner和ss corner,可以认为,逻辑电路中的多个半导体器件的工艺角类型与该逻辑电路的工艺角类型相同。

3、一般来说,在标准温度且逻辑电路的工作时序固定的情况下,tt corner的逻辑电路可以具有足够的时序裕度,但ss corner的逻辑电路和ff corner的逻辑电路却可能出现时序裕度不足的问题。

技术实现思路

1、本技术提供一种电压调节电路和方法、运算系统、集成模块和电路,用于优化sscorner的逻辑电路和ff corner的逻辑电路的时序裕度。

2、第一方面,本技术实施例提供一种电压调节电路,其主要包括振荡器和调控电路。其中,振荡器连接电源电路,该电源电路的输出电压用于为逻辑电路供电,该振荡器的工艺角类型与逻辑电路的工艺角类型相同。振荡器可以根据电源电路的输出电压生成第一时钟信号。调控电路可以根据上述第一时钟信号控制电源电路调节输出电压。

3、本技术实施例中,振荡器可以根据电源电路的输出电压生成第一时钟信号,且,振荡器具有与逻辑电路相同的工艺角类型。可以理解,振荡器的工艺角类型也会对第一时钟信号产生影响,使得不同工艺角类型的振荡器所输出的第一时钟信号也会存在些许不同。例如,在电源电路的输出电压相同的情况下,对于tt corner的振荡器,其可以输出标准频率的第一时钟信号。对于ss corner的振荡器,其输出的第一时钟信号的频率较低。对于ffcorner的振荡器,其输出的第一时钟信号的频率较高。

4、因此,调控电路可以根据第一时钟信号区分出不同工艺角类型的逻辑电路,进而可以控制电源电路适应性调节输出电压。例如,当第一时钟信号的频率较低时,意味着逻辑电路为ss corner,因此调控电路可以控制电源电路增大输出电压,从而加快逻辑电路的逻辑运算速度,优化逻辑电路的时序裕度。又例如,当第一时钟信号的频率较高时,意味着逻辑电路为ff corner,调控电路可以控制电源电路降低输出电压,从而降低逻辑电路的逻辑运算速度,优化逻辑电路的时序裕度。

5、此外,目前设计逻辑电路的工作时序时,为了增大ss corner的逻辑电路和ffcorner的逻辑电路的时序裕度,往往需要降低逻辑电路的工作频率,以延长setup时间或hold时间,也就是说,目前逻辑电路的工作频率往往达不到其最佳的工作频率。而采用本技术实施例所提供的电压调节电路,可以使逻辑电路表现出tt corner的时序特性,无需降低逻辑电路的工作频率,从而有利于提高逻辑电路的逻辑运算速度。

6、而且,目前设计逻辑电路的工作时序时,电源电路的输出电压不变,不同工艺角类型、不同工作频率的逻辑电路均工作在同一电压下,因此需要电源电路保留一定的电压裕度。特别是在ff corner的情况下,电源电路的输出电压会存在很大程度的浪费。而在本技术实施例中,通过电压调节电路为逻辑电路匹配电源电路的输出电压,无需保留电压裕度,因此还有利于进一步降低逻辑电路的功耗。

7、本技术实施例并不限制振荡器的具体结构。示例性的,振荡器可以包括第一路径,该第一路径的时延与逻辑电路的第二路径的时延正相关。在此情况下,振荡器可以根据电源电路的输出电压,通过上述第一路径生成第一时钟信号。

8、在一种可能的实现方式中,第二路径可以是逻辑电路中的任一逻辑路径。

9、在另一种可能的实现方式中,第二路径可以是逻辑电路中时序裕度最小的逻辑路径,也可以称为关键时序路径,或时序关键路径。在此情况下,振荡器中的第一路径的时延与第二路径的时延可以为线性正相关,第一路径可以追随第二路径的时延变化程度。采用该实现方式,可以使ss corner的逻辑电路和ff corner的逻辑电路中,第二路径(关键时序路径)能够表现出tt corner的时序特性。由于第二路径的时序裕度决定了逻辑电路整体上能否正常工作,因此第一路径与第二路径线性正相关,有利于在最大程度上优化逻辑电路的时序裕度,提高逻辑电路的稳定性。

10、示例性的,本技术实施例所提供的振荡器中,第一路径可以包括串联的多个第一门电路,该多个串联的第一门电路可以使第一路径的时延与第二路径的时延线性正相关。具体来说,每个第一门电路会产生一定的时延,串联的多个第一门电路的时延累积,便可以使第一路径的时延与第二路径的时延线性正相关。

11、更进一步的,第一路径中的每一个第一门电路都对应第二路径中的至少一个第二门电路,对应的第一门电路和至少一个第二门电路之间的功能类型相同,且阈值电压类型相同。其中,门电路的功能类型是根据标准单元划分的,一般来说,可以分为与门、或门、非门等等。在本技术实施例中,功能类型相同的第一门电路和第二门电路具有相同的阈值电压类型。具体来说,门电路的阈值电压类型至少可以分为以下几种:超高阈值电压、标准阈值电压、低阈值电压或超低阈值电压。采用该实现方式,可以使第一路径的时延与第二路径的时延保持更加精确的线性正相关关系,有利于进一步提高对逻辑电路的时序裕度的优化效果。

12、为了进一步扩大振荡器的适用范围,在本技术实施例中,振荡器还可以根据接收到的配置信息,将振荡器中的多个门电路中的部分或全部配置为第一路径中的上述多个第一门电路。振荡器根据配置信息,灵活配置第一路径中的多个第一门电路,进而可以灵活调节第一路径的时延,因此,即使不同场景下逻辑电路中第二路径的结构出现变化,振荡器可以保持第一路径与第二路径之间的匹配(线性正相关),使电压调节电路能够适配多种场景下的逻辑电路。

13、示例性的,本技术实施例中振荡器至少存在以下两种可能的结构:

14、结构一:振荡器中的多个门电路构成第一串联结构,振荡器还包括第一选择器和补充反相器;其中,第一串联结构可以包括多个时延电路,每个时延电路包括一个或多个门电路,每个时延电路的输入信号和输出信号相位相同,且每个时延电路的输出端皆与第一选择器的数据输入端连接,第一串联结构的输入端与补充反相器的输出端连接,第一选择器的输出端与补充反相器的输入端连接。第一选择器可以根据接收到的第一配置信息输出第一中间信号,其中,第一配置信息可以指示上述多个时延电路中的目标时延电路,该第一中间信号可以是该目标时延电路的输出信号,其中,从第一串联结构的输入端至目标时延电路的输出端之间的门电路为上述多个第一门电路;补充反相器,可以接收第一中间信号,根据第一中间信号输出第一时钟信号。

15、可以理解,第一路径所构成的振荡回路中需要包括奇数个门电路才能实现振荡器功能。因此,本技术实施例中,每个时延电路的输入信号和输出信号相位相同,因此从相位变化的角度可以将每个时延电路皆等效为偶数个门电路,在此情况下,无论第一配置信息指示任一时延电路为目标时延电路,第一路径中第一门电路的数量皆等效为偶数个反相器。又由于补充反相器的存在,因此可以使第一路径所构成的振荡回路中始终保持奇数个反相器,以确保振荡器功能的实现。

16、结构二:所述多个门电路中的一部分门电路构成第二串联结构,所述多个门电路中的另一部分门电路构成第三串联结构,振荡器还可以包括第二选择器、第三选择器和补充反相器;其中,第二串联结构可以包括多个低负载时延电路,每个低负载时延电路包括一个或多个门电路,每个低负载时延电路的输入信号和输出信号相位相同,且每个低负载时延电路的输出端皆与第二选择器的数据输入端连接,第二串联结构的输入端与补充反相器的输出端连接;第三串联结构可以包括多个高负载时延电路,每个高负载时延电路包括一个或多个门电路,每个高负载时延电路的输入信号和输出信号相位相同,且每个高负载时延电路的输出端皆与第三选择器的数据输入端连接,第三串联结构的输入端与第二选择器连接。

17、第二选择器可以根据接收到的第二配置信息输出第二中间信号,该第二配置信息可以指示上述多个低负载时延电路中的目标低负载时延电路,该第二中间信号可以是上述目标低负载时延电路的输出信号,其中,从第二串联结构的输入端至目标低负载时延电路的输出端之间的门电路为上述多个第一时延电路中的一部分第一时延电路;第三选择器可以根据接收到的第三配置信息输出第三中间信号,该第三配置信息可以指示上述多个高负载时延电路中的目标高负载时延电路,该第三中间信号可以是上述目标高负载时延电路的输出信号,其中,从第三串联结构的输入端至目标高负载时延电路的输出端之间的门电路可以是上述多个第一时延电路中的另一部分第一时延电路;补充反相器可以接收第三中间信号,根据第三中间信号输出第一时钟信号。

18、示例性的,上述高负载时延电路还可以包括至少一个负载走线。该负载走线,可以理解为串联有负载的连线,也可以理解为走线长度达到一定阈值的连线。例如,逻辑电路中,出于线路布局等方面的考虑,部分逻辑路径中的走线长度过长,从而带来较大的负载,增加了逻辑路径的时延。有鉴于此,本技术实施例中可以根据逻辑电路中第二路径的负载情况灵活配置低负载时延电路的数量和高负载时延电路的数量,以保持第一路径与第二路径之间的时延匹配。

19、本技术实施例中,调控电路可以包括分频器、频率比较器和控制器,且分频器分别与振荡器和频率比较器连接,频率比较器与控制器连接,控制器可以与电源电路连接。其中,分频器可以按照分频倍数对第一时钟信号进行分频,得到第二时钟信号;频率比较器可以接收参考时钟信号,根据上述第二时钟信号和该参考时钟信号输出频率差异信号,该频率差异信号可以指示第二时钟信号与参考时钟信号之间的相对频率大小关系;控制器可以根据上述频率差异信号,控制电源电路调节输出电压。

20、示例性的,对于tt corner类型的振荡器,其输出的第一时钟信号的频率,除以参考时钟信号的频率后的商值,为上述分频倍数。需要指出的是,温度也可能会对振荡器的时延产生些许影响,因此本技术实施例特指在标准温度下,第一时钟信号的频率,除以参考时钟信号的频率后的商值,为上述分频倍数。

21、控制器在根据上述频率差异信号,控制电源电路调节输出电压时,具体可以:在频率差异信号指示第二时钟信号的频率大于参考时钟信号的频率时,控制电源电路降低输出电压;或,在频率差异信号指示第二时钟信号的频率小于参考时钟信号的频率时,控制电源电路增大输出电压。

22、为了进一步提高控制器的准确性,本技术实施例中,调控电路还可以包括低通滤波器,该低通滤波器的输入端与频率比较器连接,低通滤波器的输出端与控制器连接;低通滤波器可以对所述频率差异信号进行滤波,并将滤波后的频率差异信号输出给控制器。经低通滤波器滤波后,可以提高频率差异信号的信号质量,从而有利于提高控制器的准确性。

23、第二方面,本技术实施例提供一种电压调节电路,该电压调节电路不仅可以调节电源电路的输出电压,还具有较大的适用范围,第二方面中相应方案的技术效果可以参照第一方面中对应方案可以得到的技术效果,重复之处不予详述。

24、示例性的,该电压调节电路主要包括振荡器和调控电路;其中,所述振荡器包括第一路径,振荡器可以根据接收到的配置信息,将第一路径中的多个门电路配置为多个第一门电路,该多个第一门电路用于使所述第一路径的时延与逻辑电路中第二路径的时延线性正相关;

25、振荡器,还可以连接电源电路,根据电源电路的输出电压通过第一路径生成第一时钟信号,该电源电路的输出电压用于为逻辑电路供电,该振荡器的工艺角类型与逻辑电路的工艺角类型相同;

26、调控电路,可以根据第一时钟信号控制电源电路调节输出电压。

27、在一种可能的实现方式中,第二路径可以是逻辑电路中的任一逻辑路径。

28、在另一种可能的实现方式中,第二路径可以是逻辑电路中时序裕度最小的逻辑路径,也可以称为关键时序路径,或时序关键路径。

29、示例性的,针对第一路径中的任一第一门电路,在第二路径中存在与该第一门电路功能类型相同的第二门电路,且该第一门电路具有与该第二门电路相同的阈值电压类型。示例性的,所述第一门电路的阈值电压类型为以下任一种阈值电压类型:超高阈值电压uhvt、高阈值电压hvt、标准阈值电压svt、低阈值电压lvt或超低阈值电压ulvt。

30、本技术实施例中,振荡器至少存在以下两种可能的结构:

31、结构一:振荡器中的多个门电路构成第一串联结构。振荡器还包括第一选择器和补充反相器;其中,第一串联结构可以包括的多个时延电路,每个时延电路包括一个或多个门电路,每个时延电路的输入信号和输出信号相位相同,且每个时延电路的输出端皆与第一选择器的数据输入端连接,第一串联结构的输入端与补充反相器的输出端连接,第一选择器的输出端与补充反相器的输入端连接。第一选择器可以根据接收到的第一配置信息输出第一中间信号,其中,第一配置信息可以指示多个时延电路中的目标时延电路,该第一中间信号可以是上述目标时延电路的输出信号,其中,从第一串联结构的输入端至目标时延电路的输出端之间的门电路为上述多个第一门电路;补充反相器,可以接收第一中间信号,根据第一中间信号输出第一时钟信号。

32、结构二:振荡器的多个门电路中的一部分门电路构成第二串联结构,多个门电路中的另一部分门电路构成第三串联结构,振荡器还可以包括第二选择器、第三选择器和补充反相器;其中,第二串联结构可以包括多个低负载时延电路,每个低负载时延包括一个或多个门电路,每个低负载的输入信号和输出信号相位相同,且每个低负载时延电路的输出端皆与第二选择器的数据输入端连接,第二串联结构的输入端与补充反相器的输出端连接;第三串联结构可以包括多个高负载时延电路,每个高负载时延包括一个或多个门电路,每个高负载的输入信号和输出信号相位相同,且每个高负载时延电路的输出端皆与第三选择器的数据输入端连接,第三串联结构的输入端与第二选择器连接。第二选择器可以根据接收到的第二配置信息输出第二中间信号,其中,第二配置信息可以指示上述多个低负载时延电路中的目标低负载时延电路,该第二中间信号可以是上述目标低负载时延电路的输出信号,其中,从第二串联结构的输入端至目标低负载时延电路的输出端之间的门电路为上述多个第一时延电路中的一部分第一时延电路;第三选择器可以根据接收到的第三配置信息输出第三中间信号,其中,第三配置信息可以指示上述多个高负载时延电路中的目标高负载时延电路,该第三中间信号可以是上述目标高负载时延电路的输出信号,其中,从第三串联结构的输入端至目标高负载时延电路的输出端之间的门电路可以是上述多个第一时延电路中的另一部分第一时延电路;补充反相器可以接收第三中间信号,根据第三中间信号输出第一时钟信号。

33、示例性的,上述高负载时延电路还可以包括至少一个负载走线。

34、本技术实施例中,调控电路可以包括分频器、频率比较器和控制器,且分频器分别与振荡器和频率比较器连接,频率比较器与控制器连接,控制器可以与电源电路连接。其中,分频器可以按照分频倍数对第一时钟信号进行分频,得到第二时钟信号;频率比较器可以接收参考时钟信号,根据上述第二时钟信号和该参考时钟信号输出频率差异信号,该频率差异信号可以指示第二时钟信号与参考时钟信号之间的相对频率大小关系;控制器可以根据上述频率差异信号控制电源电路调节输出电压。

35、示例性的,对于tt corner类型的振荡器,其输出的第一时钟信号的频率,除以参考时钟信号的频率后的商值,为上述分频倍数。

36、控制器在根据上述频率差异信号,控制电源电路调节输出电压时,具体可以:在频率差异信号指示第二时钟信号的频率大于参考时钟信号的频率时,控制电源电路降低输出电压;或,在频率差异信号指示第二时钟信号的频率小于参考时钟信号的频率时,控制电源电路增大输出电压。

37、为了进一步提高控制器的准确性,本技术实施例中,调控电路还可以包括低通滤波器,该低通滤波器的输入端与频率比较器连接,低通滤波器的输出端与控制器连接;低通滤波器可以对所述频率差异信号进行滤波,并将滤波后的频率差异信号输出给控制器。经低通滤波器滤波后,可以提高频率差异信号的信号质量,从而有利于提高控制器的准确性。

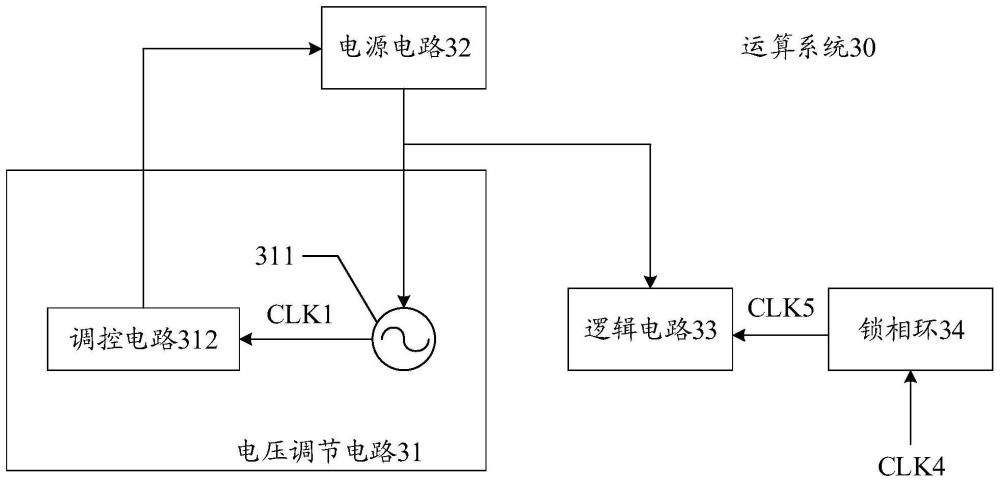

38、第三方面,本技术实施例提供一种运算系统,该运算系统可以包括电源电路、逻辑电路和如上述第一方面或第二方面中任一项所提供的电压调节电路。第三方面中相应方案的技术效果可以参照第一方面中对应方案可以得到的技术效果,重复之处不予详述。

39、一般来说,运算系统还可以包括锁相环pll,该pll与逻辑电路连接;pll可以接收参考时钟信号,并根据参考时钟信号向逻辑电路提供第三时钟信号。第三时钟信号的频率与逻辑电路的工作频率匹配,可以驱动逻辑电路工作。

40、在一种可能的实现方式中,电源电路可以包括第一电源和第二电源;其中,第一电源可以向电压调节电路提供第一输出电压;第二电源可以向逻辑电路提供第二输出电压;调控电路分别与第一电源和第二电源连接。在此情况下,调控电路可以根据第一时钟信号,分别控制第一电源调节第一输出电压,控制第二电源调节第二输出电压。其中,第一输出电压和第二输出电压保持一致。

41、第四方面,本技术实施例提供一种集成模块,该集成模块可以包括逻辑电路和如上述第一方面或第二方面中任一项所提供的电压调节电路。第四方面中相应方案的技术效果可以参照第一方面中对应方案可以得到的技术效果,重复之处不予详述。

42、在一种可能的实现方式中,集成模块还可以包括锁相环pll,该pll与逻辑电路连接;pll可以接收参考时钟信号,并根据参考时钟信号向逻辑电路提供第三时钟信号。

43、第五方面,本技术实施例提供一种集成电路,该集成电路包括至少一个如上述第三方面中任一项所提供的运算系统,和系统总线,该系统总线分别与上述至少一个运算系统连接;在集成电路中,系统总线可以分别向至少一个运算系统提供对应的至少一个参考时钟信号。第五方面中相应方案的技术效果可以参照第一方面中对应方案可以得到的技术效果,重复之处不予详述。

44、第六方面,本技术实施例提供一种电压调节方法,该方法可以应用与上述电压调节电路。第六方面中相应方案的技术效果可以参照第一方面中对应方案可以得到的技术效果,重复之处不予详述。

45、示例性的,该方法主要包括:电压调节电路可以根据电源电路的输出电压,通过振荡器生成第一时钟信号,该振荡器的工艺角类型与逻辑电路的工艺角类型相同,该电源电路的输出电压可以为逻辑电路供电;电压调节电路进而根据第一时钟信号控制电源电路调节输出电压。

46、示例性的,电压调节电路在根据第一时钟信号,控制电源电路调节输出电压时,可以按照分频倍数对第一时钟信号进行分频,得到第二时钟信号;根据第二时钟信号与参考时钟信号之间的相对频率大小关系,控制电源电路调节输出电压。

47、其中,tt corner类型的振荡器输出的第一时钟信号的频率,除以参考时钟信号的频率后的商值,为分频倍数。

48、电压调节电路在根据第二时钟信号与参考时钟信号之间的相对频率大小,控制电源电路调节输出电压时,可以在第二时钟信号的频率大于参考时钟信号的频率时,控制电源电路降低输出电压;或,在第二时钟信号的频率小于参考时钟信号的频率时,控制电源电路增大输出电压。

49、本技术的这些方面或其它方面在以下实施例的描述中会更加简明易懂。

本文地址:https://www.jishuxx.com/zhuanli/20240822/279958.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表