SMT核心控制器、编译器和在SMT核心控制器上执行编译后的运行时代码的方法与流程

- 国知局

- 2024-10-09 15:05:56

本发明大体上涉及同步多线程(simultaneous multiple threading,smt)领域,更具体地,涉及同步多线程核心控制器、编译器以及编译运行时代码和在同步多线程核心控制器上执行编译后的运行时代码的方法。

背景技术:

1、同步多线程(simultaneous multiple threading,smt)技术通常使得多个线程能够在同一个物理核上共同执行。smt技术使得多个独立线程的执行可以使用不同处理器提供的多个资源。smt技术通常用于超标量中央处理器通过硬件线程执行多个线程。但是,与多线程执行的性能相比,传统的smt技术会影响单线程执行的性能。

2、目前已做了一些尝试来提高单线程执行的性能,例如使用线程级推测方法,该方法也称为多个推测线程。但是,传统上,这样的粒度相对较粗,容易触发多线程执行之间的地址冲突。此外,传统的线程级推测方法使用一个芯片、多个处理器来解决线程之间的冲突,这降低了总体吞吐量和效率。因此,存在一个技术问题,即如何增加多线程执行的总体吞吐量,同时提高效率并改进单线程执行。

3、因此,鉴于上述讨论,需要克服与传统的同步多线程核心控制器相关的上述缺点。

技术实现思路

1、本发明提供了同步多线程(simultaneous multiple-threading,smt)核心控制器、编译器以及编译运行时代码和在同步多线程核心控制器上执行运行时代码的方法。本发明提供了一种对现有问题的方案,现有问题为如何增加多线程执行的总体吞吐量,同时提高效率并改进单线程执行。本发明的目的是提供一种至少部分地解决在现有技术中遇到的问题的方案,并提供改进的同步多线程核心控制器、改进的编译器以及改进的方法,以编译运行时代码和在同步多线程核心控制器上执行运行时代码,同时增加总体吞吐量,提高效率,例如加速smt核心控制器上的单线程执行。

2、本发明的一个或多个目的是通过所附独立权利要求中提供的方案实现的。本发明的有利实现方式在从属权利要求中进一步定义。

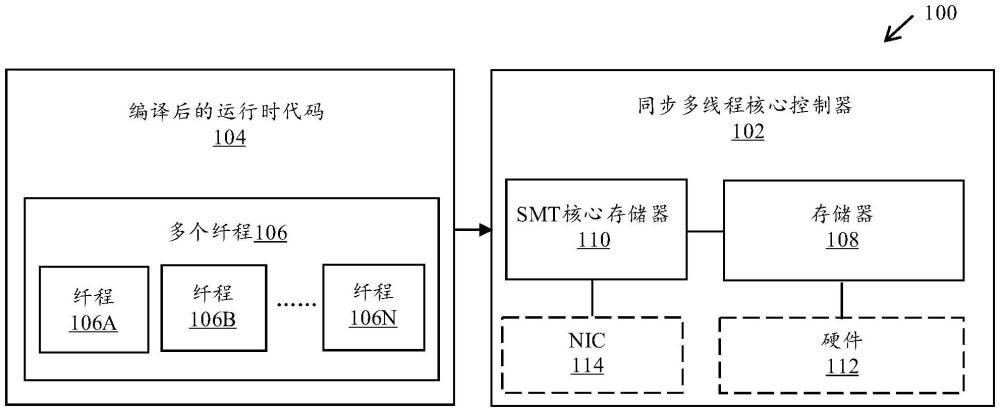

3、在一个方面,本发明提供了一种同步多线程(simultaneous multiple-threading,smt)核心控制器,该smt核心控制器用于接收包括多个纤程的编译后的运行时代码。此外,同步多线程(simultaneous multiple-threading,smt)核心控制器用于利用存储器并行执行多个纤程中的至少两个纤程,并确定正在并行执行的至少两个纤程中的任意纤程之间是否存在任何存储冲突。此外,同步多线程(simultaneous multiple-threading,smt)核心控制器用于取消存在任何存储冲突的纤程,重新执行存在任何存储冲突的纤程,并将不存在存储冲突的纤程的任何存储操作提交给同步多线程(simultaneous multiple-threading,smt)核心存储器。

4、smt核心控制器用于接收包括多个纤程的编译后的运行时代码。此外,smt核心控制器用于利用存储器并行执行多个纤程中的至少两个纤程。此外,smt核心控制器确定在并行执行的至少两个纤程之间是否存在任何存储冲突。此外,如果确定存在存储冲突,则重新执行存在存储冲突的纤程,如果确定不存在存储冲突,则在单个存储事务中执行存储操作。并行执行多个纤程中的至少两个纤程可提高超标量流水线利用率和单个线程的并行性。此外,smt核心控制器通过增加多个纤程的总体吞吐量和加速单线程执行,支持有效且高效地执行多个纤程和单线程执行。

5、在一种实现方式中,多个纤程的调度由同步多线程(simultaneous multiple-threading,smt)核心控制器的硬件执行。

6、硬件用于决定多个纤程的执行顺序,并相应地分配smt资源。

7、在另一种实现方式中,多个纤程中的至少一个纤程是计算纤程,smt核心控制器还用于在执行计算纤程时利用smt核心存储器的堆和栈帧。

8、有益的是,利用堆和栈帧来执行计算纤程使得smt核心控制器能够通过已经存在的数据来计算和执行至少一个纤程。

9、在另一种实现方式中,多个纤程中的至少一个纤程是存储纤程,smt核心控制器还用于在执行存储纤程时将堆和栈帧专用于存储纤程,并在提交存储纤程时合并专用的堆和栈帧。

10、有益的是,存储纤程的使用使得smt核心控制器能够执行包括用于执行存储纤程的堆和栈帧的存储分配操作。

11、在又一个方面,本发明提供了一种编译器,用于对根据上述权利要求中任一项所述的smt核心控制器的运行时代码进行编译,其中,该编译器用于接收串行代码,并解析串行代码,以识别待并行执行的多个纤程。多个纤程的零个或多个纤程分别对应于一个条件块,多个纤程中的零个或多个纤程分别对应于一个函数调用。该编译器用于生成包括多个纤程的编译后的运行时代码。

12、编译器对smt核心控制器的运行时代码进行编译。编译器接收串行代码,然后解析串行代码,以识别待并行执行的多个纤程。多个纤程包括零个或多个条件块纤程和函数调用纤程。有益的是,编译器生成编译后的运行时代码使得smt核心控制器能够执行编译后的运行时代码,这有利于增加总体吞吐量,同时提高效率,例如加速smt核心控制器上的单线程执行。

13、在另一种实现方式中,条件块是一个循环。

14、在该实现方式中,条件块使得编译器能够生成多个纤程,这有利于增加总体吞吐量,同时提高效率,例如加速smt核心控制器上的单线程执行。

15、在另一种实现方式中,编译器还用于在解析串行代码之前确定设置了多纤程特性比特位(multiple fiber bit)。

16、有益的是,在设置了多纤程特性比特位时,多纤程特性比特位使得编译器能够解析串行代码,在未设置多纤程特性比特位时,则限制编译器解析串行代码。

17、在另一方面,本发明提供了一种在同步多线程(simultaneous multiple-threading,smt)核心上执行编译后的运行时代码的方法。该方法包括:接收包括多个纤程的编译后的运行时代码,并利用存储器并行执行该多个纤程中的至少两个纤程。该方法还包括:确定并行执行的至少两个纤程中的任意纤程之间是否存在任何存储冲突,取消存在冲突的纤程,并重新执行存在冲突的纤程。此外,该方法包括将不存在存储冲突的纤程的任何存储操作提交给smt核心存储器。

18、该方法实现了本发明的同步多线程(simultaneous multiple-threading,smt)核心控制器的所有优点和技术效果。

19、在又一方面,本发明提供了一种用于编译器的方法。该方法包括:接收串行代码,并解析串行代码,以识别待并行执行的多个纤程。多个纤程中的零个或多个纤程分别对应于一个条件块,多个纤程中的零个或多个纤程分别对应于一个函数调用。此外,该方法用于生成包括多个纤程的编译后的运行时代码。

20、该方法实现了本发明的编译器的所有优点和技术效果。

21、应当理解,前述所有实现方式都可以组合在一起。需说明的是,本技术中描述的所有设备、元件、电路、单元和装置可以在软件或硬件元件或其任何类型的组合中实现。本技术中描述的各种实体所执行的所有步骤以及所描述的各种实体要执行的功能均意在指相应实体适于或用于执行相应步骤和功能。虽然在以下具体实施例的描述中,外部实体要执行的具体功能或步骤没有在执行具体步骤或功能的实体的具体详述元件的描述中反映,但是技术人员应清楚,这些方法和功能可以通过相应软件或硬件元件或其任何组合实现。应当理解,本发明的特征易于以各种组合进行组合,而不脱离由所附权利要求书所界定的本发明的范围。

22、本发明的附加方面、优点、特征和目的从附图和结合以下所附权利要求书解释的说明性实现方式的详细描述中变得显而易见。

本文地址:https://www.jishuxx.com/zhuanli/20241009/307612.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表