用于SARADC的参考纹波补偿技术的制作方法

- 国知局

- 2024-10-09 15:08:10

本说明书大体上涉及数据通信,包含例如一种用于逐次逼近寄存器(sar)模/数转换器(adc)的参考纹波补偿技术。

背景技术:

1、模/数转换器(adc)有多种类型,包含闪存adc、半闪存adc、逐次逼近寄存器(sar)adc、σ-δadc及流水线adc,每一adc具有不同结构及应用。本公开中所关注的sar adc通过其逐次逼近寄存器来识别,并连续比较内部adc的输入电压与输出电压,且判断输入是在变窄范围的中点以上还是以下,并继续此过程,直到达到所规定分辨率为止。

2、sar adc已广泛用于所有种类的系统中,尤其是数据通信电路及系统。时间交错式(ti)sar adc主导高速度、低功率及小面积的adc应用。高性能ti sar adc是5g射频(rf)基站的接收器中的重要电路。然而,具有高信噪失真比(sndr)及无杂散动态范围(sfdr)的性能通常会牺牲速度、功率、芯片面积及其它度量。在高分辨率ti sar的所有电路块当中,窄带宽度参考缓冲器被用于实现ti sar的三个设计度量,包含线性度、功率及芯片面积。

3、由于相关性及折衷,从根本上说,很难在同一时间实现三个设计目标。此外,tisar中的参考缓冲器纹波是sndr及sfdr降级的重要原因。在ti sar中,电容性数/模转换器(dac)将在复位及转换周期期间被充电/放电,这致使参考电压上的纹波(例如,电压波动)。校准及/或补偿被用于降低高分辨率adc的参考纹波。然而,工艺、电压及温度(pvt)改变会使校准及/或补偿效率更差。在某些极端情况下,参考电压纹波甚至会增加。

4、现有架构是参考校准sar架构,其中额外转换周期被用于检测并校正由参考纹波引起的错误位。以这种方式,sar实现了更高分辨率,并显著减少了芯片上解耦电容器。然而,所述架构使用了错误校正方案。此方案的错误覆盖范围限制了分辨率,并且所需额外转换周期限制了总体sar adc的速度。

5、另一现有参考补偿架构包含电荷产生器,所述电荷产生器为两个参考电压vref1及vref2提供所需电荷,因此可减少参考纹波。此架构的参考电荷补偿具有完美时序匹配,但pvt改变会使所述架构降级。此架构对仅闪存adc而非ti-sar的参考纹波进行补偿。闪存adc及sar adc的adc时序非常不同,因此所述adc的参考电压纹波展示出不同特性。在时间交错式adc中,纹波提供参考电压的显著部分,此架构无法对所述纹波进行补偿。

技术实现思路

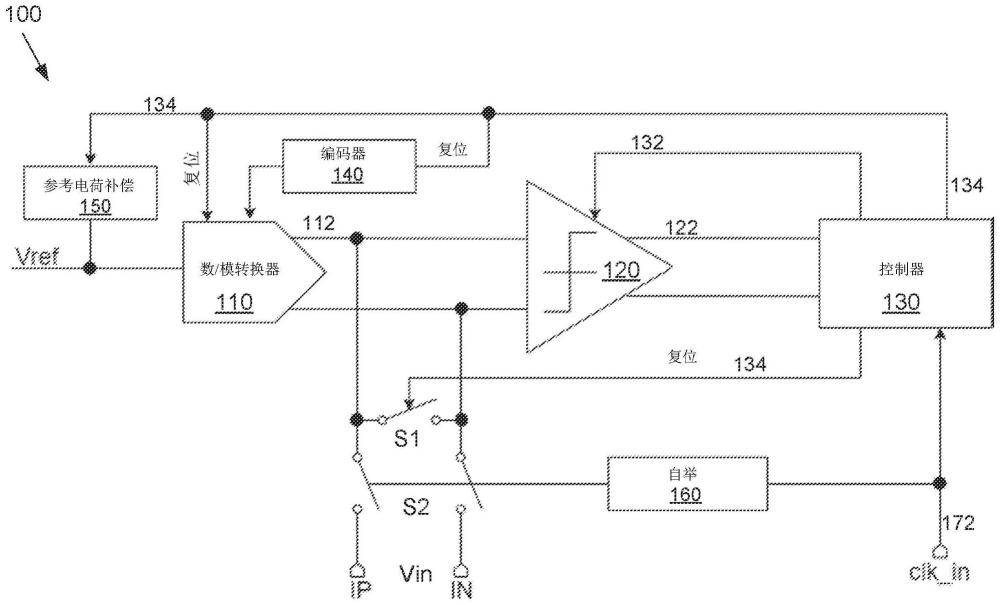

1、在一个方面中,本公开涉及一种模/数转换器(adc)电路,其包括:数/模转换器(dac)电路,其被配置为接收参考电压并基于所述参考电压来提供输出信号;比较器电路,其被配置为将所述输出信号与模拟输入信号进行比较并产生比较信号,其中基于所述输出信号大于所述模拟输入信号来产生复位命令;编码器,其被配置为通过响应于所述复位命令将与所述参考电压相关联的纹波分裂成多个脉冲对所述纹波进行补偿;及补偿电路,其被配置为响应于所述复位命令来产生补偿脉冲以对所述多个脉冲进行补偿。

2、在另一方面中,本公开涉及一种集成电路,其包括:控制器,其被配置为产生复位命令;编码器,被配置为响应于所述复位命令将与数/模转换器(dac)电路的参考电压相关联的纹波分裂成多个脉冲;及补偿电路,其被配置为响应于所述复位命令而产生补偿脉冲,其中:基于所述dac电路的输出信号大于模拟输入信号来产生所述复位命令,并且补偿脉冲被配置为对与所述纹波相关联的所述多个脉冲进行补偿。

3、在又一方面中,本公开涉及一种设备,其包括:编码器,其被配置为从控制器电路接收复位命令,并响应于所述复位命令将与模/数转换器(adc)电路的数/模转换器(dac)电路的参考电压相关联的纹波分裂成多个脉冲;及补偿电路,其被配置为从所述控制器电路接收所述复位命令,并响应于所述复位命令来产生补偿脉冲以对所述多个脉冲进行补偿,其中所述复位命令的产生是基于所述dac电路的输出信号大于所述adc电路的模拟输入信号。

技术特征:1.一种模/数转换器adc电路,其包括:

2.根据权利要求1所述的adc电路,其进一步包括控制器电路,所述控制器电路被配置为接收所述比较信号并产生所述复位命令。

3.根据权利要求2所述的adc电路,其中所述控制器电路包括有限状态机fsm电路,所述fsm电路被配置为将所述复位命令提供到所述编码器及所述补偿电路。

4.根据权利要求1所述的adc电路,其中所述补偿电路包括参考电荷补偿rcc电路,所述rcc电路被配置为产生两个补偿脉冲以对所述多个脉冲进行补偿。

5.根据权利要求4所述的adc电路,其中所述两个补偿脉冲对所述多个脉冲进行补偿以将所述多个脉冲的振幅降低到所规定范围内。

6.根据权利要求5所述的adc电路,其中所述两个补偿脉冲的宽度及量值是可调整的,以抵消所述多个脉冲。

7.根据权利要求1所述的adc电路,其中所述补偿电路进一步被配置为产生第二组补偿脉冲,以对基于所述参考电压而产生的msb纹波进行补偿。

8.根据权利要求1所述的adc电路,其中所述补偿电路进一步被配置为在由所述dac电路接收到后续参考电压之前产生所述补偿脉冲。

9.根据权利要求1所述的adc电路,其中所述补偿电路进一步被配置为通过将电荷提供到所述dac电路的参考电压端口中来产生所述补偿脉冲。

10.根据权利要求9所述的adc电路,其中所述补偿电路包括充电电路,所述充电电路被配置为提供用于向所述参考电压端口提供的电荷脉冲。

11.一种集成电路,其包括:

12.根据权利要求11所述的集成电路,其中所述控制器包括有限状态机fsm电路,所述fsm电路被配置为产生所述复位命令并将所述复位命令提供到所述编码器及所述补偿电路。

13.根据权利要求11所述的集成电路,其中所述编码器进一步被配置为通过在时域中分裂msb纹波与最低有效位lsb纹波来使复位窗口的大小加倍。

14.根据权利要求11所述的集成电路,其中所述补偿电路包括参考电荷补偿rcc电路,其中所述rcc电路被配置为产生两个补偿脉冲以对所述多个脉冲进行补偿,其中所述两个补偿脉冲的宽度及量值被调整为抵消所述多个脉冲,以将所述多个脉冲的振幅降低到所规定范围内的水平,且其中所述多个脉冲包括双峰值纹波。

15.根据权利要求11所述的集成电路,其中所述补偿电路被配置为通过将电荷注入到所述dac电路的参考电压端口中来产生所述补偿脉冲。

16.根据权利要求15所述的集成电路,其进一步包括充电电路,其中所述充电电路由两个时钟信号来控制,并被配置为提供用于注入到所述参考电压端口中的电荷脉冲。

17.一种设备,其包括:

18.根据权利要求17所述的设备,其中所述编码器被配置为在时域中分裂最高有效位msb纹波与最低有效位lsb纹波。

19.根据权利要求17所述的设备,其中:

20.根据权利要求19所述的设备,其中:

技术总结本公开涉及一种用于SAR ADC的参考纹波补偿技术。一种模/数转换器ADC电路包含数/模转换器DAC电路、比较器电路、编码器及补偿电路。所述DAC电路接收参考电压,并基于所述参考电压来提供输出信号。所述比较器电路将所述输出信号与模拟输入信号进行比较,并产生比较信号。基于所述输出信号大于所述模拟输入信号来产生复位命令。所述编码器响应于复位命令将与所述参考电压相关联的纹波分裂成多个脉冲。响应于所述复位命令,所述补偿电路产生补偿脉冲以对所述多个脉冲进行补偿。技术研发人员:孟新,Y·刘,曹军受保护的技术使用者:安华高科技股份有限公司技术研发日:技术公布日:2024/9/29本文地址:https://www.jishuxx.com/zhuanli/20241009/307767.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表