一种肖特基势垒氧化物薄膜晶体管及其制备方法

- 国知局

- 2024-10-09 15:32:34

本技术涉及半导体,具体而言,涉及一种肖特基势垒氧化物薄膜晶体管及其制备方法。

背景技术:

1、随着技术的不断发展,肖特基势垒金属氧化物薄膜晶体管(schottky barriermetal oxide thin film transistor,sbmo-tft)因其优异的本征电性能逐步受到更多的关注。与普通的金属氧化物薄膜晶体管相比,sbmo-tft通常具备高本征增益、低功耗、显著减弱的短沟道效应、更佳的器件稳定性以及饱和后的电流稳定输出特性等优点。因此,sbmo-tft适合应用到高像素密度的amlcd(主动矩阵液晶显示器)、amoled(主动矩阵有机发光二极管显示器)、mini-led(迷你发光二极管)显示器件、micro-led(微发光二极管)显示器件等电流驱动型显示器件或低功耗集成电路中,同时也适合应用于构建动态随机存储器(dram)。

2、对sbmo-tft来说,其制作关键是在源电极和半导体层形成良好的肖特基接触,以在源电极和半导体层之间形成肖特基势垒,而目前业界主要通过严格控制源电极和半导体层的接触界面处的氧等离子处理强度或插层厚度,来减小对应sbmo-tft的肖特基势垒,使源电极具有较强的载流子注入能力,从而确保对应sbmo-tft具有较高的饱和输出电流。但值得注意的是,这种sbmo-tft中的源电极的肖特基势垒接触部位会因界面缺陷对注入的大量载流子进行俘获,极易出现器件电性特性迟滞现象,严重影响器件稳定性,同时前述这种sbmo-tft工作在饱和状态时,半导体层中的耗尽区会产生较强的纵向电场,该纵向电场会导致注入的载流子发生热载流子效应(即引发半导体中的金属-氧离子键断裂,或造成载流子注入栅介质层),从而严重影响器件的可靠性。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种肖特基势垒氧化物薄膜晶体管及其制备方法,能够在利用源极层处形成的欧姆(准欧姆)接触和肖特基接触确保高饱和输出电流的器件电学特性的基础上,通过具备载流子隧穿特性的扩散阻挡层避免因源极层的电极材料向半导体层扩散而产生的载流子陷阱,并通过功函调控层极大地提升源极层相对于半导体层的功函数差异,可以极大提升肖特基势垒高度,极大减少源极层在肖特基接触部位处的载流子注入,以有效减少界面缺陷对载流子的俘获,避免半导体层中的耗尽区在强纵向电场下产生热载流子效应和载流子陷阱,从而极大地改善器件电学特性迟滞现象,提升器件的稳定性和可靠性,同时无需采用成本高的贵金属(如pt、pd、au等)来制备高功函数的源极层,以有效降低器件的制备成本。

2、为了实现上述目的,本技术实施例采用的技术方案如下:

3、第一方面,本技术提供一种肖特基势垒氧化物薄膜晶体管的制备方法,所述制备方法包括:

4、提供一基底;

5、在所述基底的一侧依次层叠制备栅极层、栅介质层和半导体层,得到第一半导体器件,其中所述栅极层和所述半导体层均图形化;

6、在所述第一半导体器件的远离所述基底的一侧制备扩散阻挡层、功函调控层和电极膜层,得到第二半导体器件,其中所述扩散阻挡层满足载流子隧穿效应,所述功函调控层设置在所述扩散阻挡层与所述电极膜层之间,所述扩散阻挡层与所述功函调控层各自在所述基底上的投影区域相互重合,且所述扩散阻挡层所对应的投影区域处于所述半导体层在所述基底上的投影区域内,所述电极膜层覆盖有所述半导体层的未被所述扩散阻挡层覆盖的外侧表面,其中所述功函调控层用于提升所述电极膜层的功函数,所述扩散阻挡层用于阻挡所述电极膜层的电极材料向所述半导体层扩散;

7、在所述第二半导体器件的远离所述基底的一侧进行光刻图形化,以将所述电极膜层图形化为相互间隔的源极层和漏极层,并将所述功函调控层图形化为与源极层和漏极层分别侧面对齐的两个功函调控部位;或者,在所述第二半导体器件的远离所述基底的一侧进行光刻图形化,以将所述电极膜层图形化为与所述扩散阻挡层和所述功函调控层同时侧面对齐的源极层,而后对所述半导体层的未被所述源极层和所述扩散阻挡层覆盖的膜层部位进行导体化,以形成用于充当漏极区的导体化膜层部位。

8、在可选的实施方式中,所述在所述基底的一侧依次层叠制备栅极层、栅介质层和半导体层,得到第一半导体器件的步骤,包括:

9、在所述基底的一侧表面上溅射沉积形成栅极层,并对沉积的所述栅极层进行光刻图形化;

10、在所述基底的制备有所述栅极层的侧面上,基于等离子体增强化学气相沉积法或原子层沉积法生长形成所述栅介质层,使所述栅介质层覆盖所述栅极层和所述基底的未被所述栅极层遮挡的侧面区域;

11、在所述栅介质层的远离所述基底的外侧表面上,基于磁控溅射法或原子层沉积法沉积形成所述半导体层,并对沉积得到的所述半导体层进行光刻图形化,得到所述第一半导体器件。

12、在可选的实施方式中,所述在所述第一半导体器件的远离所述基底的一侧制备扩散阻挡层、功函调控层和电极膜层,得到第二半导体器件的步骤,包括:

13、在所述第一半导体器件的远离所述基底的外侧表面上,基于磁控溅射法或原子层沉积法依次沉积形成所述扩散阻挡层和所述功函调控层,其中所述扩散阻挡层满足载流子隧穿效应;

14、依次对沉积的所述功函调控层和所述扩散阻挡层进行光刻图形化,使图形化后的所述扩散阻挡层和所述功函调控层各自对应的投影区域相互重合,并且图形化后的所述扩散阻挡层所对应的投影区域处于所述半导体层所对应的投影区域内;

15、在所述功函调控层的远离所述扩散阻挡层的一侧溅射沉积形成电极膜层,得到所述第二半导体器件。

16、在可选的实施方式中,所述在所述第一半导体器件的远离所述基底的一侧制备扩散阻挡层、功函调控层和电极膜层,得到第二半导体器件的步骤,包括:

17、在所述第一半导体器件的远离所述基底的外侧表面上,基于磁控溅射法或原子层沉积法沉积形成满足载流子隧穿效应的所述扩散阻挡层,并对所述扩散阻挡层进行光刻图形化,使图形化后的所述扩散阻挡层所对应的投影区域处于所述半导体层所对应的投影区域内;

18、在所述扩散阻挡层的远离所述半导体层的一侧溅射沉积形成电极膜层;

19、在真空氛围或惰性气体氛围下对所述电极膜层和所述扩散阻挡层进行退火处理,使所述电极膜层的与所述扩散阻挡层直接接触的局部区域发生氧化反应,以形成与所述扩散阻挡层投影区域重合的所述功函调控层,得到所述第二半导体器件。

20、在可选的实施方式中,所述对所述半导体层的未被所述源极层和所述扩散阻挡层覆盖的膜层部位进行导体化,以形成用于充当漏极区的导体化膜层部位的步骤,包括:

21、利用氩等离子体轰击所述半导体层的未被所述源极层和所述扩散阻挡层覆盖的膜层部位,以将被轰击的具备半导体特性的膜层部位转换为所述导体化膜层部位。

22、在可选的实施方式中,所述对所述半导体层的未被所述源极层和所述扩散阻挡层覆盖的膜层部位进行导体化,以形成用于充当漏极区的导体化膜层部位的步骤,包括:

23、在所述第二半导体器件的制备出所述源极层的外侧表面上,至少采用氮化硅材料和二氧化硅材料中的氮化硅材料沉积形成钝化层,并对所述钝化层进行退火处理,使所述半导体层的与所述钝化层直接接触的膜层部位在所述钝化层的氢扩散掺杂作用下进行导体化,以将半导体层的与所述钝化层直接接触且具备半导体特性的膜层部位转换为所述导体化膜层部位。

24、在可选的实施方式中,所述栅极层的材料为al、cu、mo、ti、ito中的任意一种;

25、所述栅介质层的材料为sio2、氮化硅、氧化铝、氧化铪、氧化锆中的任意一种或多种材料的堆叠;

26、所述半导体层的材料为ingazno、inzno、inznsno、ln-izo、ingao、zno、ga2o3、sno2和in2o3中的任意一种;

27、所述扩散阻挡层的材料为sio2、al2o3、hfo2、zro2中的任意一种;

28、所述电极膜层的材料为cu、mo、co、ti、ni、w、cr、ag或ito中的任意一种,其中所述电极膜层的功函大于所述半导体层的功函;

29、所述功函调控层的材料为氧化铜、氧化钼、氧化钴、氧化钛、氧化镍、氧化钨、氧化铬、氧化银、氧化碲、氧化锡中的任意一种。

30、在可选的实施方式中,所述栅极层的厚度范围为10-1000nm;

31、所述栅介质层的厚度范围为5-500nm;

32、所述半导体层的厚度范围为5-200nm;

33、所述扩散阻挡层的厚度范围为1-5nm;

34、所述功函调控层的厚度范围为1-100nm。

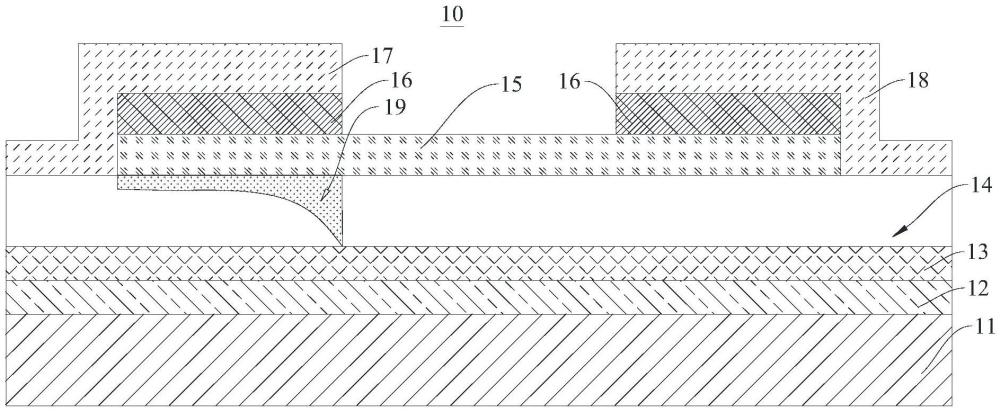

35、第二方面,本技术提供一种肖特基势垒氧化物薄膜晶体管,所述薄膜晶体管包括:

36、基底;

37、在所述基底的一侧依次层叠设置的栅极层、栅介质层和半导体层,其中所述栅介质层覆盖所述栅极层;

38、在所述半导体层上依次层叠设置的扩散阻挡层、功函调控层和电极膜层,其中所述扩散阻挡层满足载流子隧穿效应,所述功函调控层设置在所述扩散阻挡层与所述电极膜层之间,所述扩散阻挡层在所述基底上的投影区域处于所述半导体层在所述基底上的投影区域内,所述功函调控层用于提升所述电极膜层的功函数,所述扩散阻挡层用于阻挡所述电极膜层的电极材料向所述半导体层扩散;

39、所述功函调控层包括相互间隔的两个功函调控部位,两个所述功函调控部位各自在所述基底上的投影区域均处于所述扩散阻挡层所对应的投影区域内;

40、所述电极膜层包括相互间隔的源极层和漏极层,所述源极层覆盖所述半导体层的未被所述扩散阻挡层覆盖的部分外侧表面,所述漏极层覆盖所述半导体层的未被所述扩散阻挡层覆盖的剩余外侧表面,所述源极层与一个功函调控部位侧面对齐,所述漏极层与另一个功函调控部位侧面对齐,其中所述源极层的部分区域与所述半导体层直接接触形成欧姆接触或准欧姆接触,所述源极层的部分区域间隔对应功函调控部位和所述扩散阻挡层与所述半导体层形成肖特基势垒。

41、第三方面,本技术提供一种肖特基势垒氧化物薄膜晶体管,所述薄膜晶体管包括:

42、基底;

43、在所述基底的一侧依次层叠设置的栅极层、栅介质层和半导体层,其中所述栅介质层覆盖所述栅极层;

44、在所述半导体层上依次层叠设置的扩散阻挡层、功函调控层和源极层,其中所述扩散阻挡层满足载流子隧穿效应,所述功函调控层设置在所述扩散阻挡层与所述源极层之间,所述扩散阻挡层在所述基底上的投影区域处于所述半导体层在所述基底上的投影区域内,所述扩散阻挡层与所述功函调控层各自在所述基底上的投影区域相互重合,所述源极层覆盖所述半导体层的未被所述扩散阻挡层覆盖的部分外侧表面,所述源极层与所述扩散阻挡层和所述功函调控层同时侧面对齐,其中所述功函调控层用于提升所述源极层的功函数,所述扩散阻挡层用于阻挡所述源极层的电极材料向所述半导体层扩散;

45、所述半导体层包括半导体膜层部位和导体化膜层部位,其中所述导体化膜层部位为所述半导体层的未被所述源极层和所述扩散阻挡层覆盖的膜层部位,所述半导体膜层部位为所述半导体层的除所述导体化膜层部位以外的剩余膜层部位,其中所述导体化膜层部位用于作为对应薄膜晶体管的漏极区,所述源极层的部分区域与所述半导体膜层部位直接接触形成欧姆接触或准欧姆接触,所述源极层的部分区域间隔所述功函调控层和所述扩散阻挡层与所述半导体膜层部位形成肖特基势垒。

46、在此情况下,本技术实施例的有益效果可以包括以下内容:

47、本技术在基底上依次制备图形化栅极层、栅介质层、图形化半导体层、图形化扩散阻挡层、图形化功函调控层和图形化源极层,其中扩散阻挡层在基底上的投影区域处于半导体层在基底上的投影区域内,源极层覆盖半导体层的未被扩散阻挡层覆盖的部分外侧表面,此时源极层的部分区域与半导体层直接接触形成欧姆接触或准欧姆接触,源极层的部分区域间隔对应功函调控部位和扩散阻挡层与半导体层形成肖特基势垒,从而在利用源极层处形成的欧姆(准欧姆)接触和肖特基接触确保高饱和输出电流的器件电学特性的基础上,通过具备载流子隧穿特性(即满足载流子隧穿效应)的扩散阻挡层防止源极层的电极材料向半导体层扩散,以避免因源极层的电极材料向半导体层扩散而产生的载流子陷阱,并通过功函调控层极大地提升源极层相对于半导体层的功函数差异,可以极大提升肖特基势垒高度,极大减少源极层在肖特基接触部位处的载流子注入,以有效减少界面缺陷对载流子的俘获,避免半导体层中的耗尽区在强纵向电场下产生热载流子效应和载流子陷阱,进而极大地改善器件电学特性迟滞现象,提升器件的稳定性和可靠性,同时无需采用成本高的贵金属来制备高功函数的源极层,以有效降低器件的制备成本。

48、为使本技术的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

本文地址:https://www.jishuxx.com/zhuanli/20241009/309099.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表