一种处理器、电子设备及访存一致性验证方法与流程

- 国知局

- 2024-11-06 14:43:35

本技术属于电子电路领域,具体涉及一种处理器、电子设备及访存一致性验证方法。

背景技术:

1、芯片开发过程中需要实现不同高速外设接口以连接设备,如pcie(peripheralcomponent interconnect express,一种高速串行计算机接口总线标准),sata(serialadvanced technology attachment,一种高速串行链接协议),usb(universal serialbus,通用串行总线)等外接设备以及gpu(graphic processing unit,图形处理单元)、vpu(video processing unit,视频处理单元)等设备,都需要对存储空间进行dma(directedmemory access,直接存储访存)访存。该访存过程会产生和cpu(central processingunit,中央处理器)访存之间的一致性相关问题。即,cpu读写访存某一块存储空间时,会先将相应数据副本缓存到本地cache中,而当外设需要进行dma读写访存同一块地址空间的时候,系统中的一致性维护单元,需要对相应cache空间的副本做一致性操作。通常情况下,如果是外设要对内存进行dma写操作,则需要先作废相应cache中已有副本,再对内存进行dma写;如果外设要对内存进行dma读操作,则要先写回cache中已有副本到内存空间,再对内存进行dma读。一致性维护操作过程出现问题可能会导致设备读取不到正确的数据,或者cpu读不到外设更新的内容。

技术实现思路

1、鉴于此,本技术的目的在于提供一种处理器、电子设备及访存一致性验证方法,以改善现有dma访存一致性验证存在的通用性差、实现方法复杂的问题。

2、本技术的实施例是这样实现的:

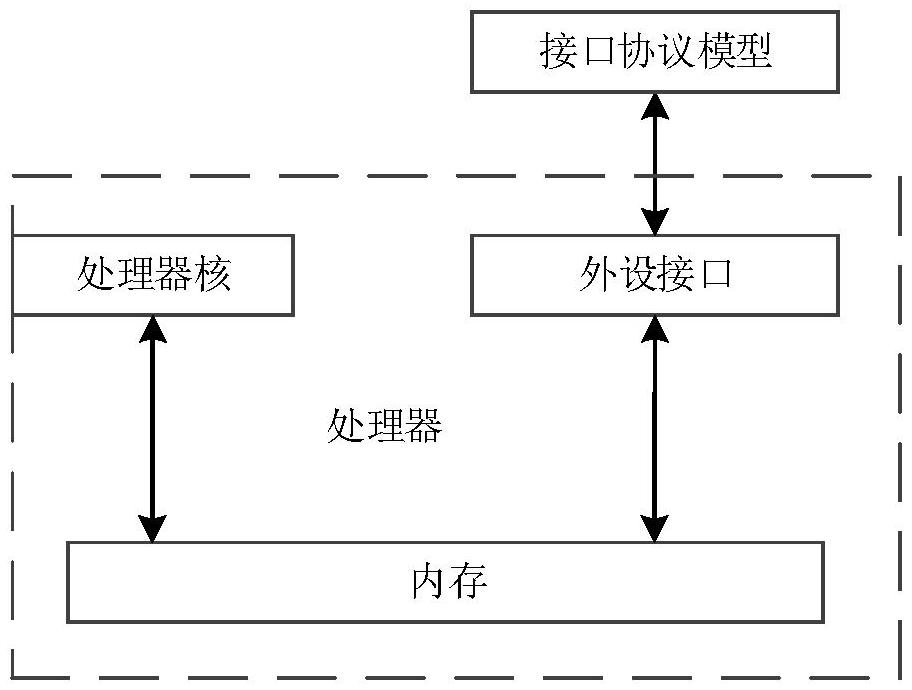

3、第一方面,本技术实施例提供了一种处理器,包括:内存、外设接口、处理器核;外设接口被配置为连接接口协议模型,所述接口协议模型用于模拟外部设备的dma访存;处理器核被配置为配置所述接口协议模型中的寄存器组,以使所述接口协议模型基于所述寄存器组中的值,通过所述外设接口发出dma访存操作;以及向所述内存发出目标访存操作,其中,所述目标访存操作的访存地址与所述dma访存操作中的访存地址一致;所述处理器核,还被配置为将所述目标访存操作的访存数据与所述dma访存操作的访存数据进行一致性比较,得到比较结果。

4、在上述实施例中,利用可由寄存器配置驱动的接口协议模型替换外部设备,由处理器核通过配置寄存器的方式使接口协议模型发出相应的dma访存操作,以及发出访存地址与dma访存操作中的访存地址一致的目标访存操作,之后将目标访存操作的访存数据与dma访存操作的访存数据进行一致性比较,便可检查dma访存一致性相关数据的正确性,并且通过配置寄存器组的值,便可实现不同属性的dma访存操作,具有复用性(通用性)好及实现方法简单的优点。

5、在一种可能的实施方式,所述接口协议模型包含第一接口模型、第二接口模型和寄存器组,所述第一接口模型和所述第二接口模型共享所述寄存器组,所述处理器核被配置为与所述第一接口模型连接,所述外设接口被配置为与所述第二接口模型连接;所述处理器核,被配置为通过所述第一接口模型配置所述寄存器组,以使所述第二接口模型基于所述寄存器组中的值,通过所述外设接口发出所述dma访存操作。

6、在上述实施例中,第一接口模型和第二接口模型共享寄存器组,处理器核通过对第一接口模型(从机接口模型)的相关寄存器组进行配置,这些寄存器组会驱动第二接口模型(主机接口模型)发出相应的对内存空间的读、写访存,即dma访存,这样便于根据需求实现不同属性的dma访存操作。

7、在一种可能的实施方式,所述寄存器组包括多个寄存器,通过配置所述多个寄存器的值调整所述dma访存操作中的猝发类型、猝发长度、猝发字节大小、缓存属性、访存地址中的至少一种属性。

8、在上述实施例中,通过配置多个寄存器的值,可以实现不同猝发类型、猝发长度、猝发字节大小、缓存属性、访存地址中的至少一种属性的dma访存操作,极大的提高了验证的通用性,通过改变寄存器的值,即可实现不同属性的dma访存操作,从而灵活的构造各种dma访存一致性场景。

9、在一种可能的实施方式,所述处理器核,还被配置为将第一校验结果与第二校验结果进行一致性比较,得到比较结果,其中,所述第二校验结果为所述目标访存操作的访存数据的校验和结果;所述第一校验结果为所述dma访存操作的访存数据的校验和结果。

10、在上述实施例中,在进行访存一致性验证时,可以是将目标访存操作的访存数据的校验和结果和dma访存操作的访存数据的校验和结果进行一致性比较,这样可以极大的提高比对效率,由于一般外部设备进行dma访存时候数据量比较大,检查数据正确性时,一一比对的方法效率太低。

11、在一种可能的实施方式,所述接口协议模型还包括存储表,所述存储表用于储存所述第一校验结果,和/或所述第二校验结果。

12、在上述实施例中,利用接口协议模型中的存储表来储存第一校验结果,和/或第二校验结果,从而减少对处理器的存储空间的使用,从而节约处理器的本地存储空间。

13、在一种可能的实施方式,若所述dma访存操作为dma写访存操作,所述目标访存操作为读访存操作;所述接口协议模型,还被配置为根据所述dma访存操作的访存数据,确定所述第一校验结果,并将所述第一校验结果存储至指定存储空间;所述处理器核,还被配置为根据所述目标访存操作的访存数据,确定所述第二校验结果,并从所述指定存储空间读取所述第一校验结果与所述第二校验结果进行一致性比较。

14、在上述实施例中,接口协议模型在发起dma写访存操作时,将根据dma访存操作的访存数据确定的第一校验结果存储至指定存储空间,处理器核在进行读访存操作时,将根据目标访存操作的访存数据确定的第二校验结果与第一校验结果进行一致性比较,极大的提高比对效率,从而可以快速完成访存一致性校验。

15、在一种可能的实施方式,若所述dma访存操作为dma读访存操作,所述目标访存操作为写访存操作;所述接口协议模型,还被配置为根据所述dma读访存操作的访存数据,确定所述第一校验结果,并将所述第一校验结果存储至所述指定存储空间;所述处理器核,还被配置为根据所述目标访存操作的访存数据,确定所述第二校验结果,并将所述第二校验结果存储至指定存储空间,并从所述指定存储空间读取所述第一校验结果和所述第二校验结果,以及将所述第一校验结果与所述第二校验结果进行一致性比较。

16、在上述实施例中,接口协议模型在发起dma读访存操作时,将根据dma访存操作的访存数据确定的第一校验结果存储至指定存储空间,处理器核在进行写访存操作时,将根据目标访存操作的访存数据确定的第二校验结果与第一校验结果进行一致性比较,极大的提高比对效率,从而可以快速完成访存一致性校验。

17、在一种可能的实施方式,所述处理器还包括:片上网络;所述外设接口、所述处理器核、所述内存均与所述片上网络连接;所述处理器核包含本地缓存,所述处理器核还被配置为在向所述内存发出目标写访存操作时,将所述目标写访存操作中的访存数据写入本地缓存;所述片上网络中的一致性维护单元,被配置为在接收到所述外设接口发出的dma访存操作时,获取所述本地缓存中的访存数据,并将所述访存数据写入所述内存,以及通过所述外设接口返回所述访存数据。

18、在上述实施例中,增设片上网络,来连接外设接口、处理器核、内存,有利于维护数据一致性,并且便于结构扩展。

19、第二方面,本技术实施例还提供了一种电子设备,包括如上述第一方面实施例和/或结合第一方面实施例的任一种可能的实施方式提供的处理器。

20、第三方面,本技术实施例还提供了一种访存一致性验证方法,应用于处理器,所述处理器包括内存、处理器核和外设接口,所述外设接口被配置为连接用于模拟外部设备的dma访存的接口协议模型;所述方法包括:所述处理器核配置所述接口协议模型中的寄存器组,以使所述接口协议模型基于所述寄存器组中的值,通过所述外设接口发出dma访存操作;所述处理器核向所述内存发出目标访存操作,其中,所述目标访存操作中的访存地址与所述dma访存操作中的访存地址一致;所述处理器核将所述目标访存操作的访存数据与所述dma访存操作的访存数据进行一致性比较,得到比较结果。

21、本技术的其他特征和优点将在随后的说明书阐述。本技术的目的和其他优点可通过在所写的说明书以及附图中所特别指出的结构来实现和获得。

本文地址:https://www.jishuxx.com/zhuanli/20241106/323783.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表