一种IGBT测试器件及其制备方法,以及IGBT器件及其制备方法与流程

- 国知局

- 2024-11-19 09:45:19

本发明涉及igbt测试器件,具体涉及一种igbt测试器件及其制备方法,以及igbt器件及其制备方法。

背景技术:

1、igbt(绝缘栅双极性晶体管),是由bjt(双极型三极管)和mosfet(绝缘型场效应管)组成的复合全控型电压驱动式功率半导体器件,兼有mosfet的高输入阻抗和gtr的低导通压降两方面的优点。igbt产品为垂直方向导通,发射极与栅极在器件表面位置,集电极处在器件背面的位置,igbt的制备工艺包括器件表面制程和器件背面制程。器件表面制程结束后集电极还没有完成,无法进行电学性能测试;需要器件背面制程完成后才可以将电极都接出进行igbt产品的电性测试。

2、目前igbt产品采用的一般是在制程结束完全后,通过针卡将集电极、发射极和栅极接出后,按照测试条件设置好的程序进行电性测试,然后对测试结果进行分析处理。该测试方式会导致器件表面部分制程的电性测试结果反馈延迟,如果前段的器件表面制程出现offline无法监测的变化或异常时,无法及时发现异常和修正异常,会导致后续产品继续被异常制程影响,造成产品的良率降低、报废率增加。

3、因此,需要一种方案,在igbt在器件表面制程完成后就进行电性测试,可以根据测试结果判断器件表面制程是否存在问题,可以及时排查问题并对工艺进行调整,减少后续晶圆被异常制程影响的数量,提高产品的整体良率,减小因工艺异常造成的损失。

技术实现思路

1、因此,本发明提供一种igbt测试器件及其制备方法,以及igbt器件及其制备方法,以解决现有技术中igbt电性测试方法会造成器件表面部分制程的电性测试结果反馈延迟,当前段的器件表面制程出现offline无法监测的变化或异常时,无法及时发现异常和修正异常,会导致后续产品继续被异常制程影响,造成产品的良率降低、报废率增加的问题。

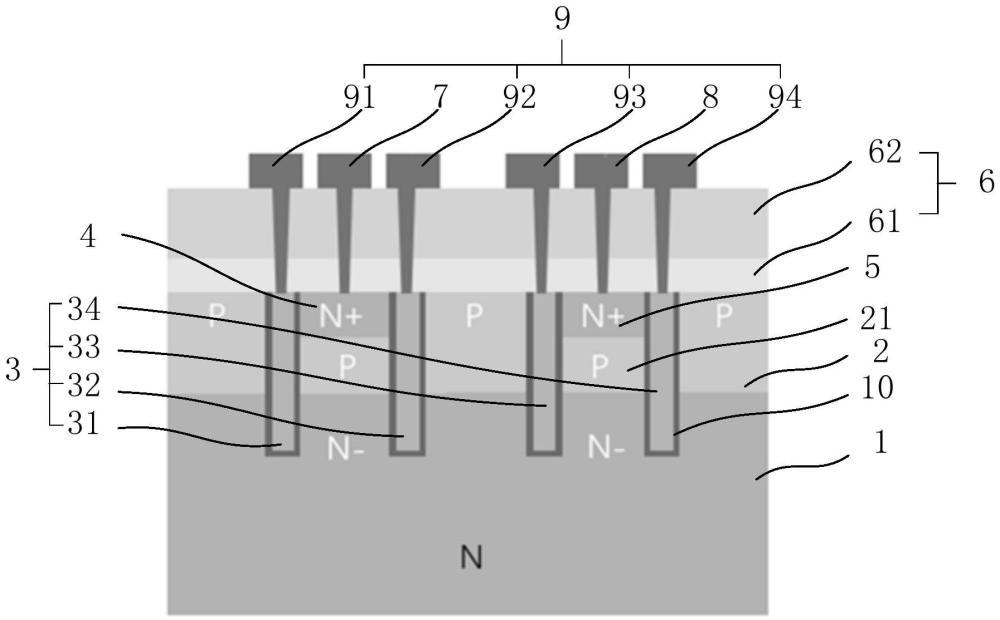

2、本发明提供一种igbt测试器件,包括:

3、应用功能区和测试功能区;

4、所述igbt测试器件包括:

5、n型漂移区,部分位于所述应用功能区,部分位于所述测试功能区;

6、p型掺杂区,位于所述n型漂移区一侧,部分位于所述应用功能区,部分位于所述测试功能区;

7、沟槽栅极,所述沟槽栅极贯穿所述p型掺杂区深入所述n型漂移区;所述沟槽栅极包括沿垂直于所述沟槽栅极延伸方向的方向依次间隔排列的第一栅极、第二栅极、第三栅极和第四栅极;所述第一栅极和所述第二栅极位于所述应用功能区,所述第三栅极和所述第四栅极位于所述测试功能区;

8、n型发射区,位于所述应用功能区,且位于所述第一栅极和所述第二栅极之间,自所述p型掺杂区背向所述n型漂移区一侧表面向所述p型掺杂区延伸,且延伸至部分所述p型掺杂区中;

9、n型集电区,位于所述测试功能区,且位于所述第三栅极和所述第四栅极之间,自所述p型掺杂区背向所述n型漂移区一侧表面向所述p型掺杂区延伸,且延伸至部分所述p型掺杂区中;

10、顶部隔离层,位于所述p型掺杂区背向所述n型漂移区一侧的表面;

11、测试发射极,位于所述顶部隔离层背向p型掺杂区一侧的表面,并贯穿所述顶部隔离层与所述n型发射区连接;

12、测试集电极,位于所述顶部隔离层背向p型掺杂区一侧的表面,并贯穿所述顶部隔离层与所述n型集电区连接;

13、测试栅极,位于所述顶部隔离层背向p型掺杂区一侧的表面,并贯穿所述顶部隔离层与所述沟槽栅极连接。

14、可选的,所述测试栅极沿垂直于所述沟槽栅极延伸方向的方向依次间隔排列第一测试栅极、第二测试栅极、第三测试栅极和第四测试栅极,分别连接所述第一栅极、所述第二栅极、所述第三栅极和所述第四栅极;

15、所述测试发射极位于所述第一测试栅极和所述第二测试栅极之间;

16、所述测试集电极位于所述第三测试栅极和所述第四测试栅极之间;

17、所述第一测试栅极和所述第二测试栅极共同连接至第一测试电极,所述第一测试电极位于所述顶部隔离层背向p型掺杂区一侧的表面;

18、所述第三测试栅极和所述第四测试栅极共同连接至第二测试电极,所述第二测试电极位于所述顶部隔离层背向p型掺杂区一侧的表面。

19、可选的,所述第一栅极和所述第二栅极之间,包括部分n型漂移区、部分p型掺杂区和所述n型发射区;其中部分p型掺杂区为p型掺杂区body区作为器件的沟道;

20、所述第三栅极和所述第四栅极之间,包括部分n型漂移区、部分p型掺杂区和所述n型发射区;其中部分p型掺杂区为p型掺杂区body区作为器件的沟道。

21、可选的,所述沟槽栅极的侧面和底面设置有栅极隔离层,所述栅极隔离层位于所述沟槽栅极与所述n型集电区之间,以及所述沟槽栅极与所述p型掺杂区之间;

22、所述沟槽栅极为多晶硅;

23、所述栅极隔离层为氧化硅。

24、可选的,所述顶部隔离层包括第一顶部隔离层和第二顶部隔离层;.

25、所述第一顶部隔离层位于所述p型掺杂区背向所述n型漂移区一侧;所述第一顶部隔离层为不做掺杂的氧化硅或氮化硅;

26、所述第二顶部隔离层位于所述第一顶部隔离层背向所述p型掺杂区一侧;所述第二顶部隔离层为含p或b、p掺杂的氧化硅。

27、本发明还提供一种igbt器件,包含上述的igbt测试器件,还包括:

28、n型场终止区,位于所述n型漂移区背向所述p型掺杂区一侧的表面;

29、p型发射区,位于所述n型场终止区背向所述n型漂移区一侧的表面;

30、集电极,位于所述p型发射区背向所述n型场终止区一侧的表面。

31、本发明还提供一种igbt测试器件的制备方法,其特征在于,包括以下步骤:

32、提供衬底层,在所述衬底层上形成n型漂移区;

33、形成沟槽栅极和p型掺杂区,在所述n型漂移区上形成所述沟槽栅极和所述p型掺杂区;所述沟槽栅极依次包括间隔排列的第一栅极、第二栅极、第三栅极和第四栅极;

34、形成n型发射区和n型集电区,在第一栅极和第二栅极之间形成所述n型发射区;在第三栅极和第四栅极之间形成所述n型集电区;

35、形成顶部隔离层,在所述p型掺杂区背向所述n型漂移区一侧的表面形成顶部隔离层;

36、形成测试发射极、测试集电极和测试栅极,在所述顶部隔离层背向p型掺杂区一侧的表面形成所述测试发射极、所述测试集电极和所述测试栅极;所述测试发射极贯穿所述顶部隔离层与所述n型发射区连接;所述测试集电极贯穿所述顶部隔离层与所述n型集电区连接;所述测试栅极贯穿所述顶部隔离层与所述沟槽栅极连接。

37、可选的,所述形成沟槽栅极和p型掺杂区的步骤包括:

38、在所述n型漂移区一侧形成沟槽区域,在沟槽区域内形成氧化硅用来做栅极隔离层;

39、然后用n型掺杂的多晶硅将沟槽填满形成所述沟槽栅极;所述沟槽栅极依次包括间隔排列的第一栅极、第二栅极、第三栅极和第四栅极;

40、在所述n型漂移区与所述多晶硅栅极的相同的一侧通过离子注入形成p型的掺杂,并向所述n型漂移区的另一侧扩散,形成所述p型掺杂区;所述p型掺杂区的深度小于所述沟槽栅极。

41、可选的,所述形成n型发射区和n型集电区的步骤包括:

42、在所述p型掺杂区背向所述n型漂移区的一侧旋涂光刻胶;

43、通过光刻工艺去除第一栅极和第二栅极之间对应的光刻胶,以及第三栅极和第四栅极之间对应的光刻胶;

44、用离子注入在去除光刻胶的地方进行n型掺杂;

45、去除剩余的光刻胶去除,对掺杂的离子进行激活,形成器件的n型发射区和n型集电区。

46、本发明还提供一种igbt器件的制备方法,用于制备上述的igbt器件,包括以下步骤:

47、形成igbt测试器件;

48、形成n型场终止区,所述型场终止区位于所述n型漂移区背向所述p型掺杂区一侧的表面;

49、形成p型发射区,所述p型发射区位于所述n型场终止区背向所述n型漂移区一侧的表面;

50、形成集电极,所述集电极位于所述p型发射区背向所述n型场终止区一侧的表面。

51、本发明的技术方案,具有如下优点:

52、一方面,本发明提供的igbt测试器件通过在igbt的器件表面设置应用功能区和测试功能区,测试功能区与应用功能区的结构对应设置,其中发射区替换为集电区,以一个测试用集电极引出,相当于使用正面的测试用集电极来代替器件背面的集电极进行电连接。可以实现在器件表面制程结束后提前进行电性测试,不用等到器件背面制程结束,即可得到器件表面制程的电性测试的结果。由于测试功能区的结构与应用功能区的结构对应设置,两者除集电区和发射区以外的结构完全相同,因此通电的路径上结构完全一致,可模拟实际通电应用时的情况。固通过测试结果可以判断器件表面制程是否存在问题,可以更早发现制程异常并及时进行问题排查并对工艺进行调整,防止后续产品被继续影响,减少后续晶圆被异常制程影响的数量,提高产品的整体良率,减小因工艺异常造成的损失。另一方面,将器件表面制程的测试结果与工艺全部完成后发最终测试结果结合起来,更容易排查异常,节省分批实验或者工程变更验证结果的时间,可以更快的将项目推进,提高效率。实际使用时,使用应用功能区一侧,配合底部的集电极正常使用,测试功能区仅占晶圆表面极小一部分,使用时不通电不影响应用功能区的使用。

53、本发明提供的igbt测试器件制备方法,可制备本发明提供的igbt测试器件。一方面,本发明提供的igbt测试器件通过在igbt的器件表面设置应用功能区和测试功能区,测试功能区与应用功能区的结构对应设置,其中发射区替换为集电区,以一个测试用集电极引出,相当于使用正面的测试用集电极来代替器件背面的集电极进行电连接。可以实现在器件表面制程结束后提前进行电性测试,不用等到器件背面制程结束,即可得到器件表面制程的电性测试的结果。由于测试功能区的结构与应用功能区的结构对应设置,两者除集电区和发射区以外的结构完全相同,因此通电的路径上结构完全一致,可模拟实际通电应用时的情况。固通过测试结果可以判断器件表面制程是否存在问题,可以更早发现制程异常并及时进行问题排查并对工艺进行调整,防止后续产品被继续影响,减少后续晶圆被异常制程影响的数量,提高产品的整体良率,减小因工艺异常造成的损失。另一方面,将器件表面制程的测试结果与工艺全部完成后发最终测试结果结合起来,更容易排查异常,节省分批实验或者工程变更验证结果的时间,可以更快的将项目推进,提高效率。实际使用时,使用应用功能区一侧,配合底部的集电极正常使用,测试功能区仅占晶圆表面极小一部分,使用时不通电不影响应用功能区的使用。

本文地址:https://www.jishuxx.com/zhuanli/20241118/330077.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。