应用于脉冲神经网络的样式框架芯片的制作方法

- 国知局

- 2024-11-19 09:55:10

本公开的实施例涉及脉冲神经网络领域,具体涉及应用于脉冲神经网络的样式框架芯片。

背景技术:

1、脉冲神经网络(spiking neural networks,snns)被认为是深度神经网络(deepneural networks,dnns)的节能替代方案。通过采用事件驱动的信息处理,snns可以显著减少与dnns相关的计算需求,同时仍能实现相当的性能。然而,当前的snns主要通过构建生成稀疏脉冲的复杂神经元模型来优先实现高准确性和大稀疏性。这种方法导致能效低和延迟高,给snns在边缘设备上的部署带来了重大挑战。

2、现有的研究主要集中在两类方案上:专用的异步处理器和稀疏感知加速器。典型的专用异步处理器包括ibm的truenorth和intel的loihi。truenorth具有4096个并行专用神经元块,设计用于高效处理数百万个神经元,同时利用脉冲操作的稀疏性。它使用同步电路进行计算,异步电路进行互连,优化了功耗。loihi集成了许多脉冲神经单元的神经形态核心用于并行处理,异步片上网络(noc)促进了核心之间的通信,进一步提高了效率。然而,这些设计在各个核心内的并行处理仍然受到限制,并且通常假设有大量片上存储器来存储整个网络的权重,这在存储受限的情况下可能不实用。

3、然而,上述方案,通常存在以下技术问题:snns需要跨多个时间步进行计算,抵消了它们在能效上的固有优势,导致更高的推理延迟。

4、该背景技术部分中所公开的以上信息仅用于增强对本发明构思的背景的理解,并因此,其可包含并不形成本国的本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的内容部分用于以简要的形式介绍构思,这些构思将在后面的具体实施方式部分被详细描述。本公开的内容部分并不旨在标识要求保护的技术方案的关键特征或必要特征,也不旨在用于限制所要求的保护的技术方案的范围。

2、本公开的一些实施例提出了应用于脉冲神经网络的样式框架芯片,来解决以上背景技术部分提到的技术问题中的一项或多项。

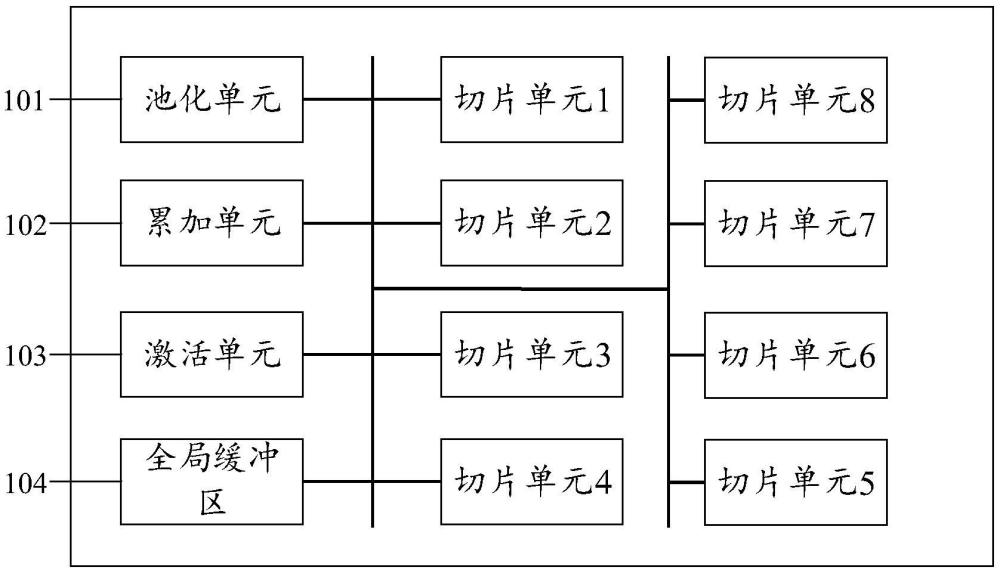

3、第一方面,本公开的一些实施例提供了一种应用于脉冲神经网络的样式框架芯片,上述样式框架芯片包括:切片单元阵列、池化单元、累加单元、激活单元与全局缓冲区,其中,切片单元阵列中的切片单元包括:处理单元阵列、切片输入缓冲区、切片输出缓冲区与切片激活单元;处理单元阵列中的处理单元包括:突触阵列组、处理输入缓冲区、处理输出缓冲区与处理累加单元;每个突触阵列包括:静态随机存取存储器阵列、突触输入缓冲区、突触输出缓冲区、图像到列调度器、位计数器、归约器、动态调度器、多路复用器;图像到列调度器分别与突触输入缓冲区、突触输出缓冲区、位计数器、归约器通信连接;归约器分别与动态调度器、多路复用器通信连接;上述切片单元阵列中的各个切片单元通信连接,上述切片单元阵列中的各个切片单元分别与池化单元、累加单元、激活单元、全局缓冲区通信连接;上述处理单元阵列中的各个处理单元通信连接,且各个处理单元分别与切片输入缓冲区、切片输出缓冲区、切片激活单元通信连接;突触阵列组中的各个突触阵列通信连接,且各个突触阵列分别与处理输入缓冲区、处理输出缓冲区、处理累加单元通信连接;突触输入缓冲区,被配置成:缓存压缩的输入脉冲;图像到列调度器,被配置成:按照时间顺序,从对应的突触输入缓冲区中读取输入脉冲,并根据行索引,对读取的输入脉冲进行解压,以及将解压的输入脉冲输入至对应的位计数器与归约器;位计数器与归约器,被配置成:统计预设时间窗口内的脉冲数,以及对所接收到的输入脉冲进行加权激活,以及将加权后的输入脉冲输入至对应的静态随机存取存储器阵列中;静态随机存取存储器阵列,被配置成:对输入脉冲进行投机快速转发处理;动态调度器,被配置成:响应于确定输入脉冲投机快速转发失败,触发条件恢复模式,将输入脉冲退回至原始脉冲序列,以确定该输入脉冲的脉冲发射时间和最终膜电位,以及将该输入脉冲的最终膜电位存储到脉冲神经网络当前神经元的膜电位中;多路复用器,被配置成:在未加权输入脉冲与加权后的输入脉冲之间进行选择,以进行存储计算。

4、可选地,动态调度器,还被配置成:动态调整时间窗口。

5、可选地,突触输出缓冲区,被配置成:缓存输入脉冲对应的膜电位与输出脉冲。

6、可选地,动态调度器,还被配置成:初始化时间窗口为最大值;响应于确定输入脉冲投机快速转发成功,更新成功计数器;响应于确定输入脉冲投机快速转发失败,更新失败计数器,并缩短时间窗口。

7、可选地,静态随机存取存储器阵列,还被配置成:响应于确定某一时间窗口内神经元没有发射任何脉冲信号,确定该神经元在时间窗口结束时的累积膜电位,并对该时间窗口内的脉冲输入与对应的权重值的乘积进行求和;响应于累积膜电位小于等于该时间窗口内的正值权重与对应脉冲输入的乘积求和,将该累积膜电位确定为累积膜电位极大值;响应于确定该累积膜电位极大值小于等于预设阈值,确定该时间窗口内神经元不发射脉冲。

8、可选地,突触阵列还包括:开关矩阵、预充电器、写入驱动器、感应放大器、第一加法器、第二加法器、第一移位寄存器、第二移位寄存器、加法累加器,上述感应放大器包括:第一读锁存器、第二读锁存器;第一读锁存器与第一加法器通信连接,第二读锁存器与第二加法器通信连接;第一移位寄存器分别与第一读锁存器、第一移位寄存器通信连接;第二移位寄存器分别与第二读锁存器、第二移位寄存器通信连接;加法累加器分别与第一移位寄存器、第二移位寄存器、动态调度器、图像到列调度器、突触输出缓冲区通信连接;开关矩阵、预充电器、写入驱动器并列串联连接;多路复用器通过总线与第一加法器、第二加法器连接。

9、可选地,池化单元,被配置成:将脉冲神经网络中的层间交互数据由四维展开为二维位图;将二维位图沿着t维度进行字节压缩,得到压缩后的稀疏字节矩阵;将压缩后的稀疏字节矩阵转换为目标存储格式。

10、本公开的上述各个实施例具有如下有益效果:通过本公开的一些实施例的应用于脉冲神经网络的样式框架芯片,利用snn脉冲活动中的稀疏性来实现高能效和低延迟的计算,同时保证了准确性。此外,投机快速转发和条件恢复,两部分协同工作从而节约不必要的计算开销,提高了计算效率。通过动态调整时间窗口的大小,不仅能够灵活应对不同神经元在各个时间步中的脉冲发射模式,还能优化推测机制的准确性,从而减少计算延迟并提高整体计算效率。通过利用脉冲数据的稀疏性和时间上的局部性,该压缩方法能够大幅度减少snn中层间交互数据的存储和传输资源。通过层次化和模块化的设计,样式框架芯片能够高效地处理snn模型中的稀疏脉冲数据,显著提高计算效率和能效。

技术特征:1.一种应用于脉冲神经网络的样式框架芯片,所述样式框架芯片包括:切片单元阵列、池化单元、累加单元、激活单元与全局缓冲区,其中,

2.根据权利要求1所述的应用于脉冲神经网络的样式框架芯片,其中,动态调度器,还被配置成:动态调整时间窗口。

3.根据权利要求1所述的应用于脉冲神经网络的样式框架芯片,其中,突触输出缓冲区,被配置成:缓存输入脉冲对应的膜电位与输出脉冲。

4.根据权利要求2所述的应用于脉冲神经网络的样式框架芯片,其中,动态调度器,还被配置成:

5.根据权利要求1所述的应用于脉冲神经网络的样式框架芯片,其中,静态随机存取存储器阵列,还被配置成:

6.根据权利要求1所述的应用于脉冲神经网络的样式框架芯片,其中,突触阵列还包括:开关矩阵、预充电器、写入驱动器、感应放大器、第一加法器、第二加法器、第一移位寄存器、第二移位寄存器、加法累加器,所述感应放大器包括:第一读锁存器、第二读锁存器;

7.根据权利要求1所述的应用于脉冲神经网络的样式框架芯片,其中,池化单元,被配置成:

技术总结本公开的实施例公开了应用于脉冲神经网络的样式框架芯片。该上述样式框架芯片包括:切片单元阵列、池化单元、累加单元、激活单元与全局缓冲区,图像到列调度器,被配置成:按照时间顺序,从对应的突触输入缓冲区中读取输入脉冲;位计数器与归约器,被配置成:统计预设时间窗口内的脉冲数,以及对所接收到的输入脉冲进行加权激活;静态随机存取存储器阵列,被配置成:对输入脉冲进行投机快速转发处理;动态调度器,被配置成:响应于确定输入脉冲投机快速转发失败,触发条件恢复模式,将输入脉冲退回至原始脉冲序列,以确定该输入脉冲的脉冲发射时间和最终膜电位。该实施方式能够高效地处理SNN模型中的稀疏脉冲数据,显著提高计算效率和能效。技术研发人员:蒋力,刘方鑫,汪宗武,杜宇航受保护的技术使用者:上海期智研究院技术研发日:技术公布日:2024/11/14本文地址:https://www.jishuxx.com/zhuanli/20241118/330658.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。