半极性多量子阱垒外延结构及其制备方法、MicroLED芯片与流程

- 国知局

- 2024-11-21 12:22:22

本发明涉及半导体,尤其是一种半极性多量子阱垒外延结构及其制备方法、micro led芯片。

背景技术:

1、micro-led显示技术在超大屏直显、ar眼镜、微投影、车载矩阵大灯等新兴领域有广阔应用前景。然而,研究发现,当micro-led的像素(pixel)尺寸微缩到100µm(微米)左右时,就已经开始出现的外量子效率(external quantum efficiency)下降现象。当micro-led像素尺寸继续微缩,外量子效率的下降更加显著,这通常称为micro-led的侧壁效应。micro-led的侧壁效应主要源自于对gan侧壁刻蚀过程中产生的材料损伤和晶体缺陷,导致刻蚀区域所在的位置成为了高密度的非辐射复合中心。举例来说,1000µm尺寸的gan基蓝光led(功率led)芯片的峰值外量子效率可达85%以上,但5µm尺寸的gan基蓝光micro-led的峰值外量子效率仅为10%左右。侧壁效应导致的低光效问题对micro-led显示模组的亮度、功耗、可靠性等关键问题都带来严重的制约。

2、现有技术中,通常采用两种方式来降低micro-led的侧壁效应:一种是在对gan侧壁刻蚀之后进行侧壁修复和钝化,然而即使在侧壁修复和钝化后,5µm尺寸的gan基micro-led的峰值外量子效率也只能达到10%左右;另一种是选区外延,如中国专利202311624938.6(公开号cn117637930a),先在衬底或者gan层上沉积掩膜层(sio2、sinx、或者金属等),接着在掩膜层上光刻出微米级或者亚微米级开口,并直接在掩膜层的开口中生长出独立不相连的micro-led像素,由于选区外延的技术无需经过刻蚀直接制备出micro-led像素,从而明显提高了micro-led的外量子效率。但是,选区外延不仅增加了外延复杂度和成本,对micro-led的键合和电极制作等芯片工艺带来极大的困难,量产可行性很低。

技术实现思路

1、为了克服以上不足,本发明提供了一种半极性多量子阱垒外延结构及其制备方法、micro led芯片,利用在外延层中均匀分布的高密度六角锥形孔侧面形成量子阱垒,从而在外延结构中增强载流子局域化,抑制载流子向micro-led侧壁的运动,来减小micro-led侧壁效应。

2、本发明提供的技术方案为:

3、一方面,本发明提供了一种半极性多量子阱垒外延结构,包括:

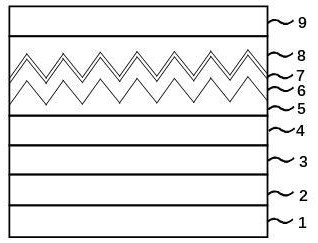

4、一种半极性多量子阱垒外延结构,包括:依次形成于生长衬底表面的成核层、位错分布控制层、n型gan电流扩展层、六角锥产生层、多量子阱垒层及p型电子阻挡层、p型gan电流扩展层、p型欧姆接触层;

5、所述六角锥产生层中形成有锥尖朝向n型gan电流扩展层的六角锥形孔,六角锥形孔的(0001)面呈六边形图案分布,且六角锥形孔密布在(0001)面上;

6、所述多量子阱垒层为半极性多量子阱垒层,且沿六角锥形孔内的半极性(1-101)侧面生长而成。

7、另一方面,本发明提供了一种半极性多量子阱垒外延结构的制备方法,包括以下步骤:依次在生长衬底表面生长成核层,位错分布控制层、n型gan电流扩展层、六角锥产生层、多量子阱垒层及p型电子阻挡层、p型gan电流扩展层、p型欧姆接触层;

8、生长所述六角锥产生层时,形成锥尖朝向n型gan电流扩展层的六角锥形孔,六角锥形孔的(0001)面呈六边形图案分布,且六角锥形孔密布在(0001)面上;

9、所述多量子阱垒层沿六角锥形孔内的半极性(1-101)侧面生长,形成半极性多量子阱垒层。

10、再一方面,本发明提供了一种micro led芯片,包括上述的半极性多量子阱垒外延结构,且所述半极性多量子阱垒外延结构被刻蚀为多个像素单元;以及第一电极和第二电极,所述第一电极与被刻蚀的半极性多量子阱垒外延结构中n型gan电流扩展层导电连接,所述第二电极与被刻蚀的半极性多量子阱垒外延结构中p型gan电流扩展层导电连接。

11、本发明提供的半极性多量子阱垒外延结构及其制备方法、micro led芯片,在外延结构中的六角锥产生层中形成有均匀分布的六角锥型孔,且六角锥形孔密布在(0001)面上,即六角锥产生层与多量子阱垒层相接触的表面呈现为连续紧密分布的下凹的六角锥形态,且相邻六角锥形孔的(0001)面存在间隙但间隙的占比很小以至间隙区域的发光可以忽略,或者相邻六角锥形孔的(0001)面共用六边形图案中的一个侧边或多个紧密连接在一起,接着,在均匀分布的六角锥形孔侧面形成半极性的多量子阱垒层,从而在外延结构中实现增强载流子局域化的效果来减小micro-led侧壁效应。

技术特征:1.一种半极性多量子阱垒外延结构,其特征在于,包括:依次形成于生长衬底表面的成核层、位错分布控制层、n型gan电流扩展层、六角锥产生层、多量子阱垒层及p型电子阻挡层、p型gan电流扩展层、p型欧姆接触层;

2.如权利要求1所述的半极性多量子阱垒外延结构,其特征在于,在n型gan电流扩展层与六角锥产生层之间,形成有掺si浓度大于3×1019/cm3的ngan插入层。

3.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,所述成核层为在1000℃-1100℃下形成的aln层,厚度为150nm-400nm。

4.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,

5.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,所述六角锥产生层中六角锥形孔的密度为7×108/cm2至1×109/cm2;所述六角锥形孔(0001)面的直径长度为350nm至500nm。

6.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,所述多量子阱垒层为inxalyga1-x-yn与inaalbga1-a-bn的周期性结构,且多量子阱垒结构的周期为1~10,其中0≦x≦1,0≦y≦1,0≦a≦1,0≦b≦1;单个inxalyga1-x-yn量子阱的厚度大于等于1nm且小于等于10nm,单个inaalbga1-a-bn量子垒层的厚度大于等于3nm且小于等于25nm。

7.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,p型电子阻挡层沿多量子阱垒层中形成的六角锥形孔内的半极性(1-101)侧面生长而成。

8.如权利要求1或2所述的半极性多量子阱垒外延结构,其特征在于,p型gan电流扩展层中,靠近p型欧姆接触层一侧具有平坦的表面。

9.一种半极性多量子阱垒外延结构的制备方法,其特征在于,包括以下步骤:依次在生长衬底表面生长成核层,位错分布控制层、n型gan电流扩展层、六角锥产生层、多量子阱垒层及p型电子阻挡层、p型gan电流扩展层、p型欧姆接触层;

10.如权利要求9所述的半极性多量子阱垒外延结构的制备方法,其特征在于,在生长n型gan电流扩展层之后、六角锥产生层之前,还包括生长掺si浓度大于3×1019/cm3的ngan插入层的步骤。

11.一种micro led芯片,其特征在于,包括如权利要求1-8中任一项所述的半极性多量子阱垒外延结构,且所述半极性多量子阱垒外延结构被刻蚀为多个像素单元;以及第一电极和第二电极,所述第一电极与被刻蚀的半极性多量子阱垒外延结构中n型gan电流扩展层导电连接,所述第二电极与被刻蚀的半极性多量子阱垒外延结构中p型gan电流扩展层导电连接。

技术总结本发明提供了一种半极性多量子阱垒外延结构及其制备方法、Micro LED芯片,在半极性多量子阱垒外延结构的六角锥产生层中,形成有锥尖朝向n型GaN电流扩展层的六角锥形孔,六角锥形孔的(0001)面呈六边形图案分布,六角锥形孔密布在(0001)面上;多量子阱垒层为半极性多量子阱垒层,且沿六角锥形孔内的半极性(1‑101)侧面生长而成。在外延结构中生长量子阱之前先制备表面为连续紧密分布的六角锥形态的六角锥产生层,并在均匀分布的六角锥孔侧面形成半极性多量子阱垒层,达到载流子局域化增强的效果来减小Micro‑LED侧壁效应。技术研发人员:付羿受保护的技术使用者:晶能光电股份有限公司技术研发日:技术公布日:2024/11/18本文地址:https://www.jishuxx.com/zhuanli/20241120/335258.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表