一种多端口多优先级的路由器数据包缓存管理调度系统

- 国知局

- 2024-11-25 14:59:17

本发明属于集成电路领域,具体涉及一种多端口多优先级的路由器数据包缓存管理调度系统。

背景技术:

1、随着信息技术的高速发展,信息社会的不断深化,互联网的信息量呈爆炸式增长,每一个网络终端对网络带宽的要求日益提高,于是对路由器等网络设备数据存储转发能力提出了更高的要求。而在网络设备对数据包的处理中,存储管理、调度占去了大部分时间,因此大多数存储器的低速缓存能力成为了限制网络处理器进一步提高的瓶颈。

2、传统的静态缓存技术为每一个优先级队列划分了固定的缓存空间,这样可以使得每一个端口的读写带宽得到充分的利用,但是实际应用中不同优先级的数据包一般是不均匀的,所以就会存在一些优先级队列的缓存空间已经满了,而另一些优先级队列的缓存空间还空着的情况,这样的话缓存空间就会存在较大的浪费。

3、为了充分利用缓存空间,动态缓存的技术得到了广泛应用,即不同优先级队列共用一个缓存空间;然而这个缓存空间存在一个问题,实际应用中数据包的长度并不是固定的,可以在一定范围内变动,所以使得数据包单位无法很好的确定:如果太大,缓存空间依然会存在较大的浪费,动态调度失去了意义;如果太小,则对动态缓存空间的调度代价会很大,严重制约整个系统的功耗以及带宽;而当前复杂的调度策略使得调度速度成为了带宽进一步提升的瓶颈。

技术实现思路

1、针对上述存在的问题或不足,为解决传统路由器缓存空间因利用率较低、调度代价大导致带宽上不去的问题,本发明提供了一种多端口多优先级的路由器数据包缓存管理调度系统,为专用集成电路,使用静态随机存储器作为存储介质,有m个输入端口和n个输出端口,数据包可以从任意输入端口向任意输出端口输出;其数据包有p个优先级,长度介于64字节和1024字节之间;使用轻量化的链表设计来调度地址资源,地址资源动态调度的最小单位s为64字节,每个数据帧位宽w为32比特。本发明将调度单位和数据单位分开处理,使用了更为轻量化的链表管理策略,在保证完全动态调度的前提下,使得调度速度大幅提升。

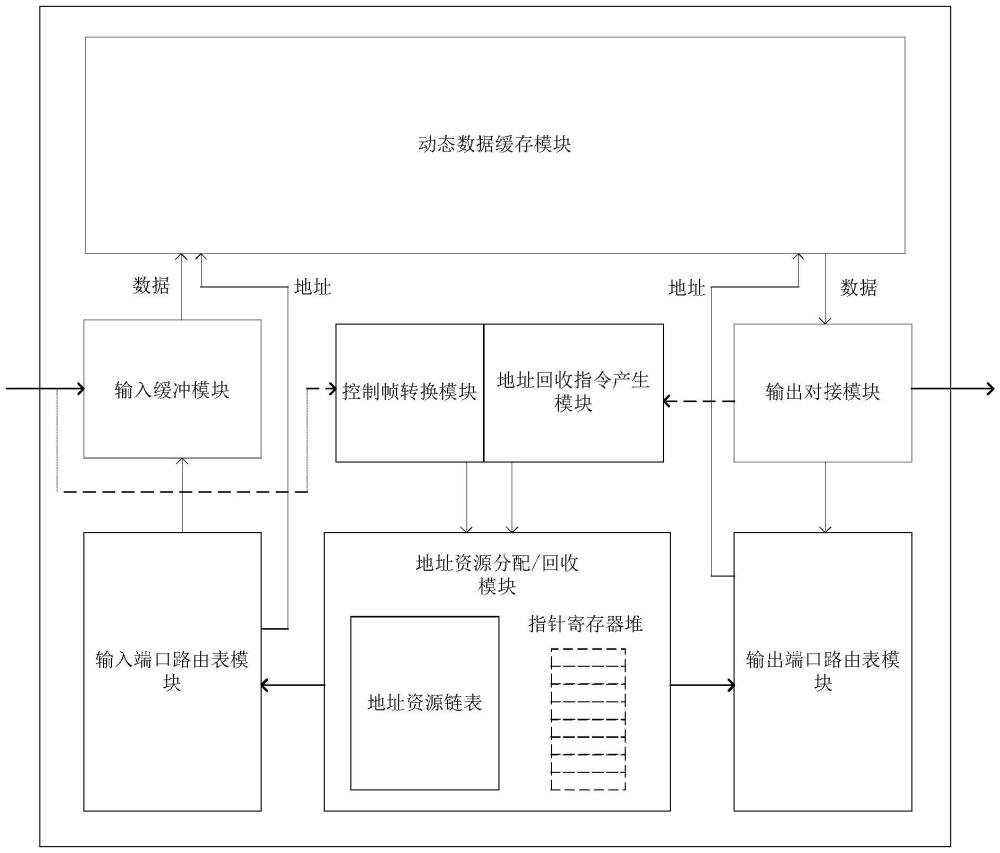

2、一种多端口多优先级的路由器数据包缓存管理调度系统,包括输入缓冲模块,控制帧转换模块,地址回收指令产生模块,地址资源分配/回收模块,输入端口路由表模块,输出端口路由表模块,输出对接模块和动态数据缓存模块。

3、所述输入缓冲模块有m个输入端口,为整个系统的输入端口,用于接收并缓冲外界的输入数据,因为地址资源的分配需要一定的时间,所以需要一定深度的fifo(先入先出队列)来暂存数据,如果时钟频率为250mhz时要求每端口带宽达到1gbps,那么这个fifo的深度至少为4m,宽度为32比特。其输出端接动态数据缓存模块,共有m个输出端口,当输入端口路由表模块产生有效地址时,从输入缓冲模块中读出数据,与有效地址一起写入动态数据缓存模块,另外将fifo的满信号连接到外界的数据提供方,实现输入数据的流量控制。

4、所述控制帧转换模块一端接外界的输入数据,有m个输入端口以及每个端口一一对应的1组寄存器,1组寄存器包含0级和1级寄存器;其输出端口接地址资源分配/回收模块,通过侦听外界的输入数据,获得输入数据中所有的控制帧,然后根据控制帧的数据包信息进行优先级轮询仲裁,到达的控制帧中,优先级最高的控制帧之一仲裁成功,其余控制帧为仲裁失败,仲裁失败的控制帧将会等待下一轮仲裁。

5、进一步的,所述仲裁成功的控制帧,为优先级最高的控制帧中端口数最高的控制帧,以保证地址资源分配的序列化。

6、进一步的,所述控制帧转换模块的仲裁机制为:(1)首先将控制帧数据写入m组本级寄存器(0级)中的对应位置,并将其有效位拉高,表示该控制帧有效;(2)当本级寄存器(0级)中控制帧有效,而下一级寄存器(1级)中对应位置无效,并且控制帧的优先级与备选优先级相同,那么将该控制帧从0级寄存器写入1级寄存器,即0级寄存器对应位置有效位拉低,而1级寄存器有效位拉高;(3)当待执行的分配指令寄存器为空时,将1级寄存器中最高位的有效控制帧变成地址分配指令,并将该控制帧在本级寄存器无效,直到1级寄存器没有控制帧;(4)当地址资源分配/回收模块允许接收分配指令,而且待执行的分配指令寄存器不为空时,将分配指令发到地址资源分配/回收模块;(5)当且仅当0级寄存器中有控制帧而1级寄存器中没有控制帧时,备选优先级置为0,其余情况则加1,备选优先级在0与p-1中循环计数,p为优先级数量。

7、所述地址回收指令产生模块包括n个输出端口,以及一一对应的n组回收指令状态寄存器,初始化为0;用于产生地址回收指令,为了正确的生成地址回收指令,该模块侦听地址资源分配/回收模块的指针寄存器堆中队列的空满情况以及输出对接模块中实际输出的数据,通过轮询的方式决定某一个时钟周期生成某一个输出端口的地址回收指令,在地址资源分配/回收模块允许接收地址回收指令时将地址回收指令发出。

8、进一步的,所述地址回收指令产生模块生成的地址回收指令有两种:

9、一种是起始地址资源回收指令,首先该模块中存在n组回收指令状态寄存器,对应n个输出端口,初始化为0,该模块会先轮询对应不同输出端口的回收指令状态寄存器的信息,如果空闲(即为0)则会根据绝对优先级仲裁或者是权重轮询优先级仲裁选择该输出端口对应的有数据包的某个优先级的数据包队列,然后会固定产生一个回收单个地址资源(即64字节)的回收指令,同时将此输出端口的回收指令状态寄存器置为忙碌。

10、另一种是补充地址资源回收指令,根据其侦听到的输出对接模块的实际数据输出,当侦听到有数据包的控制帧输出时,就根据其长度信息形成一个回收其实际长度减一个地址资源的回收指令,如果这个数据包长度就是一个地址资源,即起始地址资源回收指令已经将该数据包占用的空间完全回收,那么就不会产生补充地址资源回收指令;而当侦听到输出对接模块输出的数据为结尾帧时,将对应输出端口的回收指令状态寄存器重新置为空闲。上述产生的地址回收指令将在地址资源分配/回收模块允许接收回收指令时发给地址资源分配/回收模块。

11、所述地址资源分配/回收模块用于地址资源的分配和回收,与控制帧转换模块和地址回收指令产生模块连接,接收上两个模块的分配和回收指令,存入一个指令fifo,依次进行地址资源的分配或者回收;因为分配和回收指令可能会同时到来,所以这两种指令谁先进入指令fifo存在优先级,本模块中这个优先级轮流切换,初始化时分配指令优先级更高,存入一个分配指令后,回收指令优先级变得更高,而存入一个回收指令后,分配指令优先级变得更高,让分配和回收的指令尽量均衡的执行,当指令fifo满时,分配和回收指令都不允许接收;地址资源分配/回收模块还连接输入端口路由表模块和输出端口路由表模块,负责接收分配的地址资源和回收的地址资源,其中地址分配事件分配出的地址资源写入输入端口路由表模块,而地址回收事件回收到的地址资源写入输出端口路由表模块。

12、进一步的,所述地址资源分配/回收模块有一个存放地址资源链表的存储器,以及代表n个输出端口p个优先级总共n*p组不同队列用以读写的指针寄存器堆(dxry表示读指针,dxwy表示写指针,其中x表示输出端口,y表示优先级,例如代表输出端口为0,优先级为1的指针寄存器为d0w1和d0r1)、空链表头指针pems和尾指针peme。地址资源链表存储器的深度为2k(2k=动态数据缓存模块的存储空间/64字节),位宽为k,地址资源链表中每个地址中存储的数据为下一个节点的地址,在初始化时将地址加一的值写入当前地址。指针寄存器堆以目的地输出端口为准分为n组,每个目的地端口对应其p个优先级有p套优先级读和写的指针(例如目的地端口0的优先级0的读写指针寄存器分别是d0r0和d0w0),即一共有n*p个队列,n*p*2+2组寄存器,当读写指针指向同一个地址,则代表该队列为空,例如d0r0等于d0w0的时候就代表目的地端口为0,优先级为0的数据包当前不存在;当空链表头指针和尾指针指向同一个地址则链表已满,即地址资源已经被分配完。这些指针寄存器指向地址资源链表,位宽均为k;初始化时将一块连续的链表地址依次赋值给不同队列的读写指针,同一个队列的读写指针相同,而空链表头指针和尾指针则分别被赋值为链表剩余地址的头地址和尾地址,例如0赋值给d0r0和d0w0,1赋值给d0r1和d0w1,(n*p-1)赋值给d(n-1)r(p-1)和d(n-1)w(p-1),n*p赋值给pems,2k-1赋值给peme。

13、举例说明地址分配事件和地址回收事件,假设此时的写入数据包的目的地端口是0,优先级是1,长度是1个地址资源,来源输入端口是2,具体地址分配过程为:

14、(1)将d0w1寄存器的值分配出去,作为被分配的地址资源写入输入端口路由表模块对应的fifo(即输入端口路由表中对应输入端口2的地址资源fifo);(2)将pems寄存器的值写入d0w1寄存器和d0w1寄存器之前指向的地址,也就是说d0w1原先指向的地址1存的值将会从2变成n*p,而d0w1寄存器的值会从1变成n*p;(3)将pems寄存器指向的地址中的值读出,写入pems寄存器,也就是说从pems指向的地址n*p中读出n*p+1,然后将n*p+1写入pems寄存器;此时地址分配事件完成。

15、地址分配事件完成后,地址回收指令产生模块侦听到目的地端口为0的p组读写指针寄存器中存在读写指针不相同的寄存器,即有数据可以发出,于是就可以产生地址回收指令,发起地址回收,并读出数据,具体过程如下:

16、(1)将d0r1寄存器的值(地址1)读出作为后续模块的读出地址(即发送到输出端口路由表模块对应的输出端口0的fifo),将这个值写入peme寄存器指向的地址,以及peme寄存器本身,也就是说,将peme指向的地址2k-1内的值从0变成1,然后将peme寄存器的值从2k-1变成1;(2)将d0r1寄存器指向的地址的值读出,写入d0r1寄存器,也就是将读出n*p,然后d0r1的值从1变成n*p,至此地址回收事件完成;分配或者回收一个地址资源都只需要2个时钟周期。

17、地址资源的分配和回收指令长度为5+log2(mnp)比特,比特4+log2(mnp)表示地址资源分配或者回收,比特3+log2(mnp)到4+log2(np)表示来源端口,比特3+log2(np)到log2(np)表示长度,比特log2(np)-1到log2(n)表示优先级,比特log2(n)-1到0表示目的地端口。

18、所述输入端口路由表模块存在m个深度为16的地址资源fifo,负责接收分配的地址资源,并侦听输入缓冲模块中对应端口的数据fifo的空满信号;如果对应端口的数据fifo非空,则尝试从本模块对应端口的地址资源fifo中获取一个有效的地址资源,然后将这个有效的地址资源拼接地址偏移(如果数据帧为32比特,地址资源为64字节,在250mhz的时钟频率,1gbps的端口带宽的要求下,地址偏移就有log2(128/m)比特)成为一个有效地址,然后从输入缓冲模块中对应的数据fifo中连续取出m/8个数据,此时便形成一个有效的地址数据对,如果没有取够m/8个数据就取到了结尾帧,那么视为已经取够了数据。该模块同时最多可能存在m个有效的地址数据对,此时使用循环优先级仲裁器来进行仲裁,仲裁成功的有效的地址数据对写入动态数据缓存模块,仲裁失败的有效地址数据对则等待下一次仲裁。仲裁成功的有效地址数据对被写入动态数据缓存模块后,地址偏移加一,重新取出数据形成新的地址数据对,直到地址偏移完毕,即地址偏移位从全0偏移到来全1,此时这个地址资源失效,尝试从相应的地址资源fifo中取出地址资源重复上述过程。

19、所述输出端口路由表模块存在n个深度为16的地址资源fifo,负责接收回收的地址资源,产生有效的回收地址,从动态数据缓存模块中取出数据。输出端口路由表模块有一个读写保护锁,如果侦听输出对接模块中对应端口的状态为空闲,则尝试从本模块中对应端口的地址资源fifo中获取地址资源,作为有效的地址资源,然后将这个地址资源与输入端口路由表模块中的有效的地址资源对比,如果存在相同的地址资源,则等待,直到输入端口路由表模块中不存在相同的有效地址资源,再拼接上地址偏移成为一个有效地址(如果数据帧为32比特,地址资源为64字节,在250mhz的时钟频率,1gbps的端口带宽的要求下,那么地址偏移就有log2(128/n)比特);此时可能存在最多n个有效地址,对这些有效地址进行循环优先级仲裁,使用仲裁成功的有效地址从动态数据缓存模块中读出相应数据,放到输出对接模块的对应端口,并将该端口的状态变为忙碌,直到这个数据被外界读出,该端口的状态变回空闲,依次偏移,直到该地址资源偏移完毕,即地址偏移位从全0偏移到来全1,此时这个地址资源失效,侦听输出对接模块中对应端口的状态,尝试从相应的地址资源fifo中取出地址资源重复上述过程。

20、所述输出对接模块有n个用于数据缓存的寄存器,负责暂时存放从动态数据缓存模块读出的各个输出端口的数据,根据外界状态将数据输出。

21、所述动态数据缓存模块为静态随机存储器构成,与输入缓冲模块、输入端口路由表模块、输出对接模块、输出端口路由表模块连接,作为统一的数据缓存空间。

22、综上所述,本发明涉及专用集成电路,使用静态随机存储器作为存储介质,将调度单位和数据单位分开处理;其数据包有p个优先级,长度介于64字节和1024字节之间,每个数据包的第一帧(控制帧)包含这个数据包的长度、优先级和目的地端口信息,最后一帧(结尾帧)包含该数据包结束的信息,中间数据帧无特殊信息;数据包调度支持绝对优先级和权重轮询优先级,调度速度可达s/2字节每时钟周期,在250mhz的时钟频率下,每个端口的带宽可自适应调节,只需满足总带宽小于sgbps;使用轻量化的链表设计来调度地址资源,摒弃了传统链表的增删遍历功能,仅保留链表的连接功能,将队列的读写分开通过两套链表管理,剩余空间单独使用一套链表来管理,在较小的逻辑复杂度下实现了多队列共用一个缓存空间的效果,同时保证了较高的调度速度。

本文地址:https://www.jishuxx.com/zhuanli/20241125/335599.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。