一种小数分频补偿方法及全数字锁相环与流程

- 国知局

- 2024-12-06 12:10:27

本发明属于全数字锁相环,尤其涉及一种小数分频补偿方法及全数字锁相环。

背景技术:

1、全数字锁相环adpll是一种在数字电路中实现的锁相环,能够使输出信号与输入参考信号保持同步。

2、传统的全数字锁相环在实现小数分频时,通常依靠数字时间转换器dtc去调整参考时钟ckv实现。例如公开号为cn104506190b的中国专利公开了数字小数分频锁相环控制方法及锁相环,其通过控制装置根据当前的频率控制字和分频控制字对参考时钟进行延迟处理,使得反馈时钟与延迟参考时钟具有相近的有效沿对应时间,从而tdc仅需要处理很小时域输入范围的鉴相信号,大大降低了tdc的设计难度及对tdc分辨率的需求,使得tdc的设计简单、自由,从而保证了锁相环的设计自由度以及简单有效。

3、但是,若仅依靠数字时间转换器dtc去调整参考时钟以实现小数分频时,数字时间转换器dtc会直接影响全数字锁相环小数分频时钟的性能,对数字时间转换器dtc的线性度、精度及链长的要求极其严格,导致dtc的设计难度或成本过高。

4、故此亟需开发一种小数分频补偿方法及全数字锁相环来解决现有技术中的问题。

技术实现思路

1、本发明目的在于提供一种小数分频补偿方法及全数字锁相环,可以降低对数字时间转换器dtc的线性度、精度及链长的要求,以解决上述背景技术中提出的具备小数分频功能的全数字锁相环的数字时间转换器dtc的设计难度或成本过高问题。

2、为解决上述技术问题,本发明的具体技术方案如下:

3、一种小数分频补偿方法,应用于全数字锁相环,所述全数字锁相环包括时间数字转换器tdc、鉴相器pd和数字时间转换器dtc,所述小数分频补偿方法包括如下步骤:

4、获取延迟值nr,所述延迟值nr为时间数字转换器识别得到的输出时钟上升沿与参考时钟上升沿之间的延迟值;

5、获取小数频率控制字累加和σfcw_frac;所述小数频率控制字累加和σfcw_frac为频率控制字累加和σfcw的小数部分;

6、根据延迟值nr及小数频率控制字累加和σfcw_frac,预测第一小数补偿控制字x_int,并发送预测结果至鉴相器;

7、根据小数频率控制字累加和σfcw_frac,得到剩余补偿信息,并将剩余补偿信息发送至数字时间转换器,以使数字时间转换器处理剩余补偿信息。

8、所述延迟值nr持续获取,当时间数字转换器得到的延迟值nr与第一小数补偿控制字x_int在数值上相等时,锁相环锁定。

9、本申请的小数分频补偿方法,通过利用时间数字转换器tdc覆盖整个输出时钟信号周期,以实现第一小数补偿控制字x_int的预测,并通过数字时间转换器dtc覆盖时间数字转换器tdc,使得数字时间转换器dtc仅需处理所述小数频率控制字累加和σfcw_frac被第一小数补偿控制字x_int预测后的剩余部分,避开了利用dtc覆盖整个输出时钟信号周期而导致dtc链长过长,线性度无法得到保证的弊端,以降低对数字时间转换器dtc的线性度、精度及链长的要求,降低了数字时间转换器dtc的设计难度和成本。

10、进一步,所述的根据延迟值及小数频率控制字累加和,预测第一小数补偿控制字,包括如下步骤:

11、获取输出时钟周期值;

12、根据输出时钟周期值与小数频率控制字累加和,得到第一小数补偿控制字;

13、当获取的延迟值与第一小数补偿控制字在数值上相等时,全数字锁相环锁定。

14、进一步,所述第一小数补偿控制字包括:小数频率控制字累加和的十分位与输出时钟周期值的乘积;或小数频率控制字累加和的十分位及百分位与输出时钟周期值的乘积。

15、进一步,所述预测结果为第一小数补偿控制字与输出时钟周期值的比值。

16、一种全数字锁相环,应用小数分频补偿方法,包括参考相位累加器、鉴相器、数字滤波器、数控振荡器、可变相位累加器、数字时间转换器、时间数字转换器以及小数分频补偿单元;

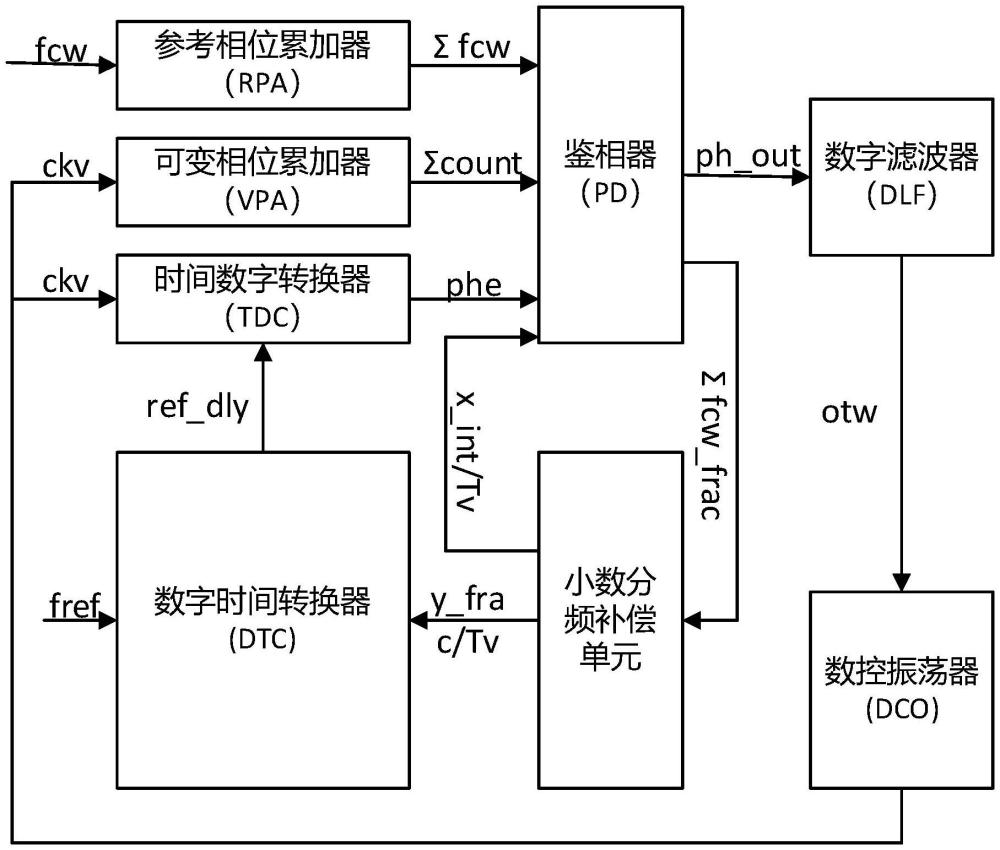

17、所述参考相位累加器的输出端与所述鉴相器的第一输入端连接;所述鉴相器的第一输出端与所述数字滤波器的输入端连接;所述数字滤波器的输出端与所述数控振荡器的输入端连接;所述数控振荡器的第一输出端与所述可变相位累加器的输入端连接;所述数控振荡器的第二输出端与所述时间数字转换器的第一输入端连接;所述可变相位累加器的输出端与所述鉴相器的第二输入端连接;所述时间数字转换器的输出端与所述鉴相器的第三输入端连接;

18、所述鉴相器的第二输出端与所述小数分频补偿单元的输入端连接,所述小数分频补偿单元的第一输出端与所述鉴相器的第四输入端连接,所述小数分频补偿单元的第二输出端与所述时间数字转换器的第一输入端连接,所述时间数字转换器的输出端与所述时间数字转换器的第二输入端连接;

19、所述小数分频补偿单元用于根据延迟值及小数频率控制字累加和,预测第一小数控制字,并发送预测结果至鉴相器;以及根据小数频率控制字累加和,得到剩余补偿信息,并将剩余补偿信息发送至数字时间转换器,以使数字时间转换器处理剩余补偿信息;其中,所述延迟值为时间数字转换器识别得到的输出时钟上升沿与参考时钟上升沿之间的延迟值;所述小数频率控制字累加和为频率控制字累加和的小数部分。

20、本申请提供了一种小全数字锁相环,通过利用小数分频补偿单元,以实现通过时间数字转换器tdc覆盖整个输出时钟信号周期,实现第一小数补偿控制字x_int的预测,并通过数字时间转换器dtc覆盖时间数字转换器tdc,使得数字时间转换器dtc仅需处理所述小数频率控制字累加和σfcw_frac被第一小数补偿控制字x_int预测后的剩余部分,避开了利用dtc覆盖整个输出时钟信号周期而导致dtc链长过长,线性度无法得到保证的弊端,以降低对数字时间转换器dtc的线性度、精度及链长的要求。

21、进一步,所述第一小数控制字通过如下公式表示:

22、σfcw_frac*tv=x_int+y_frac;

23、其中,σfcw_frac为小数频率控制字累加和,tv为输出时钟周期值,x_int为第一小数补偿控制字,y_frac为第二小数补偿控制字。

24、进一步,所述预测结果通过如下公式表示:

25、x_int/tv;

26、其中,x_int为第一小数补偿控制字,nr为延迟值,tv为输出时钟周期值。

27、进一步,所述剩余补偿信息通过如下公式表示:

28、y_frac/tv;

29、其中,y_frac为第二小数补偿控制字,tv为输出时钟周期值。

30、本发明的其他特点和优点将会在下面的具体实施方式、附图中详细的揭露。

技术特征:1.一种小数分频补偿方法,其特征在于,应用于全数字锁相环,所述全数字锁相环包括时间数字转换器、鉴相器和数字时间转换器,包括如下步骤:

2.根据权利要求1所述的小数分频补偿方法,其特征在于,所述的根据延迟值及小数频率控制字累加和,预测第一小数补偿控制字,包括如下步骤:

3.根据权利要求2所述的小数分频补偿方法,其特征在于,所述第一小数补偿控制字包括:小数频率控制字累加和的十分位与输出时钟周期值的乘积,或小数频率控制字累加和的十分位及百分位与输出时钟周期值的乘积。

4.根据权利要求2所述的小数分频补偿方法,其特征在于,所述预测结果通过如下公式表示:

5.一种全数字锁相环,其特征在于,包括参考相位累加器、鉴相器、数字滤波器、数控振荡器、可变相位累加器、数字时间转换器、时间数字转换器以及小数分频补偿单元;

6.根据权利要求5所述的全数字锁相环,其特征在于,所述第一小数控制字通过如下公式表示:

7.根据权利要求6所述的全数字锁相环,其特征在于,所述预测结果通过如下公式表示:

8.根据权利要求6所述的全数字锁相环,其特征在于,所述剩余补偿信息通过如下公式表示:

技术总结一种小数分频补偿方法及全数字锁相环,属于锁相环技术领域,一种小数分频补偿方法,包括如下步骤:获取延迟值,所述延迟值为时间数字转换器识别得到的输出时钟上升沿与参考时钟上升沿之间的延迟值;获取小数频率控制字累加和,所述小数频率控制字累加和为频率控制字累加和的小数部分;根据延迟值及小数频率控制字累加和,预测第一小数补偿控制字,并发送预测结果至鉴相器;根据小数频率控制字累加和,得到剩余补偿信息,并将剩余补偿信息发送至数字时间转换器,以使数字时间转换器处理剩余补偿信息。本申请通过小数分频补偿方法,可以降低对数字时间转换器的线性度、精度及链长的要求,以降低了数字时间转换器的设计难度和成本。技术研发人员:刘芮伯受保护的技术使用者:北京晶芯微科技有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/339759.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。