一种内置混合型体二极管的SiCMOSFET及制备方法与流程

- 国知局

- 2024-12-06 12:14:54

本发明涉及半导体,尤其涉及一种内置混合型体二极管的sic mosfet及制备方法。

背景技术:

1、在现在的节能减排社会大环境下,电能的转化和传输相较于传统化石能源更为方便,更符合当下社会形式。但是随着电力电子系统向着更大电压高功率方向发展,传统si基功率器件的性能已接近材料的理论极限,很难满足更为严苛工况下的使用条件。与传统的si材料相比, sic材料由于禁带宽度大、临界击穿电场高、本征载流子浓度小、饱和漂移速度快、熔点高、热导率高等一系列特性优势,使得其在高压、高温、高频等应用领域具有很大的优势,在未来的新能源汽车、光伏储能、充电桩等领域具有很大应用前景。

2、sic mosfet器件是sic功率器件的核心产品,其同时兼具优异的导通特性和开关特性,因此在大功率领域可以直接替代siigbt器件。并且sic mosfet内部通常会寄生pn结体二极管以实现对器件的续流保护,此设计相比于si igbt器件额外反并联续流二极管方法,减少了二极管的器件用量,降低了成本。但是sic mosfet内部的pn结体二极管也存在一定风险,在续流过程中,pn结体二极管的工作会使p区空穴进入到sic drift层中使得空穴与电子发生复合现象,从而引起sic drift层中的晶格缺陷蔓延,恶化器件性能,这一现象被称为双极退化效应,对于器件的长期使用具有很大风险。因此如何改善sicmosfet的双极退化效应对于器件的性能稳定和长期使用具有很大影响。

技术实现思路

1、针对以上问题,本发明提供了一种在is续流过程时,避免了空穴进入到sic drift层中发生双极退化效应;经issm大浪涌电流时,提高器件承受大浪涌电流冲击能力的一种内置混合型体二极管的sic mosfet及制备方法。

2、本发明的技术方案是:

3、一种内置混合型体二极管的sic mosfet制备方法,包括如下步骤:

4、s100,在sic sub层顶面依次沉积sic drift层和csl层;

5、s200,在 csl层的顶面制备肖特基接触层,使sic mosfet内部形成sbd体二极管;

6、s300,在csl层和肖特基接触层的顶面沉积p-body层,并在p-body层上通过离子注入形成重掺杂的p+区;

7、s400,在p-body层的顶面通过外延沉积一层np层;

8、s500,在肖特基接触层的顶面形成第一欧姆接触层;

9、s600,在np层的顶面刻蚀形成延伸至sic drift层内的沟槽,并在沟槽底部通过离子注入形成屏蔽电场的重掺杂的p-shield区,沟槽内形成一层栅氧化层;

10、s700,在栅氧化层内形成poly层;

11、s800,在poly层上形成隔离sic mosfet的栅电极和源电极的隔离介质层;

12、s900,在器件的顶面依次形成第二欧姆接触层和正面电极金属层。

13、具体的,步骤s100中的sic sub层掺杂浓度为1e19cm-2,sic drift层的掺杂浓度为1e15-5e16cm-2。

14、具体的,步骤s100中的csl层的掺杂浓度为1e17-5e18cm-2。

15、具体的,步骤s300中的p-body层掺杂浓度为1e17-5e18cm-2。

16、具体的,步骤s300中的p+区掺杂浓度为1e18-5e19cm-2。

17、具体的,步骤s400中的np层掺杂浓度为1e17-5e18cm-2。

18、具体的,步骤s600中的沟槽底面深度距离csl层底面深度为0.3um-1.2um。

19、具体的,步骤s600中的p-shield区掺杂浓度为1e18-5e19cm-2。

20、具体的,步骤s700中的栅氧化层厚度为30nm-80nm。

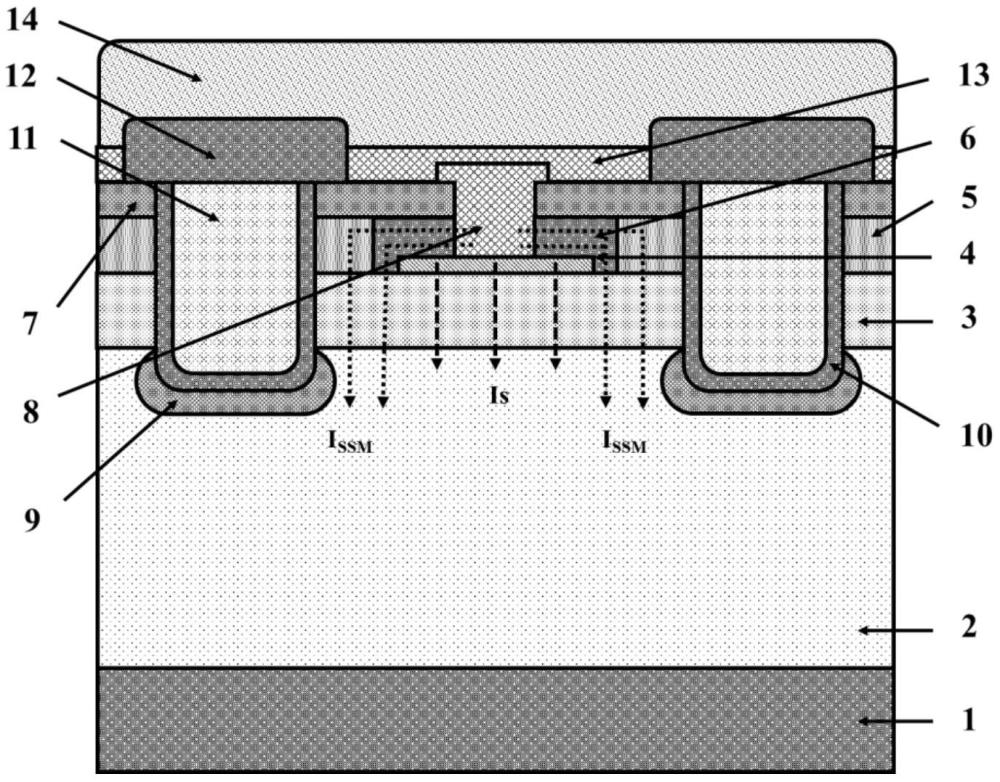

21、一种内置混合型体二极管的sic mosfet,包括从下而上设置的sic sub层、sicdrift层、csl层、第二欧姆接触层和正面电极金属层;

22、所述csl层的顶面设有:

23、肖特基接触层,形成于所述csl层的顶面中部位置;

24、p-body层,沉积在所述csl层的顶面;

25、p+区,形成于所述csl层的顶面,并与所述p-body层和肖特基接触层连接;所述p+区延伸至肖特基接触层的顶面;

26、np层,沉积在所述p-body层和p+区的顶面;

27、第一欧姆接触层,形成于所述肖特基接触层上,侧部与所述np层和p+区连接,顶面位于所述np层的上方;

28、p-shield区,设置在所述csl层的下方,用于屏蔽电场,保护栅氧化层;

29、栅氧化层,截面呈u形结构,从所述np层的顶面向下延伸,依次穿过所述np层、p-body层和csl层后,与所述p-shield区连接;

30、poly层,填充在所述栅氧化层内;隔离介质层,沉积在所述poly层上,用于隔离sicmosfet的栅电极和源电极,底面分别与所述np层、栅氧化层和poly层连接。

31、本发明有益效果:

32、1、降低器件的双极退化效应,提高器件的长期使用稳定性:

33、sic mosfet器件由于内部通常会寄生pn结体二极管,因此实现了对器件的续流保护。但是pn结体二极管在使用过程中,会容易发生p区空穴进入到sic drift层中从而发生空穴与电子的复合,导致sic drift层中的晶格缺陷蔓延,恶化器件性能,这一现象被称为sic mosfet的双极退化效应。本发明通过在沟槽sic mosfet器件内部集成混合型体二极管,即sbd二极管和pn结二极管,在is续流过程中,sbd二极管作为泄流路径开启,从而避免了双极退化效应的发生,提高了器件在长期使用中的性能稳定。

34、2、提高器件的抗浪涌电流冲击能力:

35、在系统电路的开关过程中通常会产生浪涌电流,因此功率器件都需要具备一定的抗浪涌电流冲击能力才能确保器件不被损坏。本发明在沟槽sic mosfet内部集成混合型体二极管,即sbd二极管和pn结二极管,由于pn结二极管在器件内部制备了欧姆接触,因此在issm大浪涌电流冲击下,pn结二极管作为泄流路径开启,使得器件的泄流路径从原本单一的sbd二极管变为了sbd和pn结二极管,因此提高了器件的抗浪涌电流冲击能力。

技术特征:1.一种内置混合型体二极管的sic mosfet制备方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s100中的sic sub层(1)掺杂浓度为1e19cm-2,sic drift层(2)的掺杂浓度为1e15-5e16cm-2。

3.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s100中的csl层(3)的掺杂浓度为1e17-5e18cm-2。

4.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s300中的p-body层(5)掺杂浓度为1e17-5e18cm-2。

5.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s300中的p+区(6)掺杂浓度为1e18-5e19cm-2。

6.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s400中的np层(7)掺杂浓度为1e17-5e18cm-2。

7.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s600中的沟槽底面深度距离csl层(3)底面深度为0.3um-1.2um。

8.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s600中的p-shield区(9)掺杂浓度为1e18-5e19cm-2。

9.根据权利要求1所述的一种内置混合型体二极管的sic mosfet制备方法,其特征在于,步骤s700中的栅氧化层(10)厚度为30nm-80nm。

10.一种内置混合型体二极管的sic mosfet,通过权利要求任一1-9所述的一种内置混合型体二极管的sic mosfet制备方法制备,其特征在于,包括从下而上设置的sic sub层(1)、sic drift层(2)、csl层(3)、第二欧姆接触层(13)和正面电极金属层(14);

技术总结一种内置混合型体二极管的SiC MOSFE及制备方法,涉及半导体技术领域。本发明在沟槽栅SiC MOSFET器件内部集成SBD二极管和PN结二极管,形成混合型体二极管,实现了对器件长期稳定使用的改善。在Is续流过程中,SBD体二极管作为续流管先行开启,避免了空穴进入到SiC Drift层中发生双极退化效应;在器件经Issm大浪涌电流时,PN结体二极管开启,从而提高了器件承受大浪涌电流冲击能力。技术研发人员:王正,杨程,裘俊庆,王毅受保护的技术使用者:扬州扬杰电子科技股份有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/340203.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表