一种结合HK集电极栅的SJ-LIGBT器件结构

- 国知局

- 2024-12-06 12:14:45

本发明涉及半导体,尤其涉及一种结合hk集电极栅的sj-ligbt器件结构。

背景技术:

1、绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)可近似看作为金属氧化物半导体型场效应管(metal oxide semiconductor field effecttransistor,mosfet)与双极性结型晶体管(bipolar junction transistor,bjt)的组合,因此同时具有mosfet的栅压控制的特点与bjt的双载流子导电的特点。其中,横向绝缘栅双极性晶体管(lateral insulated gate bipolar transistor,ligbt)是一种双极性功率半导体器件,具有击穿电压大,导通压降小,工作频率高等特点,广泛应用于交通,通信等各类电子领域。超级结(super-junction,sj)是一种可应用于mos、igbt等器件中的新兴结构。sj将mos与igbt中的n型漂移区变更为n-pillar与p-pillar相互交替的结构,在不影响器件纵向电场的前提下在器件内部引入了横向电场,从而在不影响导通压降的前提下增加器件的击穿电压,当器件关断时,n-pillar与p-pillar相互耗尽,器件漂移区可近似看作本征半导体,从而提高器件的击穿电压,将击穿电压与导通压降的比例从2.52优化至1.3,成功突破了传统的“硅极限”。

2、为了使n型漂移区完全耗尽从而达到最大的击穿电压,n-pillar与p-pillar往往需要具有相同的掺杂浓度。但是在ligbt中,由于衬底为低掺杂p型衬底,n-pillar与衬底之间存在寄生pn结,p型衬底使得n-pillar相比p-pillar先一步完全耗尽,使得p-pillar无法完全耗尽,导致器件击穿电压降低。另外,igbt为栅压控制功率器件,所以igbt击穿电压大,工作频率高,又因igbt为双载流子导电,所以igbt导通压降小。但是双极性导电也存在缺陷,当器件关断时,漂移区内残余的载流子会导致一定的拖尾电流,增大了器件的关断损耗。这是由于器件的集电极存在p区,在器件关断时会发挥势垒的作用阻碍电子的抽取,因此器件的n型漂移区内多余的载流子就需要通过复合消失,使得关断时间较长及产生拖尾电流,导致器件关断损耗大大增加。

技术实现思路

1、本发明实施例的目的是提供一种结合hk集电极栅的sj-ligbt器件结构,解决p-pillar无法完全耗尽导致器件击穿电压降低以及器件关断损耗大大增加的问题。

2、为解决上述技术问题,本发明实施例提供如下技术方案:

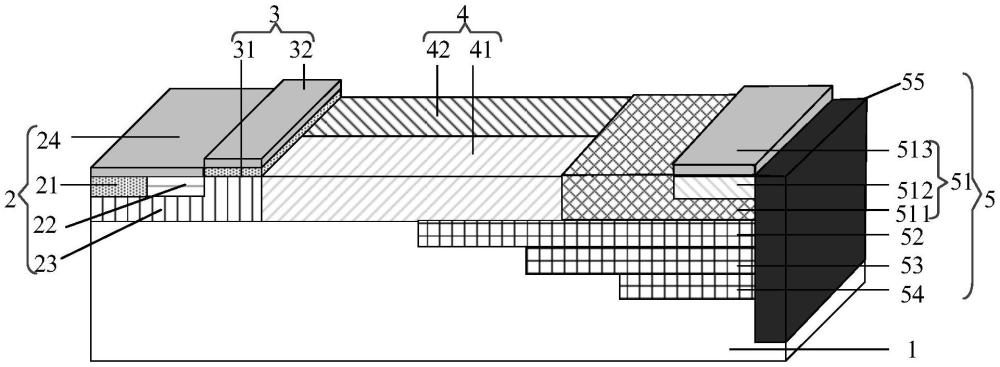

3、本发明提供一种结合hk集电极栅的sj-ligbt器件结构,包括p型衬底区、发射极结构、栅极结构、漂移区结构和集电极结构;

4、发射极结构,形成于p型衬底区的上表面的一侧;

5、栅极结构,形成于发射极结构的上表面的另一侧,且部分集电极结构被发射极结构包裹;

6、漂移区结构,形成于p型衬底区的上表面的中间区域,且漂移区结构与发射极结构相邻;

7、集电极结构,形成于p型衬底区的上表面的另一侧,并从p型衬底区的上表面延伸至p型衬底区内,且集电极结构包裹部分漂移区结构;集电极结构包括第一集电极、第一n-bufferlayer区、第二n-bufferlayer区、第三n-bufferlayer区和hk介质区;第一n-bufferlayer区形成于p型衬底区内的另一侧,与漂移区结构相邻,且第一n-bufferlayer区的上表面与p型衬底区的上表面位于同一平面,第二n-bufferlayer区形成于第一n-bufferlayer区的下表面,第三n-bufferlayer区形成于第二n-bufferlayer区的下表面,第一集电极形成于第一n-bufferlayer区的上表面,且与漂移区结构相邻,hk介质区从第一集电极的上表面延伸贯穿第一集电极、第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区,且hk介质区的底部位于p型衬底区内。

8、在一些实施例中,第一集电极包括集电极n-buffer区、集电极p区和集电极金属电极;

9、集电极n-buffer区,形成于第一n-bufferlayer区的上表面,集电极n-buffer区与漂移区结构相邻,且集电极n-buffer区包裹集电极p区;

10、集电极金属电极,形成于集电极p区的上表面;

11、hk介质区从集电极p区的上表面延伸贯穿集电极p区、集电极n-buffer区、第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区,且hk介质区的底部位于p型衬底区内。

12、在一些实施例中,发射极结构包括发射极p+区、发射极n+区、发射极p-well区、发射极金属电极;

13、发射极p-well区,形成于p型衬底区的上表面的一侧,发射极p-well区包裹发射极p+区和发射极n+区,发射极p+区和发射极n+区相邻;

14、发射极金属电极,形成于发射极p+区和发射极n+区的上表面,发射极金属电极与栅极结构相邻。

15、在一些实施例中,发射极p+区的厚度、发射极n+区和集电极p区的厚度相同。

16、在一些实施例中,栅极结构包括栅极氧化层和栅极金属电极;

17、栅极氧化层,形成于发射极p-well区的上表面的另一侧,且与发射极金属电极相邻;

18、栅极金属电极,形成于栅极氧化层的上表面。

19、在一些实施例中,漂移区结构包括n-pillar漂移区和p-pillar漂移区;

20、n-pillar漂移区,形成于p型衬底区和第一n-bufferlayer区的上表面的中间区域,n-pillar漂移区与发射极p-well区和集电极n-buffer区相邻;

21、p-pillar漂移区,形成于p型衬底区和第一n-bufferlayer区的上表面的中间区域;p-pillar漂移区与发射极p-well区和集电极n-buffer区相邻;

22、n-pillar漂移区与p-pillar漂移区沿横向方向相邻排布。

23、在一些实施例中,n-pillar漂移区的厚度与p-pillar漂移区的厚度相同,集电极n-buffer区的厚度与发射极p-well区的厚度相同。

24、在一些实施例中,第一n-bufferlayer区的厚度、第二n-bufferlayer区的厚度和第三n-bufferlayer区的厚度均相同,且第一n-bufferlayer区的长度大于第二n-bufferlayer区的长度,第二n-bufferlayer区的长度大于第三n-bufferlayer区的长度。

25、在一些实施例中,第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区构成辅助耗尽区域。

26、在一些实施例中,集电极n-buffer区、集电极p区、第一n-bufferlayer区、第二n-bufferlayer区、第三n-bufferlayer区、集电极金属电极、hk介质区构成电子抽离结构,集电极n-buffer区、集电极p区、第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区的掺杂浓度同时满足sj-ligbt器件的电荷平衡、表面与纵向电场分布的优化以及载流子抽取的需求。

27、相较于现有技术,本发明提供的一种结合hk集电极栅的sj-ligbt器件结构,包括p型衬底区、发射极结构、栅极结构、漂移区结构和集电极结构;发射极结构,形成于p型衬底区的上表面的一侧;栅极结构,形成于发射极结构的上表面的另一侧,且部分集电极结构被发射极结构包裹;漂移区结构,形成于p型衬底区的上表面的中间区域,且漂移区结构与发射极结构相邻;集电极结构,形成于p型衬底区的上表面的另一侧,并从p型衬底区的上表面延伸至p型衬底区内,且集电极结构包裹部分漂移区结构;集电极结构包括第一集电极、第一n-bufferlayer区、第二n-bufferlayer区、第三n-bufferlayer区和hk介质区;第一n-bufferlayer区形成于p型衬底区内的另一侧,与漂移区结构相邻,且第一n-bufferlayer区的上表面与p型衬底区的上表面位于同一平面,第二n-bufferlayer区形成于第一n-bufferlayer区的下表面,第三n-bufferlayer区形成于第二n-bufferlayer区的下表面,第一集电极形成于第一n-bufferlayer区的上表面,且与漂移区结构相邻,hk介质区从第一集电极的上表面延伸贯穿第一集电极、第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区,且hk介质区的底部位于p型衬底区内。这样,多层n-buffer结构即第一n-bufferlayer区、第二n-bufferlayer区和第三n-bufferlayer区,可以辅助p型衬底区进行耗尽,hk集电极栅可以优化sj-ligbt器件结构的纵向电场,从而提高sj-ligbt器件结构击穿电压;另外,多层n-buffer结构结合hk介质区,可以在sj-ligbt器件结构关闭时,辅助抽取电子以加快sj-ligbt器件结构的关断速度,降低关断损耗。

本文地址:https://www.jishuxx.com/zhuanli/20241204/340193.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。