一种半导体器件及其制造方法与流程

- 国知局

- 2024-12-06 12:29:24

本发明涉及半导体,尤其涉及一种半导体器件及其制造方法。

背景技术:

1、随着半导体技术的发展,环栅晶体管应时而生。因环栅晶体管具有的栅堆叠结构不仅形成在沟道区的顶部和侧壁上、还形成在沟道区的底部,故与平面晶体管和鳍式场效应晶体管相比,环栅晶体管具有较强的栅控能力,利于抑制短沟道效应。现有的环栅晶体管制造工艺中,常采用通过向绝缘体上硅衬底包括的顶硅层内注入掺杂的方式抑制寄生沟道漏电,提高环栅晶体管的工作性能。

2、但是,绝缘体上硅衬底中顶硅层的厚度和均匀性难以得到保证,而不同的厚度对杂质注入的浓度要求比较严格,而且顶硅层的厚度通常较小(大约为20nm)导致向厚度较薄的顶硅层内注入杂质的控制精度较高,即导致抑制寄生沟道漏电的难度较大,不利于提升环栅晶体管的电学性能。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,用于防止寄生沟道漏电,提高半导体器件的工作性能,且提高半导体器件的良率。

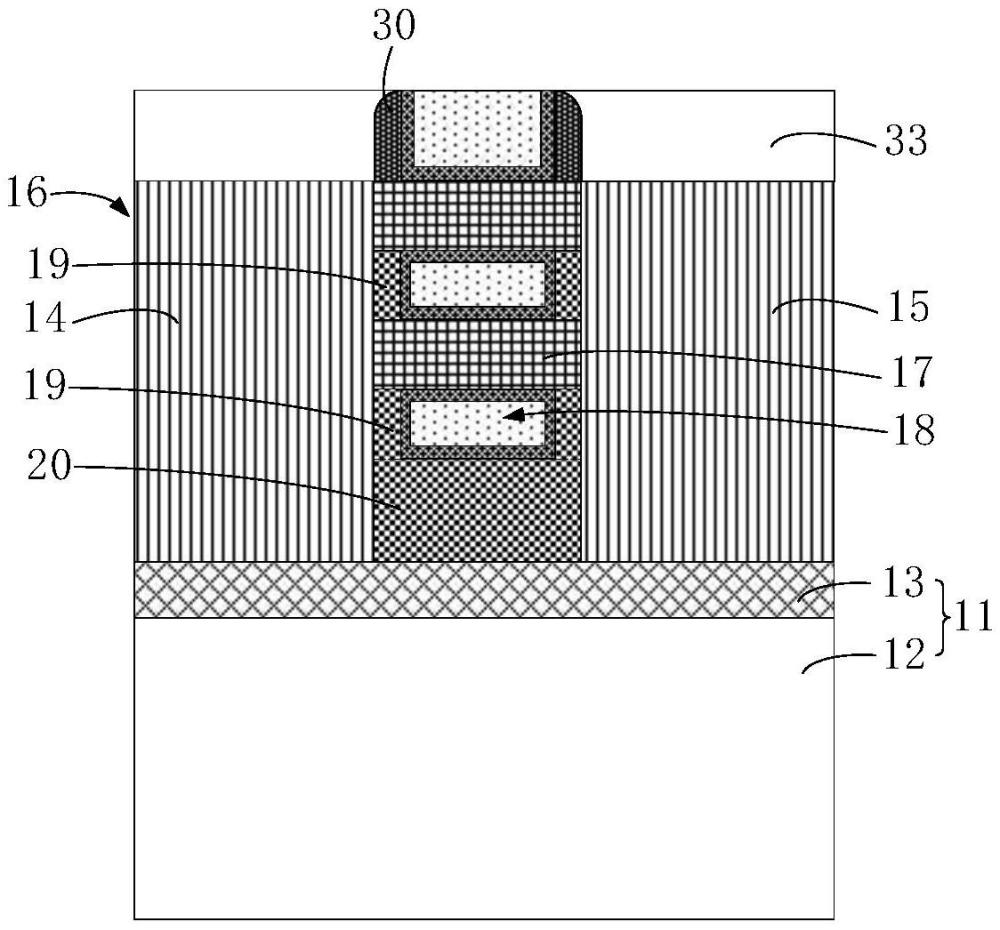

2、为了实现上述目的,第一方面,本发明提供了一种半导体器件,该半导体器件包括:半导体基底、有源结构、栅堆叠结构、内侧墙以及介质隔离结构。半导体基底包括硅衬底、以及形成在硅衬底上的埋氧化层。有源结构直接设置在埋氧化层上。有源结构包括源区、漏区、以及位于源区和漏区之间的至少两层纳米结构。相邻两层纳米结构沿半导体基底的厚度方向间隔分布,位于底层的纳米结构与埋氧化层间隔分布。栅堆叠结构直接设置在埋氧化层上,且位于每层纳米结构的外周。内侧墙至少设置在相邻两层纳米结构之间,且位于栅堆叠结构分别与源区和漏区之间。介质隔离结构设置在底层纳米结构与埋氧化层之间。介质隔离结构的材料和内侧墙的材料相同。沿栅堆叠结构的长度方向,介质隔离结构的宽度大于内侧墙的宽度。

3、采用上述技术方案的情况下,本发明提供的半导体器件中,在底层纳米结构和埋氧化层之间设置有宽度大于内侧墙的介质隔离结构,该介质隔离结构的存在使得栅堆叠结构位于底层纳米结构下方的部分的宽度小于自身其余部分的宽度,降低栅堆叠结构位于底层纳米结构下方的部分与半导体基底之间的接触面积。并且,有源结构和栅堆叠结构均直接形成在半导体基底包括的埋氧化层上。而该埋氧化层为不导电的介质层,因此可以直接利用埋氧化层防止寄生沟道漏电,提高半导体器件的工作性能。同时,埋氧化层分别与设置在自身上的有源结构和栅堆叠结构之间不再设置有顶硅层。换句话说,在制造本发明提供的半导体器件的过程中去除了顶硅层,此时无须为了抑制寄生沟道漏电采用向绝缘体上硅衬底包括的顶硅层内注入掺杂的方式,而因对顶硅层的厚度减薄处理以及对杂质注入的浓度要求比较严格导致半导体器件的良率较低,并且还可以至少节省向顶硅层内注入杂质的操作步骤,利于提高半导体器件的制造效率。此外,介质隔离结构的材料和内侧墙的材料相同,基于此在实际的制造过程中,可以在制造内侧墙的同时形成介质隔离结构,可以进一步提高半导体器件的制造效率。

4、在一种示例中,上述介质隔离结构的宽度小于纳米结构的宽度,且介质隔离结构位于栅堆叠结构分别与源区和漏区之间。

5、在一种示例中,位于底层的纳米结构直接设置在介质隔离结构上,且介质隔离结构将底层纳米结构与埋氧化层隔离开。或者,位于底层的纳米结构与介质隔离结构间隔分布,介质隔离结构将栅堆叠结构环绕在底层纳米结构下方的部分与埋氧化层隔离开。底层内侧墙设置在底层纳米结构和介质隔离结构之间。

6、在一种示例中,上述纳米结构的材料为si1-xgex,其中,0≤x≤0.5。

7、第二方面,本发明提供了一种半导体器件的制造方法,该半导体器件的制造方法包括:首先,形成一半导体基底。半导体基底包括硅衬底、以及形成在硅衬底上的埋氧化层。接下来,在埋氧化层上形成有源结构、内侧墙和介质隔离结构。有源结构包括源区、漏区、以及位于源区和漏区之间的至少两层纳米结构。相邻两层纳米结构沿半导体基底的厚度方向间隔分布,位于底层的纳米结构与埋氧化层间隔分布。介质隔离结构设置在底层纳米结构与埋氧化层之间。介质隔离结构的材料和内侧墙的材料相同。接下来,在埋氧化层上形成栅堆叠结构。栅堆叠结构位于每层纳米结构的外周。内侧墙位于栅堆叠结构分别与源区和漏区之间。沿栅堆叠结构的长度方向,介质隔离结构的宽度大于内侧墙的宽度。

8、在一种示例中,上述形成一半导体基底包括:提供一绝缘体上硅衬底。绝缘体上硅衬底包括依次层叠设置的硅衬底、埋氧化层和顶硅层。接下来,在顶硅层上形成扩散层、以及位于扩散层上的第一氧化层。扩散层的材料包括锗硅或锗。接下来,对扩散层和顶硅层进行氧化处理,使扩散层内的锗元素扩散至顶硅层内,以在埋氧化层上形成沿硅衬底的厚度方向依次层叠设置的含锗半导体层和第二氧化层。接下来,去除第二氧化层,获得半导体基底。

9、在一种示例中,上述扩散层中的锗含量大于等于35%。

10、在一种示例中,上述扩散层的厚度大于等于20nm。

11、在一种示例中,在埋氧化层上形成有源结构、内侧墙和介质隔离结构,包括:在含锗半导体层上形成沿半导体基底的厚度方向依次层叠设置的牺牲层和沟道层。接下来,选择性刻蚀层叠设置的牺牲层和沟道层、以及含锗半导体层,以在埋氧化层上形成鳍状结构。接下来,形成横跨在鳍状结构上的牺牲栅和栅极侧墙。栅极侧墙至少设置在牺牲栅沿自身长度方向的两侧。接下来,去除鳍状结构暴露在牺牲栅和栅极侧墙之外的部分。接下来,沿栅堆叠结构的长度方向,去除每层牺牲层的两侧边缘部分,以形成第一凹口;并至少去除含锗半导体层的两侧边缘部分,以形成第二凹口。接下来,形成填充在第一凹口内的内侧墙,并形成填充在第二凹口内的介质隔离结构。接下来,在剩余的鳍状结构的两侧分别形成源区和漏区。接下来,去除牺牲栅;并至少去除剩余的每层牺牲层,以使剩余的每层沟道层形成相应层纳米结构。

12、在一种示例中,上述牺牲层的材料包括锗硅,且牺牲层的材料中锗含量至少比含锗半导体层的材料中锗含量低5%。

13、在一种示例中,上述第一凹口和第二凹口同时形成。

14、在一种示例中,上述内侧墙和介质隔离结构同时形成。

15、本发明中第二方面及其各种实现方式的有益效果,可以参考第一方面及其各种实现方式中的有益效果分析,此处不再赘述。

技术特征:1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述介质隔离结构的宽度小于所述纳米结构的宽度,且所述介质隔离结构位于所述栅堆叠结构分别与所述源区和所述漏区之间。

3.根据权利要求1所述的半导体器件,其特征在于,位于底层的所述纳米结构直接设置在所述介质隔离结构上,且所述介质隔离结构将底层所述纳米结构与所述埋氧化层隔离开;

4.根据权利要求1所述的半导体器件,其特征在于,所述纳米结构的材料为si1-xgex,其中,0≤x≤0.5。

5.一种半导体器件的制造方法,其特征在于,包括:

6.根据权利要求5所述的半导体器件的制造方法,其特征在于,所述形成一半导体基底,包括:

7.根据权利要求6所述的半导体器件的制造方法,其特征在于,所述扩散层中的锗含量大于等于35%;

8.根据权利要求6所述的半导体器件的制造方法,其特征在于,所述在所述埋氧化层上形成有源结构、内侧墙和介质隔离结构,包括:

9.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述牺牲层的材料包括锗硅,且所述牺牲层的材料中锗含量至少比所述含锗半导体层的材料中锗含量低5%。

10.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述第一凹口和所述第二凹口同时形成;

技术总结本发明公开了一种半导体器件及其制造方法,涉及半导体技术领域,用于防止寄生沟道漏电,提高半导体器件的工作性能,且提高半导体器件的良率。所述半导体器件包括半导体基底、有源结构、栅堆叠结构、内侧墙以及介质隔离结构。有源结构直接设置在埋氧化层上。有源结构包括源区、漏区、以及位于源区和漏区之间的至少两层纳米结构。栅堆叠结构直接设置在埋氧化层上,且位于每层纳米结构的外周。内侧墙至少设置在相邻两层纳米结构之间,且位于栅堆叠结构分别与源区和漏区之间。介质隔离结构设置在底层纳米结构与埋氧化层之间。介质隔离结构的材料和内侧墙的材料相同。沿栅堆叠结构的长度方向,介质隔离结构的宽度大于内侧墙的宽度。技术研发人员:李永亮,雒怀志,张曦,罗军受保护的技术使用者:北京知识产权运营管理有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/341683.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种锂电池湿法回收工艺

下一篇

返回列表