碳化硅基混合二极管及其制备方法与流程

- 国知局

- 2024-12-06 12:28:19

本发明属于芯片,涉及一种碳化硅基混合二极管及其制备方法。

背景技术:

1、碳化硅(sic)作为第三代半导体典型代表,不但具有较宽的禁带宽度,还具有高的击穿电压,高的热导率,高的电子饱和速率等优点。因此,以碳化硅材料制备的电力电子器件具有更高的耐压、更大的电流承载能力以及更高的工作频率,并且其可在高频,高温环境中工作,工作的可靠性高,能够适合苛刻的工作环境等。因此碳化硅材料作为第三代电力电子器件已经成为电力电子技术最为重要的发展方向,在军事和民事领域具有重要的应用前景。

2、在碳化硅的二极管中,肖特基结构显著优点是开关速度快,属于多数载流子器件,没有反向恢复时间,但在高压下肖特基势垒退化,反向漏电大,无法实现耐高压特性。与肖特基结构相比,本征-非掺杂-杂质(positive-intrinsic-negative,pin器件具有更高的耐压,但反向恢复时间较长,正向压降较大。而结势垒肖特基二极管(junction barrierschottky,jbs),是将肖特基和pin结构结合在一起的一种器件结构,结合了两者的优点,有高压,低漏电,低正向导通压降低,反向恢复时间快等。

3、通常碳化硅混合二极管(metal-pin-schottky diode,mps),是在传统的jbs基础上多一层光刻,使得欧姆金属和肖特基金属分开制作,从而降低了降低欧姆接触电阻,提高了正向浪涌能力。

4、但是在传统的mps中,p+欧姆接触仅在硅片的表面实现,这限制了电流的分布和器件的热性能。当电流通过这种结构时,由于接触面积有限,电流密度在接触点处可能会非常高,导致局部过热和电迁移问题,从而影响器件的可靠性和寿命。此外,较小的接触面积也可能限制正向浪涌电流的能力,并且会使得反向耐压不足。

技术实现思路

1、本发明提供一种碳化硅混合二极管及其制备方法,用以解决现有技术中传统mps由于欧姆接触面积较小所导致的一系列问题。

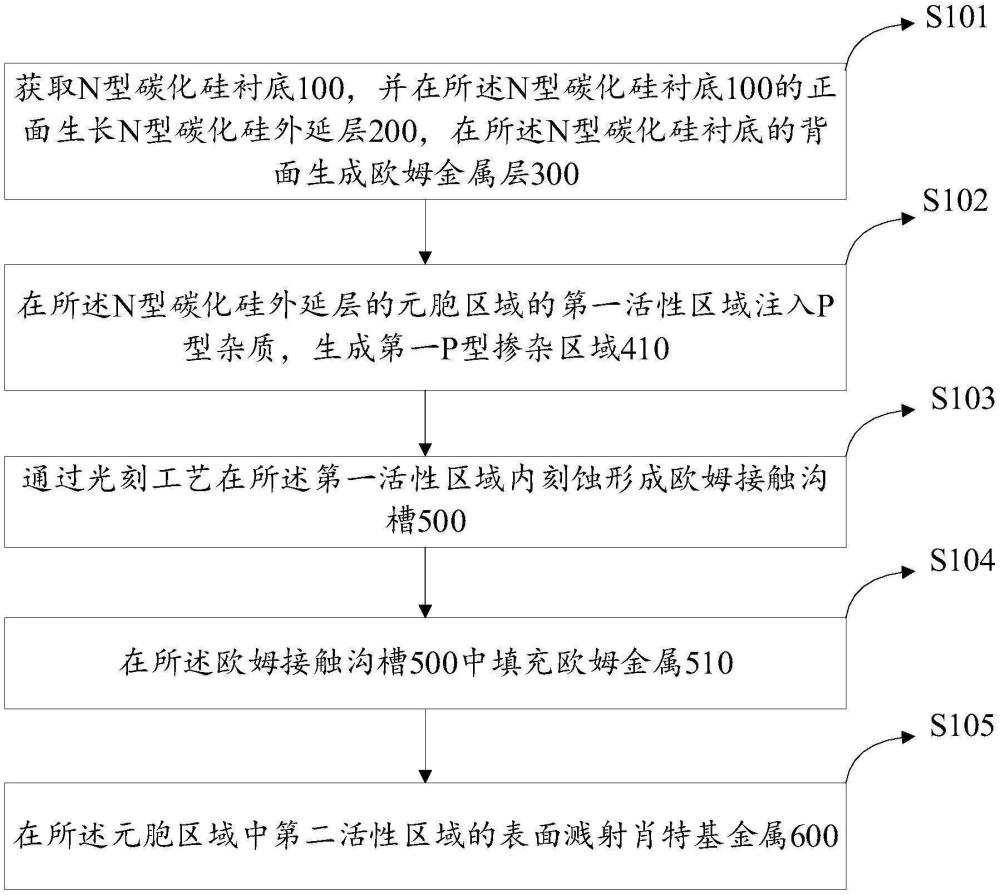

2、为了解决上述技术问题,第一方面,本发明提供一种碳化硅基混合二极管的制备方法,包括:

3、获取n型碳化硅衬底,并在所述n型碳化硅衬底的正面生长n型碳化硅外延层,在所述n型碳化硅衬底的背面生成欧姆金属层;

4、在所述n型碳化硅外延层的元胞区域的第一活性区域注入p型杂质,生成第一p型掺杂区域;

5、通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽,其中,所述欧姆接触沟槽位于所述第一p型掺杂区域内;

6、在所述欧姆接触沟槽中填充欧姆金属;

7、在所述元胞区域中第二活性区域的表面溅射肖特基金属。

8、可选地,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽之后,在所述欧姆接触沟槽中填充欧姆金属之前,还包括:

9、向所述欧姆接触沟槽的底部注入p型杂质,以在所述欧姆接触沟槽底部形成p型杂质势垒。

10、可选地,所述在所述元胞区域中第二活性区域的表面溅射肖特基金属,包括:

11、在所述第二活性区域的表面刻蚀肖特基沟槽;

12、在所述肖特基沟槽内溅射肖特基金属,并将所述肖特基金属与碳化硅合金,以形成肖特基势垒。

13、可选地,在所述并在所述n型碳化硅衬底的正面生长n型外延层之后,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽之前,还包括:

14、在所述n型碳化硅外延层的元胞区域的终端区域注入p型杂质,生成第二p型掺杂区域。

15、可选地,所述p型杂质势垒的掺杂浓度大于所述第一p型掺杂区域的掺杂浓度。

16、可选地,所述第一p型掺杂区域的宽度大于所述第二p型掺杂区域的宽度。

17、可选地,所述p型杂质为铝。

18、可选地,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽,包括:

19、在所述元胞区域的表面淀积lpteos作为阻挡层;

20、在所述lpteos上溅射镍作为刻蚀的遮挡层;

21、通过光刻工艺刻蚀所述遮挡层和所述阻挡层,并在刻蚀完成后去除光刻胶;

22、对所述元胞区域所暴露的表面刻蚀,以形成欧姆接触沟槽。

23、可选地,所述肖特基金属为钛。

24、第二方面,本发明提供一种碳化硅基混合二极管,包括:

25、n型碳化硅衬底;

26、欧姆金属层,生成于所述n型碳化硅衬底的背面;

27、n型碳化硅外延层,生长于所述n型碳化硅衬底的正面,且在所述元胞区域的第一活性区域刻蚀有欧姆接触沟槽,在所述元胞区域的第二活性区域刻蚀有肖特基沟槽;

28、肖特基金属,形成在所述肖特基沟槽的表面;

29、欧姆金属,填充于所述欧姆接触沟槽内;

30、第一p型掺杂区域,位于所述n型碳化硅外延层的元胞区域的第一活性区域,且所述欧姆接触沟槽位于所述第一p型掺杂区域内;

31、p型杂质势垒,形成于所述欧姆接触沟槽的底部,且所述p型杂质势垒的掺杂浓度大于所述第一p型掺杂区域的掺杂浓度;

32、第二p型掺杂区域,位于所述n型碳化硅外延层的终端区域。

33、与现有技术相比,本发明提供的一种碳化硅基混合二极管的制备方法,具有以下有益效果:

34、本发明在制备碳化硅基混合二极管的过程中,在第一p型掺杂区域内刻蚀形成欧姆接触沟槽,并在欧姆接触沟槽中填充欧姆金属,这样在第一p型掺杂区域内,与欧姆金属发生欧姆接触的p型杂质可以位于第一p型掺杂区域内的两个侧壁和底部的硅面,这样在第一p型掺杂区域内p型杂质欧姆接触面积可以大大增加,而接触面积的增加意味着电流可以更均匀地分布在更大的区域上,这降低了局部电流密度,减少了热聚集和电迁移的风险,从而提高了器件的热稳定性和可靠性;并且由于接触面积增大,器件可以承受更大的正向瞬态电流而不至于过热或损坏,这对于需要处理大电流的应用尤其重要;另外还可以改善反向耐压,因为反向欧姆金属作为场板使用,可以改善电场分布,提高器件的反向击穿电压,这意味着在反向偏置条件下,器件可以承受更高的电压而不被击穿。综上所述,本发明能够解决现有技术中的传统mps由于欧姆接触面积较小所导致的一系列问题。

技术特征:1.一种碳化硅基混合二极管的制备方法,其特征在于,包括:

2.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽之后,在所述欧姆接触沟槽中填充欧姆金属之前,还包括:

3.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,所述在所述元胞区域中第二活性区域的表面溅射肖特基金属,包括:

4.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,在所述并在所述n型碳化硅衬底的正面生长n型外延层之后,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽之前,还包括:

5.根据权利要求2所述的碳化硅基混合二极管的制备方法,其特征在于,所述p型杂质势垒的掺杂浓度大于所述第一p型掺杂区域的掺杂浓度。

6.根据权利要求4所述的碳化硅基混合二极管的制备方法,其特征在于,所述第一p型掺杂区域的宽度大于所述第二p型掺杂区域的宽度。

7.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,所述p型杂质为铝。

8.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,所述通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽,包括:

9.根据权利要求1所述的碳化硅基混合二极管的制备方法,其特征在于,所述肖特基金属为钛。

10.一种碳化硅基混合二极管,其特征在于,包括:

技术总结本发明属于芯片技术领域,公开了一种碳化硅混合二极管及其制备方法,该制备方法包括:获取N型碳化硅衬底,并在所述N型碳化硅衬底的正面生长N型碳化硅外延层,在所述N型碳化硅衬底的背面生成欧姆金属层;在所述N型外延层的元胞区域的第一活性区域注入P型杂质,生成第一P型掺杂区域;通过光刻工艺在所述第一活性区域内刻蚀形成欧姆接触沟槽,其中,所述欧姆接触沟槽位于所述第一P型掺杂区域内;在所述欧姆接触沟槽中填充欧姆金属;在所述元胞区域中第二活性区域的表面溅射肖特基金属。利用本发明公开的方法,可以实现解决现有技术中传统MPS由于欧姆接触面积较小所导致的一系列问题。技术研发人员:杜蕾,张学强,和巍巍受保护的技术使用者:深圳基本半导体有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/341582.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表