一种ZnO阵列膜式压敏电阻的制备方法与流程

- 国知局

- 2025-01-10 13:16:45

本发明涉及压敏电阻制备领域,具体来说,尤其涉及一种zno阵列膜式压敏电阻的制备方法。

背景技术:

1、压敏电阻是一种具有非线性伏安特性的电阻器件,其电阻值随外加电压的增加而敏感地变化,具有抑制瞬态过电压的作用。压敏电阻通常与被保护的电路或电子元器件并联,当电路中出现的瞬态过电压超过压敏电阻的阈值电压时,其电阻会急剧下降,通过压敏电阻的电流呈数个数量级地增大,而电压增加幅度很小,从而达到保护并联的电路或电子元器件的作用。为满足对各种集成电路、精密电子线路及芯片等方面的保护需求,对低压zno压敏电阻的需求量日益增多,对其性能的要求也越来越高。

2、由于低压压敏电阻的厚度很薄,在厚度方向晶粒数目很少,晶粒尺寸不均匀带来的电性能不均匀问题会非常突出。

3、为了解决现有技术问题,本发明的目的在于克服已有技术存在的不足,提供一种可精准调控压敏电阻压敏电压,并可提高电性能一致性的阵列式薄膜压敏电阻的制备方法。该结构有利于低压压敏电阻的电性能提升,尤其对小于5v的超低压压敏电阻影响更为明显,有利于实现对各种集成电路、精密电子线路及芯片等现代电子系统的保护需求。

4、针对相关技术中的问题,目前尚未提出有效的解决方案。

技术实现思路

1、为了克服以上问题,本发明旨在提出一种zno阵列膜式压敏电阻的制备方法,目的在于提供一种可精准调控压敏电阻压敏电压,并可提高电性能一致性的阵列式薄膜压敏电阻的制备方法。该结构有利于低压压敏电阻的电性能提升。

2、为此,本发明采用的具体技术方案如下:

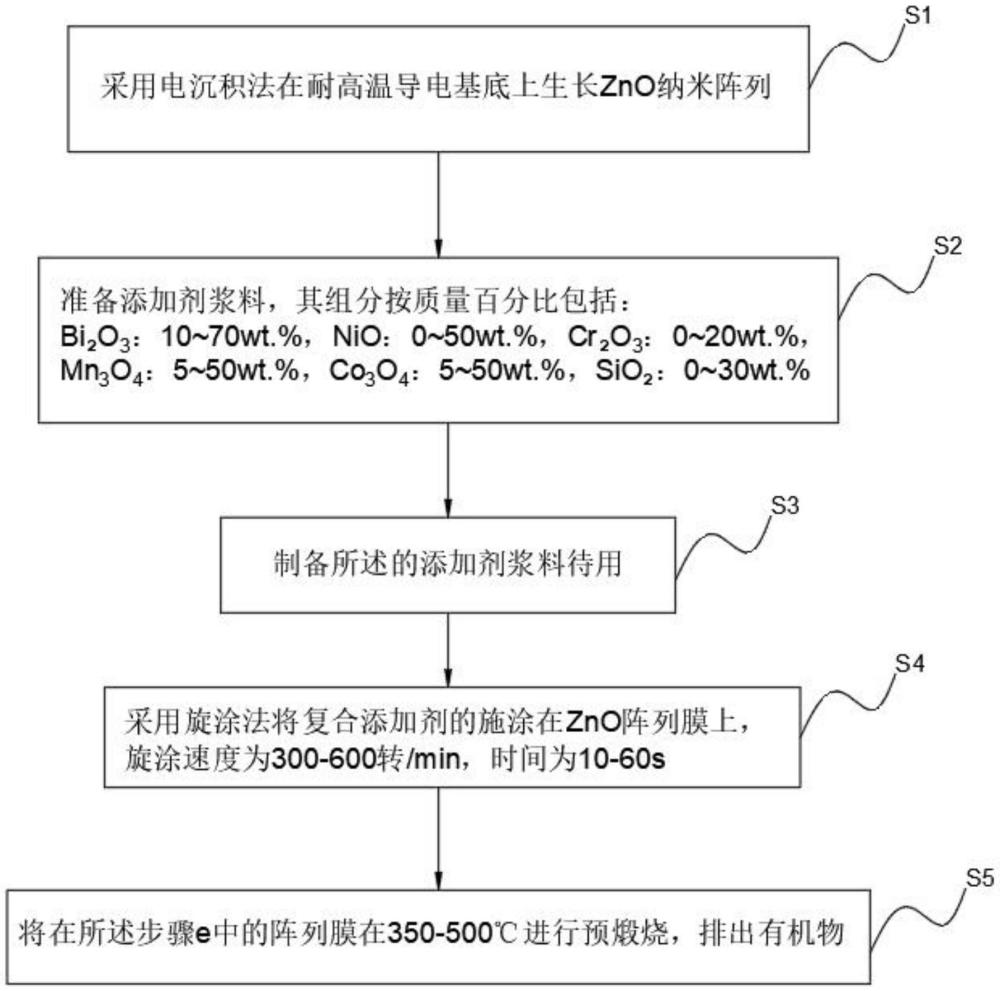

3、根据本发明的一个方面,提供了一种zno阵列膜式压敏电阻的制备方法,该制备方法具体包括如下步骤:

4、s1、采用电沉积法在耐高温导电基底上生长zno纳米阵列;

5、s2、准备添加剂浆料,其组分按质量百分比包括:bi2o3:10~70wt.%,nio:0~50wt.%,cr2o3:0~20wt.%,mn3o4:5~50wt.%,co3o4:5~50wt.%,sio2:0~30wt.%;

6、s3、制备s2的添加剂浆料待用;

7、s4、采用旋涂法将复合添加剂的施涂在zno阵列膜上,旋涂速度为300-600转/min,时间为10-60s;

8、s5、将在所述步骤s4中的阵列膜在350-500℃进行预煅烧,排出有机物。

9、可选地,所述采用电沉积法在耐高温导电基底上生长zno纳米阵列具体过程如下:

10、s11、在耐高温导电陶瓷基底上蒸镀一层pt做为底端电极;

11、s12、配制的硝酸锌和六亚甲基四胺的混合水溶液,保持溶液温度70-95℃,以步骤s11蒸镀的pt为负极,施加2.1v电压,进行电化学沉积30-180分钟,用去离子水冲洗得到zno阵列膜。

12、可选地,所述制备s2的添加剂浆料待用具体过程如下:

13、s31、将在所述步骤s2中准备原料与去离子水混合,形成混合浆,并使混合料浆达到固体质量百分比不低于30%的含固率,然后将固体悬浊液加入到卧式砂磨机中,砂磨30-90min,使得浆料的粒径达到0.3-0.6μm;

14、s32、将在所述步骤s31中制备的料浆烘干后进行煅烧,煅烧温度900-1200℃,煅烧时间1-4h。

15、可选地,所述将在所述步骤s4中的阵列膜在350-500℃进行预煅烧,排出有机物具体过程如下:

16、s51、将所述预煅烧处理的坯体在800-1200℃的高温下煅烧30-120min;

17、s52、在步骤s51煅烧过的阵列膜上沉积pt电极,形成zno阵列膜式压敏电阻。

18、可选地,所述步骤s12中,电化学沉积时间为60-120分钟。

19、可选地,所述步骤s32中煅烧温度950-1100℃,煅烧时间为2-3小时。

20、一种zno阵列膜式压敏电阻的制备方法制备得到的压敏电阻,其特征在于,包括从上到下依次设置的顶部金属电极、复合添加剂层、zno阵列膜、底部导电层以及耐高温导电基底。

21、相较于现有技术,本申请具有以下有益效果:

22、1、本发明制备的阵列膜式压敏电阻有利于低压压敏电阻的电性能提升,尤其对小于5v的超低压压敏电阻影响更为明显,有利于实现对各种集成电路、精密电子线路及芯片等现代电子系统的保护需求。

23、2、本发明工艺简洁,不需要大型精密陶瓷芯片加工设备,制备的压敏电阻体积小、通流能力强,可实现比多层式压敏电阻更低的压敏电压。

技术特征:1.一种zno阵列膜式压敏电阻的制备方法,其特征在于,该制备方法具体包括如下步骤:

2.根据权利要求1所述的一种zno阵列膜式压敏电阻的制备方法,其特征在于,所述采用电沉积法在耐高温导电基底上生长zno纳米阵列具体过程如下:

3.根据权利要求1所述的一种zno阵列膜式压敏电阻的制备方法,其特征在于,所述制备s2的添加剂浆料待用具体过程如下:

4.根据权利要求1所述的一种zno阵列膜式压敏电阻的制备方法,其特征在于,所述将在所述步骤s4中的阵列膜在350-500℃进行预煅烧,排出有机物具体过程如下:

5.根据权利要求2所述的一种zno阵列膜式压敏电阻的制备方法,其特征在于,所述步骤s12中,电化学沉积时间为60-120分钟。

6.根据权利要求3所述的一种zno阵列膜式压敏电阻的制备方法,其特征在于,所述步骤s32中煅烧温度950-1100℃,煅烧时间为2-3小时。

7.根据权利要求1-6任一项所述的一种zno阵列膜式压敏电阻的制备方法制备得到的压敏电阻,其特征在于,包括从上到下依次设置的顶部金属电极、复合添加剂层、zno阵列膜、底部导电层以及耐高温导电基底。

技术总结本发明公开了一种ZnO阵列膜式压敏电阻的制备方法,用于压敏电阻制备领域,该制备方法具体包括如下步骤,采用电沉积法在耐高温导电基底上生长ZnO纳米阵列,准备添加剂浆料,其组分按质量百分比包括:Bi<subgt;2</subgt;O<subgt;3</subgt;:10~70wt.%,NiO:0~50wt.%,Cr<subgt;2</subgt;O<subgt;3</subgt;:0~20wt.%,Mn<subgt;3</subgt;O<subgt;4</subgt;:5~50wt.%,Co<subgt;3</subgt;O<subgt;4</subgt;:5~50wt.%,SiO<subgt;2</subgt;:0~30wt.%,制备S2的添加剂浆料待用,采用旋涂法将复合添加剂的施涂在ZnO阵列膜上,旋涂速度为300‑600转/min,时间为10‑60s,将在所述步骤S4中的阵列膜在350‑500℃进行预煅烧,排出有机物。本发明制备的阵列膜式压敏电阻有利于低压压敏电阻的电性能提升,尤其对小于5V的超低压压敏电阻影响更为明显,有利于实现对各种集成电路、精密电子线路及芯片等现代电子系统的保护需求。技术研发人员:任鑫受保护的技术使用者:无锡海锡电气科技有限公司技术研发日:技术公布日:2025/1/6本文地址:https://www.jishuxx.com/zhuanli/20250110/352106.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表