带载体的金属箔以及其使用方法和制造方法与流程

- 国知局

- 2025-01-10 13:14:33

本发明涉及带载体的金属箔以及其使用方法和制造方法。

背景技术:

1、近年来,为了提高印刷电路板的安装密度而进行小型化,开始广泛进行印刷电路板的多层化。这样的多层印刷电路板在便携式电子设备的多数中出于轻量化、小型化为目的而被利用。于是,对该多层印刷电路板要求层间绝缘层的厚度的进一步降低、以及作为布线板的更进一步的轻量化。

2、作为满足这样的要求的技术,采用使用无芯积层法的多层印刷电路板的制造方法。无芯积层法是指不使用所谓的芯基板、而是交替地积层(build up)绝缘层与布线层来进行多层化的方法。无芯积层法中,为了容易地进行支撑体与多层印刷电路板的剥离,提出了使用带载体的铜箔的方案。例如,专利文献1(日本特开2005-101137号公报)中公开了一种半导体元件搭载用封装基板的制造方法,其包括以下步骤:在带载体的铜箔的载体面粘贴绝缘树脂层而制成支撑体,通过光致抗蚀加工、图案电解镀铜、抗蚀剂去除等工序在带载体的铜箔的极薄铜层侧形成第一布线导体后,形成积层布线层,将带载体的支撑基板剥离,去除极薄铜层。

3、另外,为了专利文献1所示的嵌入电路的微细化,理想的是,将极薄铜层的厚度设为1μm以下的带载体的铜箔。因此,为了实现极薄铜层的厚度降低,提出了通过溅射等气相法形成极薄铜层的方案。例如,专利文献2(国际公开第2017/150283号)中公开了通过溅射在玻璃或陶瓷等载体上形成有剥离层、防反射层以及极薄铜层的带载体的铜箔。另外,专利文献3(国际公开第2017/150284号)中公开了通过溅射在玻璃或陶瓷等载体上形成有中间层(例如密合金属层和剥离辅助层)、剥离层以及极薄铜层(例如膜厚300nm)的带载体的铜箔。专利文献2和3中还给出了如下启示:通过夹设由规定的金属构成的中间层来赋予载体机械剥离强度优异的稳定性、或者通过使防反射层呈理想的暗色,可以使图像检测(例如自动图像检测(aoi))中的辨识性提高。

4、总之,随着电子装置的更进一步小型化以及节电化,对半导体芯片和印刷电路板的高度集成化以及薄型化的需求正在提高。作为满足该需求的新一代封装技术,近年正在研究采用fo-wlp(fan-out wafer level packaging)、plp(panel level packaging)。并且,在fo-wlp、plp中,也正在研究采用无芯积层法。作为这样的方法之一,有被称作rdl-first(redistribution layer-first)法的方法,即,在无芯支撑体表面形成布线层以及根据需要的积层布线层,进而根据需要将支撑体剥离后,进行芯片的安装。例如,专利文献4(日本特开2015-35551号公报)中公开了一种半导体装置的制造方法,其包括如下步骤:在由玻璃或硅晶圆制成的支撑体的主面形成金属剥离层;在其上形成绝缘树脂层;在其上形成包含积层层的重布线层(redistribution layer);在其上的半导体集成电路的安装以及密封;由支撑体的去除带来的剥离层的露出;剥离层的去除带来的2次安装焊盘的露出;以及在2次安装焊盘的表面形成焊锡凸块;以及2次安装。

5、另一方面,已知有将电路图案曝光转印在半导体晶圆上时,在曝光前进行以对准标记为基准的位置对准的技术。例如,专利文献5(日本特开平9-74062号公报)公开了一种半导体曝光方法,其包括:在半导体晶圆上形成示出晶体取向的图案的工序;对该图案进行检测的工序;基于该检测结果将晶圆定位在规定的曝光位置的工序;以及,将最初的电路图案曝光转印在定位的晶圆上的工序。根据专利文献5,通过以所述方法进行曝光转印,可以在相对于晶体取向正确的位置上进行曝光,并且即使是不同的装置也能够在相同位置进行曝光。

6、现有技术文献

7、专利文献

8、专利文献1:日本特开2005-101137号公报

9、专利文献2:国际公开第2017/150283号

10、专利文献3:国际公开第2017/150284号

11、专利文献4:日本特开2015-35551号公报

12、专利文献5:日本特开平9-74062号公报

技术实现思路

1、随着近年来电子设备的进一步小型轻量化,期望重布线层具有线/间距(l/s)被极度微细化的布线图案(例如l/s=2μm/2μm)。为了应对该要求,想到如专利文献2及3所示那样在具备厚度被降低的极薄铜层的带玻璃载体的铜箔(或带陶瓷载体的铜箔)上通过上述的积层法等形成重布线层。另一方面,在光刻工艺中,曝光装置的曝光分辨率与曝光区域通常为折衷关系,因此微细电路形成用的曝光分辨率优异的曝光装置通常曝光区域窄(例如70mm见方)。因此,可以采用进行形成粗大电路的曝光及显影后,再次进行形成微细电路的曝光及显影的2阶段的电路形成工艺。换言之,首先,为了形成芯片安装所需的粗设计而经历使用曝光区域广(例如250mm见方)但曝光分辨率差的曝光装置的曝光及之后的显影,形成粗大电路(例如l/s=10μm/10μm的粗大电路)(第1阶段的电路形成)。然后,经历使用微细电路形成用的曝光装置的曝光及之后的显影,形成微细电路(第2阶段的电路形成)。然而,该2阶段的电路形成方法的工艺复杂,并且会先形成粗大电路,因此为了进一步形成微细电路,需要高的位置对准精度,易于导致成品率的降低。如前所述,虽然已知使用在半导体(si)晶圆上形成的示出晶体取向的图案的位置对准技术(参见专利文献5),但带载体的铜箔本来就不是半导体(si)晶圆那样的单晶,因此形成示出晶体取向的图案本身就是不可能的,期望适于带载体的金属箔的对准标记。

2、本发明人等本次得到了如下见解:在带载体的金属箔中,通过对载体自身设置构成对准标记的加工部,能够以相同的对准标记为基准进行布线形成时的粗大电路用的曝光及微细电路用的曝光这两者,其结果,可以在1阶段的电路形成工艺中同时形成粗大电路及微细电路。

3、因此,本发明的目的在于提供一种带载体的金属箔,其能够以相同的对准标记为基准进行布线形成时的粗大电路用的曝光及微细电路用的曝光这两者,其结果,可以在1阶段的电路形成工艺中同时形成粗大电路及微细电路。

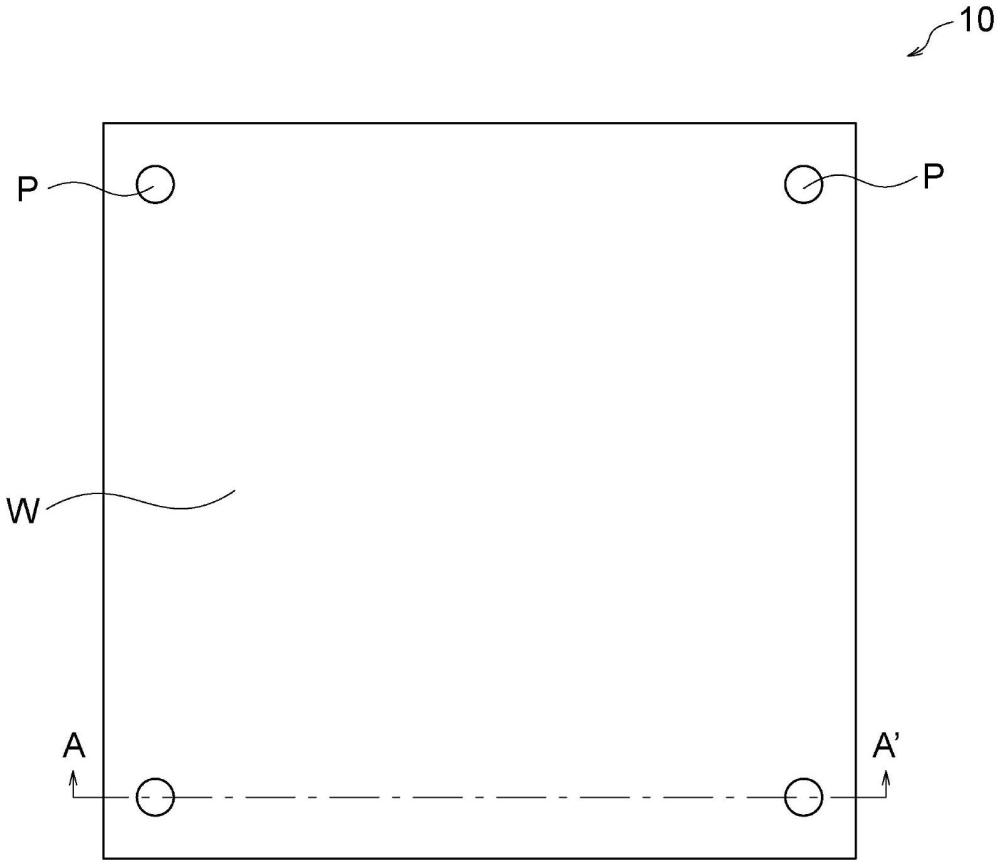

4、根据本发明的一个方式,提供一种带载体的金属箔,其具备:载体、设置在前述载体的至少一面上的剥离层、和设置在前述剥离层上的金属层,

5、前述带载体的金属箔具有布线用区域和至少2个定位用区域,

6、前述布线用区域遍布其整个区域地存在前述载体、前述剥离层及前述金属层,

7、前述至少2个定位用区域设置于前述带载体的金属箔的前述至少一面,形成在伴随曝光及显影的布线形成时用于位置对准的对准标记。

8、根据本发明的另一方式,提供一种使用前述带载体的金属箔经过曝光及显影而形成布线的方法,其包括在曝光前以前述带载体的金属箔的前述定位用区域为基准进行位置对准的工序,其中,

9、分别进行电路宽度不同的多个电路的曝光,并且,同时进行前述多个电路的显影。

10、根据本发明的另一方式,提供一种前述带载体的金属箔的制造方法,其包括:

11、准备载体的工序;

12、对前述载体的至少一面的规定区域进行加工,形成至少2个构成前述对准标记的加工部,由此划分出至少2个定位用区域的工序;以及,

13、在前述载体的前述至少一面依次形成前述剥离层及前述金属层的工序。

本文地址:https://www.jishuxx.com/zhuanli/20250110/351841.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。