微孔阵列及其制备方法与流程

- 国知局

- 2024-06-20 10:52:41

本公开属于生物分子检测芯片领域,具体而言,涉及一种生物分子检测芯片的微孔阵列的设计和其制备方法。

背景技术:

1、基于纳米孔的生物分子检测芯片是生物分子检测领域的纳米孔基因测序仪、纳米孔蛋白测序仪及其他基于纳米孔的生物分子检测设备的关键部件,包括纳米孔核酸测序芯片、纳米孔蛋白测序芯片和纳米孔蛋白检测芯片等,其主要作用是将核酸、蛋白质等生物分子或其序列信号转化为电流信号。分子检测芯片的微孔能提供生物分子检测时必需的反应容器和环境,对生物膜和纳米孔等生化系统的形成至关重要,其阵列的结构设计将直接决定生物分子检测芯片的结构及性能。

2、本公开的发明人发现,目前的情况来说,用于基于纳米孔的生物分子检测芯片还存在多个方面的技术问题亟待攻克,例如:芯片单元尺寸进一步缩小以提升芯片集成度、微孔生物相容性提升及结构优化以增加生物膜成膜效率、良率、稳定性等。

技术实现思路

1、本发明提供一种本公开实施例提供一种基于纳米孔的生物分子检测芯片微孔阵列的设计及其制备方法,用于对上述多个方面的技术问题之一进行改进。

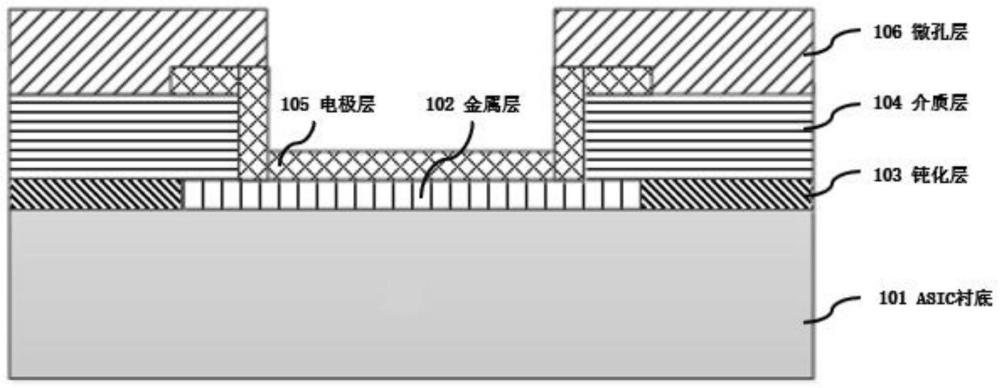

2、根据本发明的第一方面,提供一种微孔阵列。所述微孔阵列的每个微孔结构单元包括:asic衬底;金属层,位于所述asic衬底之上;钝化层,位于所述asic衬底之上;介质层,位于所述金属层和所述钝化层之上,完全覆盖所述钝化层的顶部,并且覆盖所述金属层的顶部的部分区域;电极层,位于所述金属层和所述介质层之上,覆盖所述金属层的顶部未覆盖介质层的区域以及所述介质层的顶部的部分区域;微孔层,位于所述介质层和所述电极层之上。在所述微孔层中形成微孔,所述微孔从所述微孔层的顶部贯穿至覆盖所述金属层的顶部的所述电极层的顶部。所述微孔的侧壁从上至下分别是微孔层和电极层。

3、在根据本发明第一方面的微孔阵列中,优选地,所述微孔的截面尺寸为0.5~10μm,贯穿深度为0.2~10μm。

4、在根据本发明第一方面的微孔阵列中,优选地,所述介质层的材料包括以下至少一种:二氧化硅(sio2)、二氧化钛(tio2)、氮化硅(sin)、二氧化锆(zro2)、三氧化二铝(al2o3)、聚酰亚胺(pi)。

5、在根据本发明第一方面的微孔阵列中,优选地,所述电极层包括集流体层和集流体层之上的超级电容电极层。所述集流体层的材料包括以下至少一种:过渡金属薄膜、过渡金属氮化物薄膜、过渡金属与其氮化物的复合薄膜。所述超级电容电极层的材料包括在所述集流体层上形成的过渡金属的氮氧化物薄膜。所述过渡金属可以包括ti、v、ta、mo、hf中的至少一种。

6、在根据本发明第一方面的微孔阵列中,优选地,所述微孔层的材料包括以下材料中的至少一种:聚对二甲苯(pyralene)、特氟龙(teflon)、环烯烃类共聚物(coc)、类金刚石膜(dlc)、聚亚酰胺(pi)、环氧型光刻胶(su8)、聚对苯撑苯并二噁唑光刻胶(pbo)。

7、在根据本发明第一方面的微孔阵列中,优选地,在所述微孔层与所述电极层之间没有间隙。

8、在根据本发明第一方面的微孔阵列中,优选地,所述微孔层包括:微孔层下层;微孔层上层,位于所述微孔层下层之上。在所述微孔层上层形成的微孔的截面尺寸大于在所述微孔层下层形成的微孔的截面尺寸。

9、优选地,在所述微孔层上层形成的微孔的截面尺寸为0.5~20μm,在所述微孔层下层形成的微孔的截面尺寸为0.5~10μm,所述微孔的贯穿深度为0.2~10μm。

10、相比于现有侧壁包含介质层的方案,根据本发明第一方面的方案由于部分侧壁为电极层,可显著增加电极层的总面积。因此相比于侧壁包含介质层的方案可允许微孔直径进一步缩小,实现进一步提升芯片上单位面积上微孔数量的目标。

11、根据本发明的第二方面,提供一种微孔阵列。所述微孔阵列的每个微孔结构单元包括:asic衬底;金属层,位于所述asic衬底之上;钝化层,位于所述asic衬底之上;介质层,位于所述金属层和所述钝化层之上,完全覆盖所述钝化层的顶部,并且覆盖所述金属层的顶部的部分区域;电极层,位于所述金属层和所述介质层之上,覆盖所述金属层的顶部未覆盖介质层的区域以及所述介质层的顶部的部分区域;微孔层,位于所述介质层之上。在所述微孔层中形成微孔,所述微孔从所述微孔层的顶部贯穿至所述电极层的顶部,所述微孔的侧壁从上至下分别是微孔层和电极层。在所述微孔的内圈形成由电极层边缘部分覆盖介质层而形成的凸起结构,所述凸起结构高于所述介质层的顶部,但低于微孔层的顶部。

12、根据本发明第二方面的微孔阵列中,优选地,在所述微孔层形成的微孔的截面尺寸为0.5~10μm,微孔的贯穿深度为0.2~10μm。

13、类似地,相比于现有侧壁包含介质层的方案,根据本发明第二方面的方案由于部分侧壁为电极层,可显著增加电极层的总面积,因此相比于侧壁包含介质层的方案可允许微孔直径进一步缩小,实现进一步提升芯片上单位面积上微孔数量的目标。

14、此外,根据本发明第一方面的可选实施方式也都适用于根据第二方面的微孔阵列的方案。

15、根据本发明的第三方面,提供一种微孔阵列的制备方法。在所述制备方法中,通过以下步骤形成所述微孔阵列的每个微孔结构单元:提供asic衬底;在asic衬底上形成金属层;在asic衬底上形成钝化层;在所述金属层和所述钝化层上形成介质层,其中,暴露出所述金属层的顶部的部分区域;在所述介质层的顶部的部分区域以及暴露出的所述金属层的顶部的部分区域上形成电极层;在所述介质层和所述电极层上形成微孔层;在所述微孔层中形成微孔。所述微孔从所述微孔层的顶部贯穿至覆盖所述金属层的顶部的所述电极层的顶部。所述微孔的侧壁从上至下分别是微孔层和电极层。

16、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述方法进一步包括:在提供asic衬底以及形成金属层和钝化层之后,对所述asic衬底顶部的金属层和钝化层表面进行平坦化。例如,可以使用化学机械抛光(cmp)技术或类似平坦化技术。

17、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述的形成电极层的步骤进一步包括:使电极层材料覆盖所述介质层和暴露出的所述金属层的顶部的部分区域;以及去除部分电极层材料,暴露出介质层的顶部的一部分。

18、优选地,所述方法进一步包括:在去除部分电极层材料之前,在所述电极层上形成保护层;以及在去除部分电极层材料之后,去除所述保护层。所述保护层包括介质材料,在所述电极层上生长,厚度为10nm~2μm。所述保护层的介质材料包括以下至少一种:二氧化硅(sio2)、二氧化钛(tio2)、氮化硅(sin)、二氧化锆(zro2)、三氧化二铝(al2o3)、聚酰亚胺(pi)。

19、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述的形成介质层的步骤进一步包括:使用pecvd、旋涂或者贴膜方式形成所述介质层,厚度为0.1~10μm;通过去除不需要的介质材料,暴露出所述金属层的顶部的部分区域。

20、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述的形成电极层的步骤进一步包括:在所述介质层的顶部的部分区域以及暴露出的所述金属层的顶部的部分区域上形成集流体层;和在所述集流体层上形成超级电容电极层。

21、优选地,使用磁控溅射的方式沉积形成厚度为10nm~4μm的氮化钛(tin)以形成所述集流体层;和使用磁控溅射的方式沉积形成厚度为40nm~4μm的氮氧化钛以形成所述超级电容电极层。

22、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述的形成微孔层的步骤包括使用旋涂、贴膜形成一层有机材料层作为微孔层,厚度为0.2~10μm。所述的在所述微孔层中形成微孔的步骤包括对所述微孔的区域进行图形化以去除部分微孔层材料,图形化的微孔截面尺寸为0.5~10μm。

23、在根据本发明第三方面的微孔阵列的制备方法中,优选地,所述的形成微孔层和形成微孔的步骤包括:使用压印的方法将已经图形化的微孔层转印到所述电极层和介质层上。

24、优选地,所述微孔层的材料为su8或pbo。

25、类似地,相比于现有侧壁包含介质层的方案,根据本发明第三方面的方案由于部分侧壁为电极层,可显著增加电极层的总面积。因此相比于侧壁包含介质层的方案可允许微孔直径进一步缩小,实现进一步提升芯片上单位面积上微孔数量的目标。

26、与现有技术相比,本制备方法可避免用于形成生物膜的磷脂等脂质材料在间隙处堆积,从而提升形成的生物膜的良率、质量和稳定性。

27、此外,根据本发明第一方面的可选实施方式所对应的方法步骤也都适用于根据第三方面的微孔阵列的制备方法。

28、在以上的实施方案中,去除部分电极层材料以暴露出介质层的顶部的一部分的步骤可以采用图形化来完成,更具体,可以使用光刻和刻蚀技术。

29、在可选的实施方案中,保护层可以通过化学机械抛光(cmp)、图形化刻蚀或其组合的方式去除,其目的在于保护超级电容电极层疏松的表面,使其电压驱动能力得到保持,且可避免在电极层和微孔层之间形成间隙。

30、此外,在微孔层图形化后,若在前述步骤未去除所述保护层,可使用刻蚀或腐蚀的方法去除。

31、根据本发明的第四方面,提供一种微孔阵列的制备方法。在所述方法中,通过以下步骤形成所述微孔阵列的每个微孔结构单元:提供asic衬底;在asic衬底上形成金属层;在asic衬底上形成钝化层;在所述金属层和所述钝化层上形成介质层,其中,暴露出所述金属层的顶部的部分区域;在所述介质层的顶部的部分区域以及暴露出的所述金属层的顶部的部分区域上形成电极层;在所述介质层上形成微孔层;在所述微孔层中形成微孔,所述微孔从所述微孔层的顶部贯穿至所述电极层的顶部,所述微孔的侧壁从上至下分别是微孔层和电极层。在所述微孔的内圈形成由电极层边缘部分覆盖介质层而形成的凸起结构,所述凸起结构高于所述介质层的顶部,但低于微孔层的顶部。

32、在根据本发明第四方面的微孔阵列的制备方法中,优选地,在所述微孔层形成的微孔的截面尺寸为0.5~10μm,微孔的贯穿深度为0.2~10μm。

33、类似地,相比于现有侧壁包含介质层的方案,根据本发明第五方面的方案由于部分侧壁为电极层,可显著增加电极层的总面积。因此相比于侧壁包含介质层的方案可允许微孔直径进一步缩小,实现进一步提升芯片上单位面积上微孔数量的目标。

34、此外,根据本发明第一方面的可选实施方式所对应的方法步骤也都适用于根据第四方面的微孔阵列的制备方法。

35、根据本发明的第五方面,提供一种微孔阵列。所述微孔阵列的每个微孔结构单元包括:asic衬底;金属层,位于所述asic衬底之上;钝化层,位于所述asic衬底之上;电极层,位于所述金属层和所述钝化层之上,完全覆盖所述金属层的顶部,并且覆盖所述钝化层的顶部的部分区域;第一介质层,位于所述钝化层和所述电极层之上,覆盖所述电极层的顶部的部分区域;第二介质层,位于第一介质层之上;微孔层,位于所述第二介质层之上。在所述微孔层、第二介质层和第一介质层中形成微孔,所述微孔从所述微孔层的顶部贯穿至所述电极层的顶部。所述微孔在第一介质层中的截面尺寸大于在第二介质层中的截面尺寸。

36、在根据本发明第五方面的微孔阵列中,优选地,所述微孔在微孔层中的截面尺寸不小于在第二介质层中的截面尺寸。

37、在根据本发明第五方面的微孔阵列中,优选地,在所述微孔层形成的微孔的截面尺寸为0.5~10μm,微孔的贯穿深度为0.2~10μm。

38、在根据本发明第五方面的微孔阵列中,优选地,所述第一介质层和第二介质层的材料包括以下至少一种:二氧化硅(sio2)、二氧化钛(tio2)、氮化硅(sin)、二氧化锆(zro2)、三氧化二铝(al2o3)、聚酰亚胺(pi)。

39、在根据本发明第五方面的微孔阵列中,优选地,所述电极层包括集流体层和集流体层之上的超级电容电极层。所述集流体层的材料包括以下至少一种:过渡金属薄膜、过渡金属氮化物薄膜、过渡金属与其氮化物的复合薄膜。所述超级电容电极层的材料包括在所述集流体层上形成的过渡金属的氮氧化物薄膜。所述过渡金属包括ti、v、ta、mo、hf中的至少一种。

40、在根据本发明第五方面的微孔阵列中,优选地,所述微孔层的材料包括以下材料中的至少一种:聚对二甲苯(pyralene)、特氟龙(teflon)、环烯烃类共聚物(coc)、类金刚石膜(dlc)、聚亚酰胺(pi)、环氧型光刻胶(su8)、聚对苯撑苯并二噁唑光刻胶(pbo)。

41、在根据本发明第五方面的微孔阵列中,优选地,所述微孔层包括:微孔层下层;微孔层上层,位于所述微孔层下层之上。在所述微孔层上层形成的微孔的截面尺寸大于在所述微孔层下层形成的微孔的截面尺寸。

42、优选地,在所述微孔层上层形成的微孔的截面尺寸为0.5~20μm,在所述微孔层下层形成的微孔的截面尺寸为0.5~10μm,所述微孔的贯穿深度为0.2~10μm。

43、根据本发明的第六方面,提供一种微孔阵列的制备方法。在所述方法中,通过以下步骤形成所述微孔阵列的每个微孔结构单元:提供asic衬底;在asic衬底上形成金属层;在asic衬底上形成钝化层;在所述金属层和所述钝化层上形成电极层,其中,暴露出所述钝化层的顶部的部分区域;在所述电极层的顶部以及暴露出的所述钝化层的顶部的部分区域上形成第一介质层;在所述第一介质层上形成第二介质层;在所述第二介质层上形成微孔层;贯穿所述微孔层、所述第二介质层和所述第一介质层形成微孔,暴露出电极层的顶部的部分区域;通过去除第一介质层的材料,使得所述微孔在第一介质层中的截面尺寸大于在第二介质层中的截面尺寸。

44、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述方法进一步包括:在提供asic衬底以及形成金属层和钝化层之后,对所述asic衬底顶部的金属层和钝化层表面进行平坦化。例如,可以使用化学机械抛光(cmp)技术或类似平坦化技术。

45、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述的形成电极层的步骤进一步包括:使电极层材料完全覆盖所述钝化层和所述金属层的顶部;以及去除部分电极层材料,暴露出钝化层的顶部的一部分。

46、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述的形成第一介质层的步骤进一步包括:在电极层上生长第一介质层,厚度为1~8μm。

47、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述的形成第二介质层的步骤进一步包括:使用pecvd、旋涂或者贴膜方式在第一介质层上形成第二介质层,厚度为0.2~10μm。

48、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述的形成电极层的步骤进一步包括:在所述金属层和所述钝化层上形成集流体层;和在所述集流体层上形成超级电容电极层。

49、优选地,使用磁控溅射的方式沉积形成厚度为10nm~4μm的tin以形成所述集流体层;和使用磁控溅射的方式沉积形成厚度为40nm~4μm的氮氧化钛以形成所述超级电容电极层。

50、在根据本发明第六方面的微孔阵列的制备方法中,优选地,所述的形成微孔层的步骤包括使用旋涂、贴膜形成一层有机材料层作为微孔层,厚度为0.2~10μm;所述的贯穿所述微孔层、所述第二介质层和所述第一介质层形成微孔的步骤包括对所述微孔的区域进行图形化以去除部分微孔层、部分第一介质层、部分第二介质层的材料,图形化的微孔截面尺寸为0.5~10μm。

51、优选地,所述微孔层的材料为su8或pbo。

52、此外,根据本发明第五方面的可选实施方式所对应的方法步骤也都适用于根据第六方面的微孔阵列的制备方法。

53、在以上的实施方案中,去除部分电极层材料以暴露出钝化层的顶部的一部分的步骤可以采用图形化来完成,更具体,可以使用光刻和刻蚀技术。

54、在可选的实施方案中,可以使用pecvd、旋涂或者贴膜方式形成第一介质层,厚度为0.1-10μm。

55、可以通过cmp或其他类似的平坦化技术如刻蚀等进行抛磨,其目的在于使第一介质层形成一个平整的表面。

56、在可选的实施方案中,还包括:使用pecvd、旋涂或者贴膜的方式形成所述第二介质层,厚度为0.1~10μm。

57、在可选的实施方案中,还包括:使用旋涂、贴膜形成微孔层,厚度为0.2~10μm。

58、在可选的实施方案中,还包括:使用光刻或刻蚀方法对所述微孔层和第二介质层进行图形化,图形化的微孔截面尺寸为0.5~10μm。

59、在可选的实施方案中,还包括:使用等离子体或者湿法去胶去除光刻胶并用清洗液对刻蚀过程中产生的有机聚合物进行去除,以保证电极层的完全暴露。

60、根据本公开的教导,在保持微孔截面尺寸不变的情况下,增加微孔中所暴露的电极层的表面积;或者在保持微孔中所暴露的电极层的表面积不变的情况下,减小微孔截面尺寸。由此,提升了电压驱动力和芯片集成度。

本文地址:https://www.jishuxx.com/zhuanli/20240619/533.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表