一种基于GIS盖板的三明治加速度计制备方法与流程

- 国知局

- 2024-07-27 12:43:17

一种基于gis盖板的三明治加速度计制备方法技术领域1.本发明涉及测量测试技术领域,具体涉及一种基于gis盖板的三明治加速度计制备方法。背景技术:2.基于mems技术的不断发展和推进,mems加速度计具有体积小、功耗低、交叉灵敏度低、可批量化生产等优势,并快速占领了石油勘探、消费电子、航空航天、汽车工业等领域。一般的mems加速度计分为电容式、谐振式、热对流式、光电式等检测原理,其中电容式检测原理具有梳齿式、三明治式和跷跷板式三种结构形式,梳齿式和跷跷板式结构复杂,制备难度大;三明治结构相对以上两者结构简单易制备,可以通过外围结构实现过阻尼控制,同时基于其结构形式的优势易实现大灵敏度。3.三明治mems加速度计通常采用硅-硅-硅三层或硅-玻璃-硅-玻璃-硅五层结构。其中硅-硅-硅三层结构以法国colibrys公司为代表,位于中间的硅质量块结构层与上下硅盖板层采用亲水键合技术实现高强度连接及气密封装,为了保证层间绝缘采用氧化硅作为介质层,通常氧化硅采用热氧化或化学气相沉积制备,氧化层厚度通常在5μm以内,且本身介电常数很大,因此在密封环区域会产生较大的寄生电容,通常寄生电容占到敏感芯片基础电容的一半以上,导致了较大的测量系统误差,但是该方案易于在晶片表面制备电极,可实现晶圆级批量筛选测试;而硅-玻璃-硅-玻璃-硅五层结构以日本村田公司为代表,位于中间的硅质量块结构层与上下盖板层采用阳极键合技术实现高强度连接及气密封装,上下盖板为硅-玻璃双层复合结构,玻璃作为连接和密封的介质层,厚度通常可以达到100μm以上,因此密封环区域寄生电容明显降低,但是基于该工艺方案的敏感芯片电极是在划片完成之后在侧面制备的,该工艺通用性差,且敏感芯片无法在晶圆级阶段实现批量筛选测试,降低了研发和生产效率。技术实现要素:4.本发明是为了解决寄生电容的问题,提供一种基于gis盖板的三明治加速度计制备方法,加速度计包括上盖板、下盖板和中间层敏感结构,上光刻腐蚀出多个单元图形,与玻璃片进行键合,通过回流、研磨、抛光等工序实现gis结构;结构硅晶片双面光刻湿法腐蚀出结构图形;将结构硅晶片中的结构图形、上下盖板硅晶片中与结构硅中结构图形对应的单元图形在设定气压、设定温度的键合设备内进行键合。本发明继承经典硅-玻璃-硅-玻璃-硅五层结构低寄生电容优势,同时实现了表面电极制备,使用基于与硅热膨胀系数更为接近的sd-2玻璃和ti金属电极,制造出寄生电容小、低应力的敏感芯片,同时实现晶圆级批量化性能测试。5.本发明提供一种基于gis盖板的三明治加速度计制备方法,包括以下步骤;6.s1、制备上盖板:使用热氧化工艺,在上盖板硅晶圆的表面生长二氧化硅绝缘层并单面光刻腐蚀出结构单元,采用玻璃回流填充和研磨抛光工艺得到上盖板玻璃层,使用单面光刻干法在上盖板玻璃层的上表面刻蚀出上盖板外电极极板,在上盖板外电极极板的上表面镀金属得到上盖板内电极,上盖板制备完成,上盖板玻璃层的材质为bf33/sd-2玻璃,上盖板内电极的材料为钛;7.s2、制备敏感层:在敏感层硅晶圆表面生长二氧化硅和氮化硅绝缘层,双面光刻腐蚀出结构单元并形成摆锤间隙结构,敏感层制备完成;8.s3、制备下盖板:使用热氧化工艺,在下盖板硅晶圆的表面生长二氧化硅绝缘层并单面光刻腐蚀出结构单元,采用玻璃回流填充和研磨抛光工艺得到下盖板玻璃层,使用单面光刻干法在下盖板玻璃层的上表面刻蚀出下盖板外电极极板,在下盖板外电极极板的上表面镀金属得到下盖板内电极,下盖板制备完成,上盖板玻璃层的材质为bf33/sd-2玻璃,下盖板内电极的材料为钛;9.s4、键合:将上盖板和下盖板中的结构图形与敏感层的结构图形对正后在真空或惰性气体环境下进行阳极键合,得到加速度计。10.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s1包括:11.s11、对上盖板硅晶圆本体进行标清清洗,使用热氧化工艺对上盖板硅晶圆本体双面镀氧化硅掩膜得到氧化硅掩膜层,然后进行匀胶光刻,将光刻胶未保护的氧化硅掩膜层去除;12.s12、放入koh溶液进行双面腐蚀,得到上盖板凸台结构;放入boe溶液中去除氧化硅掩膜层;13.s13、对上盖板玻璃层和上盖板硅晶圆进行标清清洗,将上盖板玻璃层和腐蚀出单元图形的上盖板硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,然后进行研磨抛光;14.s14、对复合片进行化学清洗和行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到上盖板外电极极板;15.s15、使用lift off方式镀上盖板内电极;16.s16、使用硬掩膜镀铝外电极,上盖板制备完成。17.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s12中,腐蚀温度为70℃-80℃,z向腐蚀速率为50-60μm/h。18.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,上盖板包括依次设置的上盖板硅晶圆、上盖板玻璃层、上盖板外电极极板和上盖板内电极,上盖板内电极面向敏感层,上盖板为gis盖板;19.上盖板硅晶圆包括上盖板硅晶圆本体和设置在上盖板硅晶圆本体表面的上盖板凸台结构。20.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s2包括:21.s21、将敏感层硅晶圆本体进行标清清洗,使用热氧化工艺在敏感层硅晶圆本体双面镀氧化硅掩膜得到氧化硅掩膜层;22.s22、进行匀胶光刻,放入boe溶液中去除光刻胶暴露出的氧化硅掩膜层;放入koh溶液进行双面腐蚀,腐蚀出浅槽结构;23.s23、去除全部氧化硅掩膜层,化学清洗之后在敏感层硅晶圆本体的两面均分别镀氧化硅得到氧化硅掩膜层、镀氮化硅得到氮化硅掩膜层,氧化硅掩膜层和氮化硅掩膜层形成掩膜层;进行二次光刻形成敏感层的图形,刻蚀掉光刻胶暴露出的氮化硅掩膜层和氧化硅掩膜层;24.s24、去除敏感层硅晶圆本体上的光刻胶,再次匀胶光刻,刻蚀掉光刻胶暴露出的氮化硅掩膜层;25.s25、去除光刻胶,将带有掩膜层的敏感层硅晶圆本体放入koh溶液中双面腐蚀得到摆锤间隙初始结构;26.s26、放入boe溶液中去除摆锤间隙初始结构的挠性梁上的氧化硅掩膜层,放入koh溶液中进行双面腐蚀,得到摆锤间隙结构;放入氢氟酸溶液中去除全部的氮化硅掩膜层和氧化硅掩膜层,敏感层制备完成。27.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s25中,腐蚀的温度为50℃-60℃,z向腐蚀速率为6-7μm/h;28.步骤s26中,腐蚀的温度为70℃-80℃,z向腐蚀速率为50-60μm/h。29.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,敏感层包括敏感层硅晶圆本体和设置在敏感层硅晶圆本体中的摆锤间隙结构;30.摆锤间隙结构包括单梁结构、双梁结构和四梁结构。31.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s3包括:32.s31、对下盖板硅晶圆本体进行标清清洗,使用热氧化工艺对下盖板硅晶圆本体双面镀氧化硅掩膜得到氧化硅掩膜层,然后进行匀胶光刻,将光刻胶未保护的氧化硅掩膜层去除;33.s32、放入koh溶液进行双面腐蚀,得到下盖板凸台结构;放入boe溶液中去除氧化硅掩膜层;34.s33、对下盖板玻璃层和下盖板硅晶圆进行标清清洗,将下盖板玻璃层和腐蚀出单元图形的下盖板硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,然后进行研磨抛光;35.s34、对复合片进行化学清洗和行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到下盖板外电极极板;36.s35、使用lift off方式镀下盖板内电极;37.s36、使用硬掩膜镀铝外电极,下盖板制备完成。38.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,步骤s32中,腐蚀温度为70℃-80℃,z向腐蚀速率为50-60μm/h;39.步骤s4中键合的温度为330℃以上。40.本发明所述的一种基于gis盖板的三明治加速度计制备方法,作为优选方式,下盖板包括依次设置的下盖板硅晶圆、下盖板玻璃层、下盖板外电极极板和下盖板内电极,下盖板内电极面向敏感层,下盖板为gis盖板;41.下盖板硅晶圆包括下盖板硅晶圆本体和设置在下盖板硅晶圆本体表面的下盖板凸台结构。42.本发明提供了一种基于gis盖板的三明治加速度计制备方法,该方法包括以下步骤:43.(1)采用热氧化工艺,在上盖板硅晶圆表面生长二氧化硅绝缘层,单面光刻腐蚀出结构单元;采用玻璃回流填充和研磨抛光工艺得到gis盖板;单面光刻干法刻蚀出外电极极板;在gis盖板镀金属内电极。44.(2)采用热氧化工艺,在下极板硅晶圆表面生长二氧化硅绝缘层,单面光刻腐蚀出结构单元;采用玻璃回流填充和研磨抛光工艺得到gis盖板;单面光刻干法刻蚀出外电极极板;在gis盖板镀金属内电极。45.(3)在中间层硅晶圆表面生长二氧化硅和氮化硅绝缘层,双面光刻腐蚀出结构单元。46.(4)将结构硅晶片中的结构图形、上下盖板硅晶片中与结构硅中结构图形对应的单元图形进行阳极键合。47.一、敏感层的制备过程如下:48.(1)先对硅晶圆进行标清清洗,采用热氧化工艺在晶圆双面镀氧化硅薄膜;49.(2)进行匀胶光刻,放入boe溶液中去除光刻胶暴露出的氧化硅掩膜;放入koh溶液进行双面腐蚀,腐蚀出浅槽结构;50.(3)去除氧化硅掩膜层,化学清洗之后在硅晶圆的两面分别镀氧化硅和氮化硅,形成掩膜层;进行二次光刻形成敏感层的图形,刻蚀掉光刻胶暴露出的氮化硅和氧化硅掩膜;51.(4)去除敏感结构上的光刻胶,再次匀胶光刻,刻蚀掉光刻胶暴露出的氮化硅掩膜;52.(5)去除光刻胶,将带有掩膜层的硅晶圆放入koh溶液中双面腐蚀出摆锤间隙结构;如图3所示为双面腐蚀摆锤间隙示意图,其中低温腐蚀的温度为50℃-60℃,z向腐蚀速率为6-7μm/h。53.(6)放入boe溶液中去除挠性梁上的氧化硅掩膜,放入koh溶液中进行双面腐蚀,得到摆锤结构;放入氢氟酸溶液中去除氮化硅和氧化硅掩膜;其中高温腐蚀的温度为70℃-80℃,z向腐蚀速率为50-60μm/h。54.二、下盖板的制备过程:55.(1)对硅晶圆进行标清清洗,采用热氧化工艺对晶圆双面镀氧化硅掩膜;进行匀胶光刻,将光刻胶未保护的掩膜部分去除;56.(2)放入koh溶液进行双面腐蚀,得到凸台结构;放入boe溶液中去除氧化硅掩膜;其中高温腐蚀70℃-80℃,z向腐蚀速率为50-60μm/h。57.(3)对bf33/sd-2玻璃和硅晶圆进行标清清洗,将bf33/sd-2玻璃和腐蚀出单元图形的硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,之后进行研磨抛光,得到gis下盖板;58.(4)对gis盖板进行化学清洗,进行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到下盖板外电极;59.(5)采用lift off方式镀ti内电极;60.(6)采用硬掩膜镀铝外电极。61.三、上盖板制备过程:62.(1)对硅晶圆进行标清清洗,采用热氧化工艺对晶圆双面镀氧化硅掩膜;进行匀胶光刻,将光刻胶未保护的掩膜部分去除;63.(2)放入koh溶液进行双面腐蚀,得到凸台结构;放入boe溶液中去除氧化硅掩膜;其中高温腐蚀70℃-80℃,z向腐蚀速率为50-60μm/h。64.(3)对bf33/sd-2玻璃和硅晶圆进行标清清洗,将bf33/sd-2玻璃和腐蚀出单元图形的硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,之后进行研磨抛光,得到gis上盖板;65.(4)对gis盖板进行化学清洗,进行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到上盖板外电极;66.(5)采用lift off方式镀ti内电极2;67.(6)采用硬掩膜镀铝外电极。68.四、三层键合制备过程:69.将中间层晶圆和上下盖板在键合对准机上进行对准,温度为330℃以上,并在真空或惰性气体环境下进行键合。70.本发明具有以下优点:71.(1)继承经典硅-玻璃-硅-玻璃-硅五层结构低寄生电容优势,同时实现了表面电极制备,避免在划片后通过侧面电极实现电信号引出,解决经典硅-玻璃-硅-玻璃-硅五层结构无法晶圆级检测的瓶颈问题;72.(2)gis盖板使用基于与硅热膨胀系数更为接近的sd-2玻璃制备,与硅-玻璃-硅-玻璃-硅五层结构的经典对称平衡设计相结合,可以显著提升三明治加速度计的全温零位漂移性能指标。73.(3)上下gis盖板与敏感层相对的电容电极采用ti金属,与硅本身具有优秀的黏附性,同时可以作为非蒸散型金属吸气剂,可以实现微小密封腔体内真空或惰性气体气压的长期维持,可以明显提升三明治加速度计的长期稳定性。74.(4)本发明能够制造出寄生电容小、低应力的敏感芯片,同时可实现晶圆级批量化性能测试。附图说明75.图1为一种基于gis盖板的三明治加速度计制备方法流程图;76.图2为一种基于gis盖板的三明治加速度计结构示意图;77.图3为一种基于gis盖板的三明治加速度计结构爆炸图;78.图4a为一种基于gis盖板的三明治加速度计制备方法步骤s11结构示意图;79.图4b为一种基于gis盖板的三明治加速度计制备方法步骤s12结构示意图;80.图4c为一种基于gis盖板的三明治加速度计制备方法步骤s13结构示意图;81.图4d为一种基于gis盖板的三明治加速度计制备方法步骤s14结构示意图;82.图4e为一种基于gis盖板的三明治加速度计制备方法步骤s15结构示意图;83.图5a为一种基于gis盖板的三明治加速度计制备方法步骤s21结构示意图;84.图5b为一种基于gis盖板的三明治加速度计制备方法步骤s22结构示意图;85.图5c为一种基于gis盖板的三明治加速度计制备方法步骤s23结构示意图;86.图5d为一种基于gis盖板的三明治加速度计制备方法步骤s24结构示意图;87.图5e为一种基于gis盖板的三明治加速度计制备方法步骤s25结构示意图;88.图5f为一种基于gis盖板的三明治加速度计制备方法步骤s26结构示意图;89.图5g为一种基于gis盖板的三明治加速度计制备方法摆锤间隙结构示意图示意图;90.图6a为一种基于gis盖板的三明治加速度计制备方法步骤s31结构示意图;91.图6b为一种基于gis盖板的三明治加速度计制备方法步骤s32结构示意图;92.图6c为一种基于gis盖板的三明治加速度计制备方法步骤s33结构示意图;93.图6d为一种基于gis盖板的三明治加速度计制备方法步骤s34结构示意图;94.图6e为一种基于gis盖板的三明治加速度计制备方法步骤s35结构示意图;95.图7为一种基于gis盖板的三明治加速度计制备方法步骤s4键合示意图。96.附图标记:97.1、上盖板;11、上盖板硅晶圆;111、上盖板硅晶圆本体;112、上盖板凸台结构;12、上盖板玻璃层;13、上盖板外电极极板;14、上盖板内电极;2、敏感层;21、敏感层硅晶圆本体;22、摆锤间隙结构;3、下盖板;31、下盖板硅晶圆;311、下盖板硅晶圆本体;312、下盖板凸台结构;32、下盖板玻璃层;33、下盖板外电极极板;34、下盖板内电极;a、氧化硅掩膜层;b、光刻胶;c、浅槽结构;d、氮化硅掩膜层;e、摆锤间隙初始结构。具体实施方式98.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。99.实施例1100.如图1所示,一种基于gis盖板的三明治加速度计制备方法,包括以下步骤;101.s1、制备上盖板:使用热氧化工艺,在上盖板硅晶圆11的表面生长二氧化硅绝缘层并单面光刻腐蚀出结构单元,采用玻璃回流填充和研磨抛光工艺得到上盖板玻璃层12,使用单面光刻干法在上盖板玻璃层12的上表面刻蚀出上盖板外电极极板13,在上盖板外电极极板13的上表面镀金属得到上盖板内电极14,上盖板1制备完成,上盖板玻璃层12的材质为bf33/sd-2玻璃,上盖板内电极14的材料为钛;102.如图2-3所示,上盖板1包括依次设置的上盖板硅晶圆11、上盖板玻璃层12、上盖板外电极极板13和上盖板内电极14,上盖板内电极14面向敏感层2,上盖板1为gis盖板;103.上盖板硅晶圆11包括上盖板硅晶圆本体111和设置在上盖板硅晶圆本体111表面的上盖板凸台结构112;104.s11、对上盖板硅晶圆本体111进行标清清洗,使用热氧化工艺对上盖板硅晶圆本体111双面镀氧化硅掩膜得到氧化硅掩膜层a,然后进行匀胶光刻,将光刻胶b未保护的氧化硅掩膜层a去除;去除氧化硅掩膜的结构如图4a所示;105.s12、放入koh溶液进行双面腐蚀,得到上盖板凸台结构112;放入boe溶液中去除氧化硅掩膜层a;腐蚀温度为70℃-80℃,z向腐蚀速率为50-60μm/h;上盖板凸台结构112如图4b所示;106.s13、对上盖板玻璃层12和上盖板硅晶圆11进行标清清洗,将上盖板玻璃层12和腐蚀出单元图形的上盖板硅晶圆11进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,然后进行研磨抛光;玻璃回流盖板后结构如图4c所示;107.s14、对复合片进行化学清洗和行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到上盖板外电极极板13;上盖板外电极13的结构如图4d所示;108.s15、使用lift off方式镀上盖板内电极14;上盖板内电极14的结构如图4e所示;109.s16、使用硬掩膜镀铝外电极,上盖板1制备完成;110.s2、制备敏感层:在敏感层硅晶圆21表面生长二氧化硅和氮化硅绝缘层,双面光刻腐蚀出结构单元并形成摆锤间隙结构22,敏感层2制备完成;111.s21、将敏感层硅晶圆本体21进行标清清洗,使用热氧化工艺在敏感层硅晶圆本体21双面镀氧化硅掩膜得到氧化硅掩膜层a,结构如图5a所示;112.s22、进行匀胶光刻,放入boe溶液中去除光刻胶b暴露出的氧化硅掩膜层a;放入koh溶液进行双面腐蚀,腐蚀出浅槽结构c,结构如图5b所示;113.s23、去除全部氧化硅掩膜层a,化学清洗之后在敏感层硅晶圆本体21的两面均分别镀氧化硅得到氧化硅掩膜层a、镀氮化硅得到氮化硅掩膜层d,氧化硅掩膜层a和氮化硅掩膜层d形成掩膜层;进行二次光刻形成敏感层的图形,刻蚀掉光刻胶b暴露出的氮化硅掩膜层d和氧化硅掩膜层a,结构如图5c所示;114.s24、去除敏感层硅晶圆本体21上的光刻胶b,再次匀胶光刻,刻蚀掉光刻胶b暴露出的氮化硅掩膜层d,结构如图5d所示;115.s25、去除光刻胶b,将带有掩膜层的敏感层硅晶圆本体21放入koh溶液中双面腐蚀得到摆锤间隙初始结构e;腐蚀的温度为50℃-60℃,z向腐蚀速率为6-7μm/h,双面腐蚀摆锤间隙示意图如图5e所示;116.s26、放入boe溶液中去除摆锤间隙初始结构e的挠性梁上的氧化硅掩膜层a,放入koh溶液中进行双面腐蚀,腐蚀的温度为70℃-80℃,z向腐蚀速率为50-60μm/h,得到摆锤间隙结构22;放入氢氟酸溶液中去除全部的氮化硅掩膜层c和氧化硅掩膜层a,结构如图5f所示,摆锤间隙结构22如图5g所示,敏感层2制备完成;117.敏感层2包括敏感层硅晶圆本体21和设置在敏感层硅晶圆本体21中的摆锤间隙结构22;118.摆锤间隙结构22包括单梁结构、双梁结构和四梁结构;119.s3、制备下盖板:使用热氧化工艺,在下盖板硅晶圆31的表面生长二氧化硅绝缘层并单面光刻腐蚀出结构单元,采用玻璃回流填充和研磨抛光工艺得到下盖板玻璃层32,使用单面光刻干法在下盖板玻璃层32的上表面刻蚀出下盖板外电极极板33,在下盖板外电极极板33的上表面镀金属得到下盖板内电极34,下盖板3制备完成,上盖板玻璃层32的材质为bf33/sd-2玻璃,下盖板内电极34的材料为钛;120.s31、对下盖板硅晶圆本体311进行标清清洗,使用热氧化工艺对下盖板硅晶圆本体311双面镀氧化硅掩膜得到氧化硅掩膜层a,然后进行匀胶光刻,将光刻胶b未保护的氧化硅掩膜层a去除;去除氧化硅掩膜的结构如图6a所示;121.s32、放入koh溶液进行双面腐蚀,得到下盖板凸台结构312;放入boe溶液中去除氧化硅掩膜层a;腐蚀温度为70℃-80℃,z向腐蚀速率为50-60μm/h;下盖板凸台结构312如图6b所示;122.s33、对下盖板玻璃层32和下盖板硅晶圆31进行标清清洗,将下盖板玻璃层32和腐蚀出单元图形的下盖板硅晶圆31进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,然后进行研磨抛光;玻璃回流盖板后结构如图6c所示;123.s34、对复合片进行化学清洗和行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到下盖板外电极极板33;下盖板外电极极板33的结构如图6d所示;124.s35、使用lift off方式镀下盖板内电极34;下盖板内电极34的结构如图6e所示;125.s36、使用硬掩膜镀铝外电极,下盖板3制备完成;126.下盖板3包括依次设置的下盖板硅晶圆31、下盖板玻璃层32、下盖板外电极极板33和下盖板内电极34,下盖板内电极34面向敏感层2,下盖板3为gis盖板;127.下盖板硅晶圆31包括下盖板硅晶圆本体311和设置在下盖板硅晶圆本体311表面的下盖板凸台结构312;128.s4、键合:将上盖板1和下盖板3中的结构图形与敏感层2的结构图形对正后在真空或惰性气体环境下进行阳极键合,键合的温度为330℃以上,得到加速度计。129.实施例2130.如图1所示,一种基于gis盖板的三明治加速度计制备方法,包括以下步骤;131.(1)采用热氧化工艺,在上盖板硅晶圆表面生长二氧化硅绝缘层,单面光刻腐蚀出结构单元;采用玻璃回流填充和研磨抛光工艺得到gis盖板;单面光刻干法刻蚀出外电极极板;在gis盖板镀金属内电极。132.(2)采用热氧化工艺,在下极板硅晶圆表面生长二氧化硅绝缘层,单面光刻腐蚀出结构单元;采用玻璃回流填充和研磨抛光工艺得到gis盖板;单面光刻干法刻蚀出外电极极板;在gis盖板镀金属内电极。133.(3)在中间层硅晶圆表面生长二氧化硅和氮化硅绝缘层,双面光刻腐蚀出结构单元。134.(4)将结构硅晶片中的结构图形、上下盖板硅晶片中与结构硅中结构图形对应的单元图形进行阳极键合。135.敏感层的制备过程如下:136.(1)先对硅晶圆11进行标清清洗,采用热氧化工艺在晶圆双面镀氧化硅薄膜,结构如图5a所示;137.(2)进行匀胶光刻,放入boe溶液中去除光刻胶暴露出的氧化硅掩膜;放入koh溶液进行双面腐蚀,腐蚀出浅槽结构,结构如图5b所示;138.(3)去除氧化硅掩膜层,化学清洗之后在硅晶圆的两面分别镀氧化硅和氮化硅,形成掩膜层;进行二次光刻形成敏感层的图形,刻蚀掉光刻胶暴露出的氮化硅和氧化硅掩膜,结构如图5c所示;139.(4)去除敏感结构上的光刻胶,再次匀胶光刻,刻蚀掉光刻胶暴露出的氮化硅掩膜,结构如图5d所示;140.(5)去除光刻胶,将带有掩膜层的硅晶圆放入koh溶液中双面腐蚀出摆锤间隙结构;如图5e所示为双面腐蚀摆锤间隙示意图,其中低温腐蚀的温度为50℃-60℃,z向腐蚀速率为6-7μm/h。141.(6)放入boe溶液中去除挠性梁上的氧化硅掩膜,放入koh溶液中进行双面腐蚀,得到摆锤结构;放入氢氟酸溶液中去除氮化硅和氧化硅掩膜;结构如图5f所示,摆锤间隙结构22如图5g所示,其中高温腐蚀的温度为70℃-80℃,z向腐蚀速率为50-60μm/h。下盖板的制备过程:142.(1)对硅晶圆进行标清清洗,采用热氧化工艺对晶圆双面镀氧化硅掩膜;进行匀胶光刻,将光刻胶未保护的掩膜部分去除;去除氧化硅掩膜的结构如图6a所示;143.(2)放入koh溶液进行双面腐蚀,得到凸台结构;放入boe溶液中去除氧化硅掩膜;其中高温腐蚀70℃-80℃,z向腐蚀速率为50-60μm/h;下盖板凸台结构312如图6b所示;144.(3)对bf33/sd-2玻璃和硅晶圆进行标清清洗,将bf33/sd-2玻璃和腐蚀出单元图形的硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,之后进行研磨抛光,得到gis下盖板;玻璃回流盖板后结构如图6c所示;145.(4)对gis盖板进行化学清洗,进行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到下盖板外电极;下盖板外电极极板33的结构如图6d所示;146.(5)采用lift off方式镀ti内电极;下盖板内电极34的结构如图6e所示;147.(6)采用硬掩膜镀铝外电极。148.上盖板制备过程:149.(1)对硅晶圆进行标清清洗,采用热氧化工艺对晶圆双面镀氧化硅掩膜;进行匀胶光刻,将光刻胶未保护的掩膜部分去除;去除氧化硅掩膜的结构如图4a所示;150.(2)放入koh溶液进行双面腐蚀,得到凸台结构;放入boe溶液中去除氧化硅掩膜;其中高温腐蚀70℃-80℃,z向腐蚀速率为50-60μm/h,上盖板凸台结构112如图4b所示;151.(3)对bf33/sd-2玻璃和硅晶圆进行标清清洗,将bf33/sd-2玻璃和腐蚀出单元图形的硅晶圆进行阳极键合,键合完成之后进行化学清洗;将键合完成之后的复合片放入管式炉之后进行高温回流填充,之后进行研磨抛光,得到gis上盖板;玻璃回流盖板后结构如图4c所示;152.(4)对gis盖板进行化学清洗,进行匀胶光刻,采用icp设备对玻璃和硅进行干法刻蚀,得到上盖板外电极;上盖板外电极13的结构如图4d所示;153.(5)采用lift off方式镀ti内电极2;上盖板内电极14的结构如图4e所示;154.(6)采用硬掩膜镀铝外电极。155.三层键合制备过程:156.将中间层晶圆和上下盖板在键合对准机上进行对准,温度为330℃以上,并在真空或惰性气体环境下进行键合。157.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123215.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

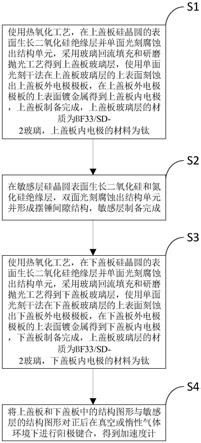

返回列表