微电子密封件内的屏障结构的制作方法

- 国知局

- 2024-07-27 12:45:17

微电子密封件内的屏障结构1.相关申请的交叉引用2.本技术要求美国临时专利申请号63/134,655的优先权,该专利申请在2021年1月7日提交,名称为“physical barrier structure formed within a microelectronic enclosure”,并且由此通过引用以其整体并入本文。背景技术:3.半导体器件使用各种液体或蒸气材料来制造。成品半导体器件还可在器件内具有不同划定区域,这些区域都在密封体积内。在制造期间,液体或蒸气材料可在半导体器件的不同划定区域中移动。技术实现要素:4.根据本说明书的至少一个示例,一种方法包括在第一衬底的至少一部分上施加介电材料。所述方法还包括在所述第一衬底的所述至少一部分上沉积籽晶金属。所述方法还包括在籽晶金属上沉积镀覆光致抗蚀剂。所述方法还包括在所述籽晶金属上镀覆金属线,其中所述镀覆光致抗蚀剂形成所述金属线的边界,并且其中所述金属线形成屏障结构的至少一部分。所述方法还包括剥离所述镀覆光致抗蚀剂的至少一部分并蚀刻所述籽晶金属的至少一部分。所述方法还包括相对于所述屏障结构定位第二衬底以形成腔室。5.根据本说明书的至少一个示例,一种器件包括第一衬底。所述器件还包括屏障结构,所述屏障结构包括位于所述第一衬底上的金属层,其中所述屏障结构形成腔室。所述器件还包括第二衬底,所述第二衬底位于所述金属层上,其中所述金属层在所述第一衬底和所述第二衬底之间延伸,并且其中所述金属层包括在所述腔室内接触所述第一衬底的倾斜边缘。6.根据本说明书的至少一个示例,一种器件包括半导体器件,所述半导体器件位于第一衬底上。所述器件还包括籽晶金属,所述籽晶金属位于所述第一衬底上。所述器件还包括金属线,所述金属线位于所述籽晶金属上。所述器件还包括一个或多个金属层,所述一个或多个金属层堆叠在所述金属线上,其中第二衬底定位在所述一个或多个金属层中的至少一者上方,所述第二衬底覆盖所述半导体器件。所述器件还包括屏障结构,所述屏障结构包括所述金属线,其中所述屏障结构在所述第一衬底和所述第二衬底之间延伸以形成所述半导体器件位于其中的腔室,并且其中所述屏障结构包括倾斜边缘,所述第一衬底接触所述倾斜边缘的一端。附图说明7.图1a是根据各种示例的具有屏障结构的器件。8.图1b是根据各种示例的具有屏障结构的器件。9.图2是根据各种示例的屏障结构的放大视图。10.图3a-图3e示出了根据各种示例的用于产生屏障结构的过程流程。11.图4是根据各种示例的具有屏障结构的器件和不具有屏障结构的器件的缺陷计数的曲线图。12.图5是根据各种示例的用于产生屏障结构的方法的流程图。具体实施方式13.在一些半导体器件中,在制造期间,液体或蒸气材料在器件的不同区域之间的转移可引起可损坏器件的化学相互作用。例如,半导体器件可具有经由氧化物层和各种金属层来彼此耦接的两个晶片。在半导体器件的制造期间使用的化学物质可与金属层相互作用并产生不期望的污染物。一种此类污染物是与铟反应而引起的铟盐。这种污染物可在制造期间或之后损坏半导体器件并且导致可靠性问题。14.在本文的示例中,围绕半导体封装的某些元件的屏障结构防止液体或蒸气材料在制造期间在半导体器件的不同划定区域之间或其中移动。半导体器件的元件可在一个区内,该区在其周边附近被密封。通过本文所述的技术,可减小不相容材料的相互作用。作为一个示例,屏障结构可延缓存在于器件的一个区中的贱金属被存在于器件的不同区中的酸或碱腐蚀。屏障结构在物理上分离当两个单片衬底键合时产生的不同区或腔室区域。减小或消除了流体和蒸气在不同区或腔室区域之间的转移。在本文的一个示例中,可通过在逐渐倾斜的介电边缘之上溅射和镀覆金属以形成接触衬底的金属倾斜边缘来形成屏障结构。15.图1a是根据各种示例的具有屏障结构的器件100。器件100的示例包括微机械开关,诸如在数字微镜器件(dmd)中存在的那些微机械开关。器件100包括微型环境102,该微型环境通过屏障结构106与外部环境104(例如,在微型环境102的外部)分开。器件100包括晶片108、晶片110、半导体器件112、氮化钛层113、晶片114和介电层115。在一个示例中,晶片108可以是玻璃晶片。在一个示例中,晶片110可以是硅晶片。在一个示例中,晶片114可以是互补金属氧化物半导体(cmos)晶片。在一个示例中,半导体器件112可以是微机电系统(mems)器件。半导体器件112的其他示例包括微流控器件、片上实验室器件、激光阵列、相位调制器、微型气相色谱仪、谐振器或光学传感器。介电层115可包括任何数量的层,并且可如图1a所示的那样图案化。在一个示例中,介电层115可以是氧化物层。器件100还包括氧化物层116、籽晶金属118、镀覆键合线120(例如,金属线)、金属层122和金属层124。介电材料126和污染物128也在图1a中示出。在一些示例中,籽晶金属118可以是许多类型的金属层或合金中的任何一种,诸如钛-铜(ti-cu)、镍-钨(ni-w)、钛-钨(ti-w)或金。在一个示例中,籽晶金属118的厚度可在0.2微米和0.3微米之间。在一些示例中,镀覆键合线120可以是金-铟(au-in)、铜-锡(cu-sn)、金-锡(au-sn)、金-锗(au-ge)、铝-锗(al-ge)或任何其他合适的材料。在一些示例中,金属层122可以是铟层或锡层。在该示例中,污染物128被示出在由屏障结构106产生的镀覆键合线120和氧化物层116之间的空区内。在本文的示例中,屏障结构106使污染物128远离半导体器件112。16.在一些示例中,微型环境102(例如,腔室区域)是不透气密封的。本文的微型环境102包括半导体器件112。在一个示例中,半导体器件112可以是dmd。在另一个示例中,微型环境102可包括除mems器件之外的器件,诸如在密封环境中发现的任何半导体器件。微型环境102保护半导体器件112免受可损坏半导体器件112的材料,诸如污染物128。在一个示例中,在制造期间在微型环境102内使用的液体或蒸气可与金属层122反应并产生盐,例如,如果金属层122是铟,则产生铟盐。例如,酸可施加到晶片114以润滑半导体器件112,从而用于在其寿命期间的机械操作。该酸可与金属层122的铟相互作用以产生铟盐。在其他示例中,其他类型的金属可与酸相互作用并产生污染物,诸如如果用锡代替金属层122。此外,上面相对于籽晶金属118和镀覆键合线120描述的一些金属也可与酸相互作用以产生污染物。铟盐(或其他污染物)由污染物128表示。如果污染物128迁移到半导体器件112,则半导体器件112可能被损坏。屏障结构106防止或减小污染物128的迁移。17.屏障结构106通过以下方式来形成:使籽晶金属118和镀覆键合线120在介电材料126之上延伸,以及然后移除介电材料126的一些或全部以完成微型环境102。在一个示例中,介电材料126可以是光致抗蚀剂。下面描述了屏障结构106的形成的细节。通过使镀覆键合线120在介电材料126之上延伸,在镀覆键合线120和氧化物层116之间存在接触或接近接触。由于这种接触或接近接触,微型环境102中的化学物质可能不会与金属层122相互作用,这防止将污染物128引入到器件100中。在一些示例中,接近接触可足以防止由于毛细管压力而引起的污染物移动,如下所述。如果化学物质确实与金属层122相互作用,则屏障结构106将污染物128捕获在微型环境102之外,因此污染物128不迁移到半导体器件112。在该示例中,一些介电材料126可保持在屏障结构106旁边。然而,在其他示例中,介电材料126可从屏障结构106下面完全移除。18.在此示例中,晶片108覆盖微型环境102并允许来自器件100外部的光到达半导体器件112。晶片110被图案化以产生通过晶片108到半导体器件112的透视窗口,这就是晶片110在图1a中被示为不直接在半导体器件112之上的原因。图案化移除了晶片110的直接位于半导体器件112之上的部分,因此来自器件100外部的光可通过晶片110中的间隙到达半导体器件112。外部环境104表示在微型环境102之外的环境。屏障结构106将微型环境102与外部环境104分开以为半导体器件112提供密封腔室。在其他示例中,覆盖和密封微型环境102的材料可以不是晶片108和晶片110。材料可以是任何盖、晶片、窗口或第二衬底,其中第一衬底在此示例中是晶片114。19.如下所述,通过沉积和图案化包括介电材料126的各种层来形成屏障结构106和微型环境102。在一个示例中,籽晶金属118可包括一种或多种溅射金属诸如钛和铜。在器件100中,介电材料126和籽晶金属118之间的边界被示为弯曲屏障。图1a中所示的元件不是按比例的,并且介电材料126和籽晶金属118之间的边界在其他示例中可具有另一个形状。例如,在一个示例中,边界可以是相对于介电层115不超过45度的缓斜率,由图1a中的角θ表示。在其他示例中,屏障结构106的斜率可甚至更小,诸如具有针对在水平方向上的每两微米至十微米会在垂直方向上增加一微米的高度。如果斜率大于45度,可能难以沉积均匀的籽晶金属118。大于45度的斜率也可导致其中籽晶金属从介电层115上的平坦表面阶跃到涂覆介电材料126的区域附近的缺陷。20.在一些示例中,介电材料126可具有低粗糙度,诸如小于10纳米ra(粗糙度平均值)。在一些示例中,镀覆键合线120可具有小于20纳米ra的粗糙度。21.图1b是根据各种示例的具有屏障结构的器件。图1b示出了器件150的三个视图,该器件是诸如图1a中的器件100的器件。器件150包括腔室内的mems器件152。mems器件152处于第一衬底154和第二衬底156之间。mems器件152被屏障结构158围绕,在一个示例中,该屏障结构可以是屏障结构106。22.在图1b的左侧,示出了器件150,其中第一衬底154和第二衬底156彼此分开。在该示例中,mems器件152处于第二衬底156上。如上所述,屏障结构158有助于保护mems器件152在制造期间免受污染。在另一个示例中,不同的半导体器件可替代mems器件驻留在第二衬底156上。在图1b的右上方,第一衬底154和第二衬底156对准但尚未彼此耦接以形成针对mems器件152的密封腔室。图1b的右下角示出了器件150,其中第一衬底154和第二衬底156已经形成针对mems器件152的密封腔室。mems器件152收到由第一衬底154和第二衬底156形成的密封腔室的保护。23.图2是根据各种示例的器件(诸如器件100)的一部分的放大视图200。放大视图200示出微型环境202、屏障结构204、玻璃晶片206、硅晶片208、氧化物210、cmos晶片212、氮化钛层213、籽晶金属214、氧化物层215、镀覆键合线216(例如,金属线)、光致抗蚀剂218和间隙220。图2中的部件与图1a中的其对应部件类似地操作。图2中的部件可如下所述的那样制造。24.屏障结构204减小或防止微型环境202的污染(图2中未示出),类似于图1a中的屏障结构106。然而,在该示例中,屏障结构204不接触氧化物210。相反,屏障结构204靠近氧化物210,在一个示例中处于两微米或更小的范围内。屏障结构204和氧化物210在它们之间形成间隙220。如果间隙220具有足够的纵横比,则间隙220形成可捕获试图穿过屏障结构204的流体或蒸气的毛细管。流体或蒸气的穿过屏障结构204的进一步传输被捕获在间隙220内的流体或蒸气的毛细管压力阻碍。在一个示例中,形成毛细管的间隙220的纵横比可具有25微米或更大的宽度,并且可具有1微米或更小的高度。因此,屏障结构204不必接触氧化物210以减少或防止微型环境202的污染。如果间隙的高度太大,毛细管压力可能不会阻碍流体或蒸气的穿过间隙的传输。25.图3a至图3e示出了根据本文的各种示例的用于产生屏障结构(诸如屏障结构106和204)的过程流程。图3a至图3e示出了可执行以构造如本文所述的屏障结构的步骤。在其他示例中,可执行附加步骤,可移除某些步骤,或者可以另一个适当顺序执行这些步骤。图3a至图3e中的部件不一定按比例。另外,下面描述的金属层和抗蚀剂层中的每一者可表示单层材料或堆叠在一起的多层材料。26.图3a是半导体器件300,其包括cmos晶片304上的钛层301、mems器件302和氧化物层303。光致抗蚀剂306或另一种介电材料在半导体器件300的至少一部分上图案化以涂覆mems器件302并为将要制造的屏障结构创建基础。覆盖mems器件302的光致抗蚀剂306还具有沿用于形成屏障结构的倾斜边缘的斜率308。如上所述,在一些示例中,斜率308可以是45度或更小的缓斜率。这里,斜率308被示为更陡的斜率,因此可更容易地看到半导体器件300的部件。比45度更陡的斜率可能会使得难以沉积均匀的籽晶金属。大于45度的斜率可导致其中籽晶金属从氧化物层303上的平坦表面阶跃到涂覆光致抗蚀剂306的区域附近的缺陷。27.在一个示例中,光致抗蚀剂306具有在衬底(例如,cmos晶片304)上方的介于4微米至5微米之间的最大厚度309。太厚的光致抗蚀剂可导致在光致抗蚀剂中形成气泡。在一些示例中,可在上面提供的范围内增加或减少厚度以满足屏障结构的金属键合或柔顺的任何要求。在一些示例中,光致抗蚀剂306的最终阻挡结构可通过施加多个光致抗蚀剂层和光刻过程来创建。在一个示例中,使用三个单独的光致抗蚀剂层,其中顶层仅在图3a所示的开放区域中被图案化(例如,被移除)。然后可向下蚀刻整个光致抗蚀剂主体以揭露在图3a所示的光致抗蚀剂306之间的开放区域中的金属线(例如,籽晶金属310和金属线314,在如下所述的稍后步骤中沉积)。光致抗蚀剂306的斜率308由图案化和蚀刻过程的组合确定。在一个示例中,来自第三光致抗蚀剂层的图案可经由蚀刻转移到第一光致抗蚀剂层和第二光致抗蚀剂层中。第一层、第二层和第三层的剩余光致抗蚀剂形成光致抗蚀剂306的全部或部分。在其他示例中,可使用不同数量的层来产生光致抗蚀剂306的阻挡结构。28.图3b示出了半导体器件300,其中籽晶金属310沉积在半导体器件300上。籽晶金属310有利于镀覆籽晶金属310上方的层。籽晶金属310的材料和厚度可基于应用而变化。在一些示例中,钛、铜、镍或金用于籽晶金属310。金属的组合可用于籽晶金属310。在一些实施例中,籽晶金属310和籽晶金属310上的其他金属的组合厚度(下面描述)可约为6微米。在另一个示例中,厚度介于5.5微米和6.5微米之间。在一些示例中,籽晶金属310的厚度沿着光致抗蚀剂306的顶部和/或沿着光致抗蚀剂306的倾斜边缘是均匀的。在一些示例中,籽晶金属310在光致抗蚀剂306之上的电连续性和厚度均匀性是通过光致抗蚀剂306的缓斜率308来实现的。继而,在籽晶金属310顶部上的附加层(下面描述)的厚度在衬底和屏障结构两者上也是均匀的。厚度均匀性允许屏障结构和其他特征的尺寸是可重复和可制造的。金属的组合厚度可为后续步骤中执行的镀覆过程提供良好的附着和导电性。29.图3c示出了半导体器件300,其中镀覆光致抗蚀剂312在光致抗蚀剂306和籽晶金属310上图案化。镀覆光致抗蚀剂312的厚度介于4微米至5微米之间。在一个示例中,4微米至5微米的镀覆光致抗蚀剂312的厚度提供良好的金属镀覆均匀性。对镀覆光致抗蚀剂312进行图案化以设置用于在水平方向上镀覆的边界,这在下一步骤中执行。30.图3d示出了具有通过镀覆形成的金属线314的半导体器件300。镀覆光致抗蚀剂312在水平方向上为金属线314提供边界。在该示例中,金属线314镀覆在籽晶金属310上。在一些示例中,金属线314是包括钛、铜、镍或金的金属层。金属的组合可用于金属线314。如上所述,籽晶金属310、金属线314和其他金属的厚度可介于5.5微米至6.5微米之间。金属的这种组合厚度可为镀覆过程提供良好的附着和导电性。31.图3e示出了在处理完成后的半导体器件300。图3e包括铟层316、金属层318、金属层320、氧化物322、硅晶片324、玻璃晶片326和屏障结构328。在其他示例中,铟层316可以是另一种金属。在图3e中,镀覆光致抗蚀剂312已经被剥离并且不存在于图3e中。然后暴露和剥离位于镀覆光致抗蚀剂312下面的籽晶金属310。光致抗蚀剂306被灰化以移除光致抗蚀剂306并揭露mems器件302。移除光致抗蚀剂306揭露了屏障结构328的底边缘307。该底边缘307有助于最终屏障结构328的形状。屏障结构328的一端延伸到氧化层303,而另一端在氧化层303上方。在一个示例中,由于灰化过程期间的未完全移除,一些少量的光致抗蚀剂306可能残留在屏障结构328附近。在其他示例中,光致抗蚀剂306可被完全移除。在一些示例中,45度或更小的缓斜率可用于屏障结构328的底部边缘307。移除光致抗蚀剂306还可在籽晶金属310(和/或金属线314)和氧化物层303之间产生空气间隙。空气间隙可改善屏障结构328的顺应性。在一些示例中,当光致抗蚀剂306接近氧化物层303时,移除光致抗蚀剂306可致使光致抗蚀剂306向零厚度渐缩。在一个示例中,光致抗蚀剂306和氧化物层303的相交是平滑的。在该区域中,籽晶金属310和金属线314的厚度可以是均匀的。在该区域中,籽晶金属310和/或金属线314可遵循光致抗蚀剂306的轮廓。在一些示例中,在屏障结构328的区域中,光致抗蚀剂306的厚度的变化小于0.5微米。如图3e所示,在本示例中,屏障结构328由籽晶金属310和金属线314形成。屏障结构328通过在mems器件302周围创建密封腔室或微型环境102来减小防止mems器件302的污染。32.在该示例中,通过沉积附加金属层来完成cmos晶片304和氧化物322之间的金属键合。沉积铟层316、金属层318和金属层320以完成金属层。金属层318和金属层320可以是任何合适的金属诸如钛、铜、镍或金。在一些示例中,金属的组合可用于金属层318和320。在一个示例中,层314、316、318、320和322可使用镀覆来键合到其相邻层。在一些示例中,这些层的宽度可能不同。金属层320键合到氧化物322。硅晶片324耦接到氧化物322,并且玻璃晶片326耦接到硅晶片324。33.籽晶金属310、金属线314、铟层316、金属层318和金属层320提供cmos晶片304(例如,第一衬底)与为mems器件302创建窗口的晶片(例如,硅晶片324和玻璃晶片326,其可以是第二衬底的一部分,以及氧化物322)之间的金属键合。该金属键合有助于密封半导体器件300并在mems器件302周围创建微型环境102。如上所述,除mems器件302之外,其他类型的器件可被密封在微型环境102中。34.在一些示例中,密封半导体器件300的盖(例如,氧化物322、硅晶片324和玻璃晶片326)可以是第二衬底。第二衬底可包括第二单独半导体衬底、或两个或更多个衬底的键合堆叠。第二衬底(或键合堆叠)可通过与用于创建第一半导体衬底(在此示例中为cmos晶片304)的过程分离和独立的过程来单独地或共同地创建。35.在一个实施例中,密封腔室的盖或第二衬底可通过瞬时液相键合来密封。瞬时液相键合也称为固液互扩散键合。在这种技术中,夹层熔化,并且夹层元素扩散到衬底材料中,由此导致等温凝固。该过程导致具有比键合温度更高的熔点的键合。这种类型的键合实现低过程温度,同时在连接晶片后提供更高的重熔温度。36.在另一个示例中,密封腔室的盖或第二衬底可通过粘合剂键合来密封。粘合剂键合涉及使用粘合剂并且通常涉及相对较低的键合温度。37.密封腔室的盖可通过任何合适的技术连接到第一衬底(诸如cmos晶片304),包括例如金属键合、直接键合、阳极键合、反应键合和粘合剂键合。金属键合的进一步示例包括但不限于固液互扩散键合、共熔键合和热压键合。38.可通过晶片处理技术在沉积之前或之后对键合材料进行图案化以便形成包含本文所述屏障结构的一个或多个单独腔室。这种方法也称为晶片级封装。在晶片级封装中,在晶片被分成单独的微电子器件或芯片之前,至少部分地通过并行处理以晶片形式的多个管芯来形成单独器件封装。本文的一些示例可通过晶片级封装来形成,因为屏障结构和键合结构的形成是用晶片形成过程来执行的。39.在第一衬底和盖或第二衬底上形成最终结构的材料可通过许多薄膜晶片形成过程中的任何一种来沉积,包括蒸发、溅射、镀覆、离子束沉积、化学气相沉积、光致抗蚀剂沉积、光刻、蚀刻、清洗等。40.另外,在一些示例中,第二衬底可以是非平面的。非平面特征可有助于通过靠近垂直的方法(诸如小于1微米)在腔室封装内形成屏障结构以经由上述毛细管作用产生密封腔室。在另一个示例中,第二衬底可与第一半导体衬底(cmos晶片304)上的屏障结构328垂直接触。41.在本文的示例中,屏障结构328可使用用于在没有附加掩模级的情况下在晶片之间产生金属键合的技术来制造。本文的制造技术产生具有高度均匀性的薄膜和屏障结构,这使得技术可重复。本文描述的结构可被设计成具有可变的顺应性程度。本文所述的一些结构可通过声学显微镜来无损地检查。屏障结构也通过与半导体器件的有效区域相同的材料来制造,这保证了材料的相容性。42.图4是根据本文的各种示例的具有屏障结构的器件和不具有屏障结构的器件的缺陷计数的曲线图400。缺陷是半导体器件(诸如半导体器件112)的由存在于半导体器件上的污染物128引起的故障。图400的x轴表示缺陷的数量,而y轴表示每个器件的以周为单位的测试时间。图400的左半部分示出了零周、一周和两周后的五个不具有屏障结构的器件的缺陷计数。图400的右半部分示出了零周、一周和两周后的五个具有屏障结构的器件的缺陷计数。43.如图4所示,缺陷计数402表示在零周时或在器件被制造时的没有屏障结构的器件中的缺陷。在零周时,无屏障结构的器件具有零个缺陷。缺陷计数404表示在一周时的不具有屏障结构的器件中的缺陷。在一周时,器件具有约10到约50个缺陷之间的各种缺陷计数。44.缺陷计数406表示在两周时的不具有屏障结构的器件中的缺陷。在两周时,不具有屏障结构的器件具有约20到约120之间的缺陷计数。因此,没有屏障结构的器件有时即使在一两周时也可表现出大量缺陷。45.缺陷计数408、410和412分别表示在零周、一周和两周时的具有屏障结构的器件中的缺陷。缺陷计数408、410和412都为零。因此,与不具有屏障结构的器件相比,本文所述的屏障结构显著减小缺陷。46.图5是根据本文的各种示例的用于产生屏障结构的方法500的流程图。方法500的步骤可以任何合适的顺序执行,并且可在一些示例中包括附加步骤。47.方法500开始于510,其中在第一衬底的至少一部分上施加介电材料。可在半导体器件之上施加介电材料。在一个示例中,介电材料可以是光致抗蚀剂。48.可在半导体器件上图案化介电材料以涂覆mems器件或其他部件,并且为将要制造的屏障结构创建基础。介电材料还具有沿用于形成屏障结构的边缘的斜率。如上所述,在一些示例中,斜率可以是45度或更小的缓斜率。上面相对于图3a描述了介电材料的应用。49.再次参考图5,方法500在520继续,其中在第一衬底的至少一部分上沉积籽晶金属,并且籽晶金属可沉积在第一衬底的包含介电材料的部分上。籽晶金属有助于将籽晶金属上方的层镀覆到籽晶金属下方的层。籽晶金属的材料和厚度可基于应用而变化。在一些示例中,钛、铜、镍或金可用作籽晶金属。在其他实施例中,金属的组合可用于籽晶金属,诸如钛-铜籽晶金属。上面相对于图3b描述了籽晶金属的沉积。50.方法500在530继续,其中在籽晶金属上沉积镀覆光致抗蚀剂。在一个示例中,镀覆光致抗蚀剂沉积在籽晶金属的至少一部分和介电材料的至少一部分上。对镀覆光致抗蚀剂进行图案化以为后面执行的镀覆步骤设置一个或多个边界。在一个示例中,镀覆光致抗蚀剂部分地覆盖在步骤510中施加的介电材料和在步骤520中施加的籽晶金属。以这种方式部分地覆盖介电材料和籽晶金属会允许介电材料和籽晶金属形成为屏障结构的一部分。在一个实施例中,镀覆光致抗蚀剂的厚度介于4微米至5微米之间,其在其他实施例中可增加或减少。上面相对于图3c描述了镀覆光致抗蚀剂的沉积。51.方法500在540继续,其中在籽晶金属上镀覆金属线,其中镀覆光致抗蚀剂形成金属线的边界,并且其中金属线形成屏障结构的至少一部分。在上面关于图3d描述的示例中,镀覆光致抗蚀剂312在金属线314的每一侧提供边界。金属线在半导体器件和外部环境之间,或者在其他示例中在第一衬底的其他区之间提供屏障结构的至少一部分。52.再次参考图5,方法500在550继续,其中剥离镀覆光致抗蚀剂的至少一部分。此外,在550处,蚀刻籽晶金属的至少一部分。如果镀覆光致抗蚀剂被剥离,则被蚀刻的籽晶金属可以是暴露的籽晶金属。因为镀覆光致抗蚀剂为金属线提供了至少一个边界,所以剥离镀覆光致抗蚀剂暴露金属线的一个或多个边缘。53.方法500在560处继续,其中相对于屏障结构定位第二衬底以形成腔室。腔室可以是密封腔室,在一些示例中,半导体器件可位于密封腔室内。在一些示例中,第二衬底可以是盖、晶片、窗口或另一衬底。第二衬底可包括第二单独半导体衬底、或两个或更多个衬底的键合堆叠。在一个实施例中,密封腔室的盖或第二衬底可通过瞬时液相键合来密封。在另一个示例中,密封腔室的盖或第二衬底可通过粘合剂键合来密封。54.在附加步骤中,在蚀刻籽晶金属的至少一部分之后,可移除介电材料的至少一部分以揭露半导体器件并创建屏障结构。在一个示例中,介电材料可被灰化以移除介电材料。介电材料的移除在屏障结构的底部处提供底切。屏障结构的底部具有由被移除的介电材料的数量和形状确定的形状。底切提供了如上所述的屏障结构的斜率。在一些示例中,缓斜率用于屏障结构的底部。如图3e所示和上文所述,屏障结构由光致抗蚀剂、籽晶金属和金属线的组合形成。屏障结构减小或防止腔室或微型环境的污染,如在本文的示例中所述。55.在附加步骤中,通过沉积附加金属层来完成金属键合。例如,沉积铟层316、金属层318和金属层320以完成图3e中的金属层。这些金属层可在方法500的步骤560之后使用任何合适的技术来沉积。这些金属层可包括任何合适的金属诸如钛、铜、镍或金。在一些示例中,金属的组合可用于这些金属层。在沉积金属层之后,可将金属层键合到氧化物诸如氧化物322。然后,可添加硅晶片(诸如硅晶片324)和玻璃晶片(诸如玻璃晶片326)以完成半导体器件。56.在本说明书中,术语“耦接”可覆盖实现与本说明书一致的功能关系的联接、通信或信号路径。例如,如果器件a提供信号以控制器件b来执行动作,则:(a)在第一示例中,器件a直接耦接到器件b;或者(b)在第二示例中,如果中间部件c没有实质上改变器件a和器件b之间的函数关系,因此器件b由器件a经由器件a所提供的控制信号控制,则器件a通过中间部件c间接耦接到器件b。57.虽然某些部件可在本文中描述为属于特定过程技术,但这些部件可被交换为其他过程技术的部件。58.除非另有说明,在值前的“约”、“大约”或“基本上”是指所述值的+/-10%。在权利要求的范围内,修改在所描述的示例中是可能的,并且其他示例是可能的。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123412.html

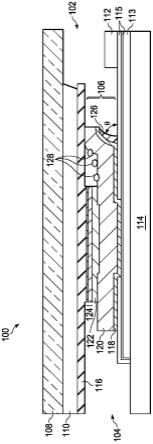

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。