利用芯片下方基板中的腔体控制翘曲的集成电路封装的制作方法

- 国知局

- 2024-07-27 12:53:07

本文的实施例涉及集成电路封装,特别是控制安装有集成电路裸片的集成电路封装的层压基板的翘曲。

背景技术:

1、图1示出集成电路封装10的一部分的横截面。封装10包括层压基板12。层压基板12由多个层的层压形成,这些层包括:绝缘(例如,fr4-阻燃剂4)芯层14;在芯层14的每个相对表面上的导电(铜)层18a、18b;在每个铜层18a、18b上的预浸料层16a、16b;在每个预浸料层16a、16b上的导电(铜)层18c、18d;以及在每个铜层18c、18d上的阻焊层20a、20b。层压基板12还可以包括电镀过孔(未明确示出),其将铜层18a、18c的一部分电连接到铜层18b、18d的一部分。层压基板12可以采用印刷电路板pcb的形式。

2、集成电路裸片30安装至层压基板12的上表面。集成电路裸片30包括背面32和正面34。在正面34上提供多个集成电路电连接垫36。使用粘合材料38(例如裸片附接胶水或胶带),在层压基板12上表面处,将集成电路裸片30的背面32附接至阻焊层20a。

3、在阻焊层20a中选择性地制成开口40,以露出提供层压基板12的连接垫42的铜层18c的相应部分。键合线43在电连接垫36到相应的连接垫42之间电连接。

4、在阻焊层20b中选择性地制成开口44,以露出提供层压基板12的连接垫46的铜层18d的相应部分。将焊球48安装至连接垫46。

5、罩体(或盖子)50附接至层压基板12以包封集成电路裸片30。可选地,包封体可以在层压基板12上被二次注模以包封集成电路芯片30。

6、集成电路裸片30的硅材料与层压基板12之间的热膨胀系数cte存在已知的不匹配。例如,硅的cte约为2.8ppm/℃,塑料基板的cte约为15ppm/℃。cte中的这种不匹配可能导致设备翘曲的风险,这会产生许多问题,诸如难以附接罩体50;损坏集成电路裸片30的硅材料或粘合材料38;以及修改集成电路裸片30的电子电路的操作(例如,操作参数漂移)。

7、本领域需要解决设备翘曲的问题。

技术实现思路

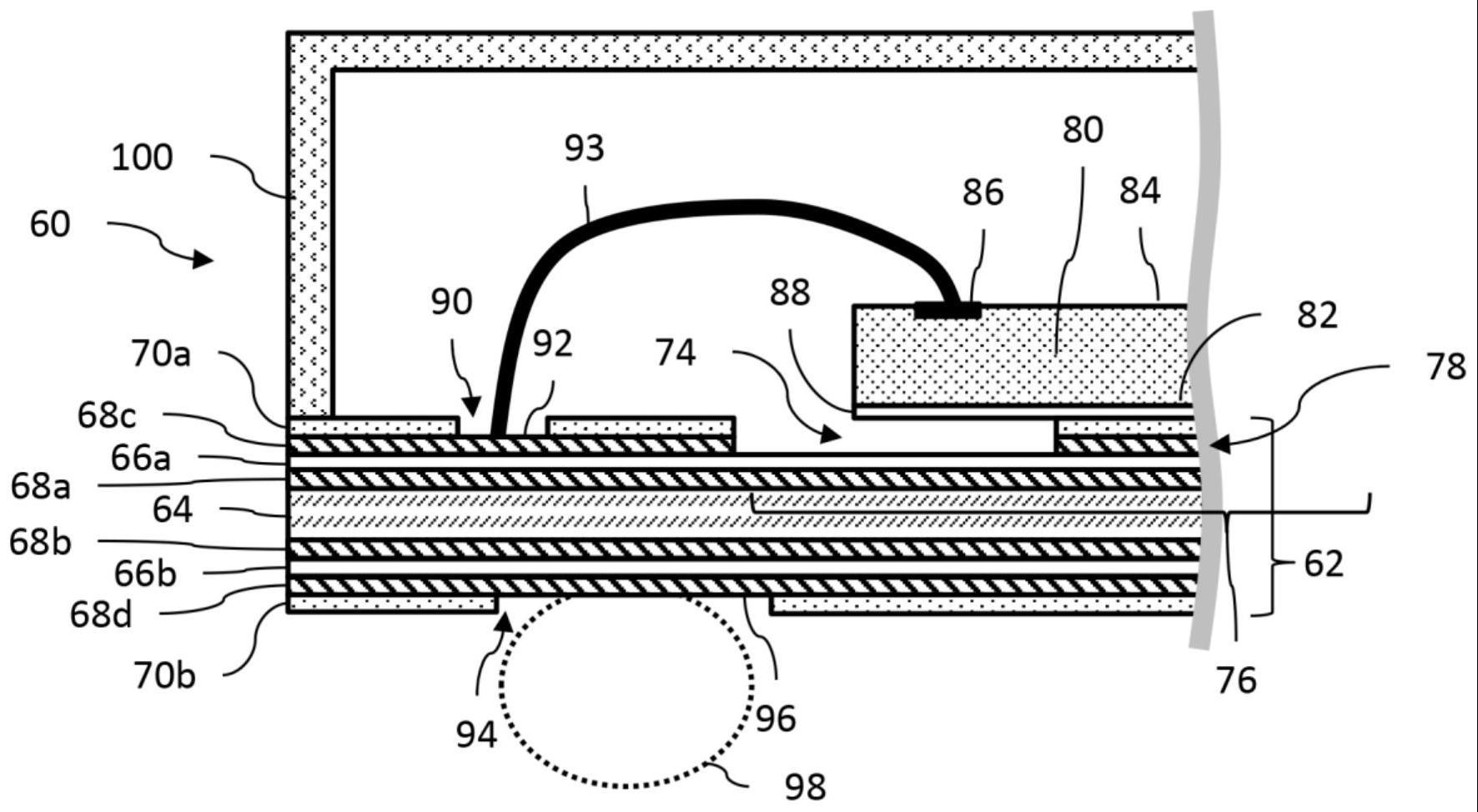

1、在一个实施例中,集成电路封装包括:由绝缘芯层、绝缘芯层之上的导电层和导电层之上的阻焊层形成的支撑基板,其中支撑基板包括裸片附接位置和第一连接垫;集成电路芯片,具有带第二连接垫的正面和背面,其中背面在裸片附接位置处安装至支撑基板的上表面;其中支撑基板的上表面包括位于裸片附接位置内的腔体,所述腔体延伸到集成电路芯片的背面之下,所述腔体包括一个其中不存在阻焊层和导电层的至少一部分的区域;以及第一和第二连接垫之间的键合线。

2、在一个实施例中,用于集成电路封装的支撑基板包括:绝缘芯层;在绝缘芯层之上的导电层;在导电层之上的阻焊层;以及在用于所述支撑基板的裸片附接位置处,在支撑基板上的表面中的腔体,该腔体包括其中不存在阻焊层和导电层的至少一部分的区域。

技术特征:1.一种集成电路封装,包括:

2.根据权利要求1所述的集成电路封装,其中在所述集成电路芯片的外围部分的下方存在所述腔体,所述第二连接垫位于所述外围部分。

3.根据权利要求1所述的集成电路封装,其中在所述集成电路芯片的外围部分的下方不存在所述腔体,所述第二连接垫位于所述外围部分。

4.根据权利要求1所述的集成电路封装,其中所述导电层的不存在的所述部分是所述腔体内所述导电层厚度的一部分。

5.根据权利要求1所述的集成电路封装,其中所述导电层的不存在的所述部分是所述腔体内所述导电层的整个厚度。

6.根据权利要求1所述的集成电路封装,其中所述绝缘芯层由fr4材料制成。

7.根据权利要求1所述的集成电路封装,其中所述导电层由铜制成。

8.根据权利要求1所述的集成电路封装,还包括粘合层,所述粘合层用于将所述集成电路芯片的所述背面附接至所述支撑基板的所述上表面。

9.根据权利要求1所述的集成电路封装,其中所述腔体延伸到所述裸片附接位置之外。

10.根据权利要求1所述的集成电路封装,其中所述腔体延伸到所述集成电路芯片的外边缘之外。

11.根据权利要求1所述的集成电路封装,还包括安装至支撑基板的罩体,并且所述罩体被配置为包封所述集成电路芯片。

12.根据权利要求1所述的集成电路封装,其中在所述裸片附接位置内存在的所述阻焊层的剩余部分和所述导电层的剩余部分形成基座,其中所述集成电路芯片的所述背面安装至所述基座。

13.根据权利要求12所述的集成电路封装,其中所述腔体完全包围所述基座。

14.根据权利要求12所述的集成电路封装,其中所述腔体部分地包围所述基座。

15.一种用于集成电路封装的支撑基板,包括:

16.根据权利要求15所述的支撑基板,其中竖直地在安装至所述裸片附接位置的集成电路芯片的正面上的连接垫将被定位的位置之下,在所述裸片附接位置处在所述支撑基板的所述上表面中不存在所述腔体。

17.根据权利要求15所述的支撑基板,其中所述导电层的不存在的所述部分是所述腔体内所述导电层厚度的一部分。

18.根据权利要求15所述的支撑基板,其中所述导电层的不存在的所述部分是所述腔体内所述导电层的整个厚度。

19.根据权利要求15所述的支撑基板,其中所述绝缘芯层由fr4材料制成。

20.根据权利要求15所述的支撑基板,其中所述导电层由铜制成。

21.根据权利要求15所述的支撑基板,其中所述腔体延伸到所述裸片附接位置之外。

22.根据权利要求15所述的支撑基板,其中在所述裸片附接位置内存在的所述阻焊层的剩余部分和所述导电层的剩余部分形成基座,其中所述集成电路芯片的所述背面安装至基座。

23.根据权利要求22所述的支撑基板,其中所述腔体完全包围所述基座。

24.根据权利要求22所述的支撑基板,其中所述腔体部分地包围所述基座。

技术总结本发明涉及利用集成电路芯片下方层压基板中形成的腔体控制翘曲的集成电路封装。支撑基板包括绝缘芯层、绝缘芯层之上的导电层和导电层之上的阻焊层。集成电路芯片的背面在裸片附接位置处安装在支撑基板的上表面。支撑基板的上表面包括位于裸片附接位置内的腔体,其中腔体延伸到集成电路芯片的背面之下。腔体由其中已将阻焊层和导电层的至少一部分移除的区域限定。键合线将集成电路芯片正面上的连接垫连接到支撑基板上表面的连接垫。技术研发人员:R·杜卡受保护的技术使用者:意法半导体(马耳他)有限公司技术研发日:技术公布日:2024/1/12本文地址:https://www.jishuxx.com/zhuanli/20240726/123940.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。