一种MEMS器件封装结构及其制备方法与流程

- 国知局

- 2024-07-27 13:01:26

本发明属于微机电系统,特别是涉及一种mems器件封装结构及其制备方法。

背景技术:

1、mems谐振器是一种mems(micro electro mechanical system,微机电系统)器件,由mems芯片和asic(application specific integrated circuit,专用集成电路)芯片组成。

2、mems芯片是指微型机械系统芯片,由微小尺寸的机械结构和电子元件集成在一起。在mems谐振器中,mems芯片通常包括一个微弹性结构,如悬臂梁或薄膜,以及与之相连的电极。当施加电压或电场时,微弹性结构会产生机械振动,形成谐振。

3、asic芯片是指专门设计和制造的应用特定集成电路芯片。在mems谐振器中,asic芯片用于控制和驱动mems芯片的振动。asic芯片通常包含一个振荡电路,用于提供谐振频率的稳定和精确控制。通过将mems芯片和asic芯片组合在一起,mems谐振器可以实现高度集成化和稳定的振荡功能,在许多应用领域中被广泛使用,如无线通信、传感器、时钟等。

4、对于mems谐振器来说,小型化是指将设备或器件的尺寸缩小至更小的尺寸。在mems谐振器中,小型化是一项重要的发展趋势。通过使用微纳加工技术和先进的材料,可以将mems谐振器的尺寸缩小到微米或纳米级别。小型化可以带来多重好处,包括更高的集成度、更低的功耗、更快的响应速度和更广泛的应用领域。小型化的mems谐振器在无线通信中可以用于频率选择、滤波和时钟源等功能。在传感器领域,小型化的mems谐振器可以用于惯性传感器、压力传感器、加速度计等应用。此外,小型化的mems谐振器还可以用于医疗设备、消费电子产品和汽车电子等领域。

5、现有技术中,主要通过导线键合的方式实现asic芯片和mems芯片之间的电互连,通常需要留有用于导线键合的空间,且需要对asic芯片和mems芯片的电连接进行分别引出,因此封装结构通常大于asic芯片的面积,难以实现封装尺寸的小型化;同时导线键合的互连方式导致连接线过长,产生的寄生器件影响较大,限制了mems谐振器在高频器件中的使用;另外由于通过引线键合的方式进行电互连,导致mems结构的真空度无法得到保证,容易影响器件的性能可靠性。

6、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的,不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上现有技术的缺点,本发明的目的在于提供一种mems器件封装结构及其制备方法,用于解决现有技术中mems器件封装结构的寄生参数大、封装面积大的问题。

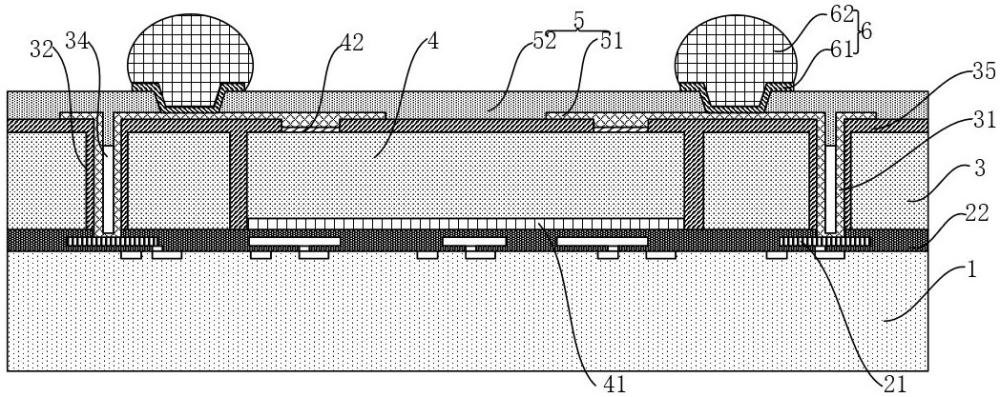

2、为实现上述目的,本发明提供一种mems器件封装结构,所述mems器件封装结构包括:asic芯片、导电连接层、硅基框架、mems芯片、重布线层和导电引出层;

3、所述asic芯片包括相对设置的正面和背面,所述asic芯片包括asic导电连接部和第一钝化层,所述asic导电连接部设置于所述asic芯片的正面,所述第一钝化层包裹所述asic导电连接部未进行电连接的部分;所述硅基框架包括相对设置的正面和背面,所述硅基框架的背面设置于所述第一钝化层上;

4、所述mems芯片包括相对设置的正面和背面,所述mems芯片包括mems导电连接部,所述mems导电连接部设置于所述mems芯片的正面,所述硅基框架内设置有垂直孔结构和凹槽,所述mems芯片的背面放置于所述硅基框架的凹槽内;所述导电连接层设置于所述垂直孔结构内,所述垂直孔结构使下方的所述asic导电连接部显露,所述导电连接层与显露出的所述asic导电连接部相连以使所述asic芯片的电连接通过所述asic导电连接部和所述导电连接层引出至所述硅基框架表面;

5、所述重布线层包括线路层和介质层,所述重布线层覆盖于所述mems芯片的正面和所述硅基框架的正面,所述重布线层的线路层与所述导电连接层、所述mems导电连接部均形成有效电连接以使所述asic芯片和所述mems芯片的电连接引出至所述重布线层表面;

6、所述导电引出层设置于所述重布线层上,所述导电引出层与所述重布线层的线路层形成有效电连接以使所述mems芯片和所述asic芯片的电信号引出至所述mems器件封装结构的表面。

7、可选地,所述mems器件封装结构还包括第二钝化层,所述第二钝化层填充于所述mems芯片与所述硅基框架之间、所述垂直孔结构的侧面与所述导电连接层之间、所述导电连接层和所述硅基框架表面之间的空隙及所述硅基框架、所述mems芯片显露出的表面。

8、可选地,所述导电连接层填充整个所述垂直孔结构;或所述导电连接层仅覆盖所述垂直孔结构的内壁表面,形成以所述导电连接层为壁面的通孔结构,所述通孔结构与所述重布线层接触的表面被所述重布线层的介质层密封。

9、可选地,所述导电连接层仅覆盖所述垂直孔结构的内壁表面时,仅在所述通孔结构与所述重布线层接触的表面设置所述重布线层的介质层,所述通孔结构的内部为真空状态;或所述通孔结构被所述重布线层的介质层填满。

10、可选地,所述硅基框架内的所述凹槽为贯通所述硅基框架的通槽或未贯通所述硅基框架的盲槽。

11、可选地,所述mems芯片的背面设置有绝缘胶层,所述mems芯片通过所述绝缘胶层固定在所述硅基框架的所述凹槽内。

12、可选地,所述导电引出层包括基底金属层和焊球,所述焊球通过所述基底金属层与所述重布线层的线路层形成有效电连接以使所述mems芯片和所述asic芯片的电信号引出至所述mems器件封装结构的表面。

13、本发明还提供一种mems器件封装结构的制备方法,所述制备方法用于制备上述任意一种mems器件封装结构,所述制备方法包括:

14、设置一硅基框架,所述硅基框架包括相对设置的正面和背面,所述硅基框架包括垂直孔结构和凹槽,所述垂直孔结构贯穿所述硅基框架;

15、于所述硅基框架的背面设置asic芯片,所述asic芯片包括相对设置的正面和背面,所述asic芯片的正面设置有asic导电连接部和包裹所述asic导电连接部的第一钝化层;所述asic芯片的正面的所述第一钝化层与所述硅基框架的背面连接;

16、于所述硅基框架的凹槽内设置mems芯片,所述mems芯片包括相对设置的正面和背面,所述mems芯片的背面设置于所述凹槽内,所述mems芯片的正面设置mems导电连接部;

17、去除所述垂直孔结构下方的所述第一钝化层以显露出所述asic导电连接部;

18、于所述垂直孔结构内设置导电连接层,使所述导电连接层与所述asic导电连接部之间形成有效电连接,所述导电连接层将所述asic芯片的电连接通过所述asic导电连接部引出至所述硅基框架的表面;

19、于所述mems芯片的正面设置重布线层,所述重布线层覆盖所述mems芯片的正面和所述硅基框架的正面,所述重布线层包括线路层和介质层,于所述重布线层的表面设置开口,所述开口显露出所述线路层,所述重布线层的线路层与所述mems导电连接部、所述导电连接层均形成有效电连接使所述mems芯片和所述asic芯片的电连接通过线路层引出至所述重布线层表面的所述开口;

20、于所述开口内设置基底金属层,于所述基底金属层上设置焊球,所述基底金属层与所述焊球组成导电引出层,所述导电引出层将所述mems芯片和所述asic芯片的电连接引出至所述mems器件封装结构的表面。

21、可选地,所述硅基框架的制备方法包括:提供一硅片,所述硅片包括相对设置的第一表面和第二表面;于所述硅片的第一表面设置垂直孔结构和凹槽;对所述硅片的第二表面进行减薄至所述垂直孔结构贯穿所述硅片,至此得到硅基框架,所述硅片的第一表面为所述硅基框架的正面,所述硅片的第二表面为所述硅基框架的背面。

22、可选地,于所述垂直孔结构内设置导电连接层前,于所述硅基框架和所述mems芯片显露出的表面设置第二钝化层,所述第二钝化层覆盖所述垂直孔结构的侧壁并填充于所述mems芯片和所述硅基框架之间的空隙,去除所述mems导电连接部上方的所述第二钝化层和所述垂直孔结构底部的所述第二钝化层以显露出所述mems导电连接部和所述asic导电连接部。

23、如上,本发明的mems器件封装结构及其制备方法,具有以下有益效果:

24、本发明通过在硅基框架内放置mems芯片,以设置重布线层实现mems芯片和asic芯片的电互连和电信号引出,缩短互连线长度,减小寄生参数,利于高频领域应用;

25、本发明通过钝化层对mems芯片的二次密封提高器件真空的稳定性,避免受到外界环境影响mems芯片的内部结构,从而提高了mems器件封装结构得到性能稳定性和使用寿命;

26、本发明通过在asic芯片上设置硅基框架并在硅基框架内设置mems芯片的堆叠结构,使整体封装面积不大于asic芯片面积,使封装小型化。

本文地址:https://www.jishuxx.com/zhuanli/20240726/124567.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表