一种电子器件的制备方法及电子器件与流程

- 国知局

- 2024-07-27 13:05:44

本申请涉及微电子,尤其涉及一种电子器件的制备方法及电子器件。

背景技术:

1、目前,在微机电芯片以及集成电路传感器制造中,加工精度是影响器件性能的主要因素,通常薄膜沉积可以通过溅射的方法在晶圆表面生长特定厚度所需膜层,不同的膜层厚度直接影响到器件的阻值以及灵敏度,然而,现有电子器件的制备方式,刻蚀工艺流程中的过刻现象严重,部分膜层的过刻容易导致器件的电阻增大,影响电子器件的电学性能。

技术实现思路

1、本申请实施例提供一种压电材料的制备方法及电子器件,通过干法刻蚀和湿法刻蚀结合的方式,改善刻蚀过刻的问题,提高电子器件的电学性能。

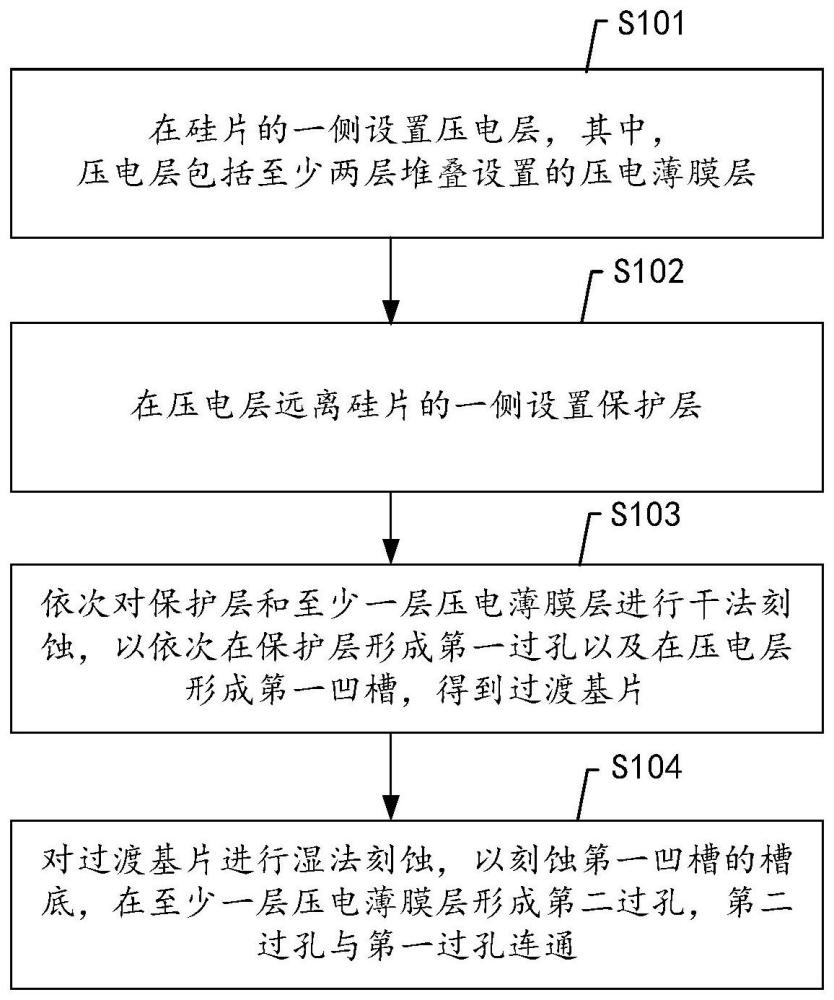

2、本申请实施例的第一方面,提供一种电子器件的制备方法,包括:

3、在硅片的一侧设置压电层,其中,所述压电层包括至少两层堆叠设置的压电薄膜层;

4、在所述压电层远离所述硅片的一侧设置保护层;

5、依次对所述保护层和至少一层所述压电薄膜层进行干法刻蚀,以依次在所述保护层形成第一过孔以及在所述压电层形成第一凹槽,得到过渡基片;

6、对所述过渡基片进行湿法刻蚀,以刻蚀所述第一凹槽的槽底,在至少一层所述压电薄膜层形成第二过孔,所述第二过孔与所述第一过孔连通。

7、在一些实施方式中,所述压电层包括第一压电薄膜层和第二压电薄膜层,所述第二压电薄膜层设置于所述硅片与所述第一压电薄膜层之间;

8、所述依次对所述保护层和至少一层所述压电薄膜层进行干法刻蚀,包括:

9、对所述保护层进行干法刻蚀,以在所述保护层形成所述第一过孔;

10、通过所述第一过孔对所述第一过孔所在区域的所述第一压电薄膜层进行干法刻蚀,以在所述第一压电薄膜层形成所述第一凹槽。

11、在一些实施方式中,所述第一凹槽的槽深与所述第一压电薄膜层的厚度的比值范围为42%-57%;和/或,

12、所述第一凹槽的槽壁坡度角的锐角小于或等于70°,所述槽壁坡度角为所述第一凹槽的侧壁与所述硅片所在平面的夹角。

13、在一些实施方式中,所述第一压电薄膜层包括氮化铝;

14、所述第二压电薄膜层包括钼。

15、在一些实施方式中,对所述过渡基片进行湿法刻蚀,包括:

16、对所述第一凹槽的槽底进行湿法刻蚀,以在所述第一压电薄膜层形成第二过孔;

17、通过所述第二过孔对所述第二过孔所在区域的第二压电薄膜层进行湿法刻蚀,以在所述第二压电薄膜层形成第二凹槽。

18、在一些实施方式中,所述第一凹槽在所述硅片上的正投影落在所述第二凹槽的槽底在所述硅片上的正投影内;和/或,

19、所述第二凹槽的槽深占所述第二压电薄膜层厚度的百分比大于0%且小于或等于17%;和/或,

20、所述第二凹槽的槽壁坡度角的锐角小于或等于20°。

21、本申请的第二方面,提供一种电子器件,应用如第一方面所述的电子器件制备方法制备得到的,所述电子器件包括:硅片、压电层、保护层;

22、所述压电层设置于所述硅片与所述保护层之间,所述压电层包括至少两层堆叠设置的压电薄膜层;

23、所述保护层设置有第一过孔;

24、至少一层所述压电薄膜层设置有第二过孔,所述第二过孔与所述第一过孔连通。

25、在一些实施方式中,所述压电层包括第一压电薄膜层和第二压电薄膜层;

26、所述第一压电层位于所述硅片与所述第二压电薄膜层之间;

27、所述第二压电层位于所述第一压电薄膜层和所述保护层之间。

28、在一些实施方式中,所述第一压电薄膜层设置有所述第二过孔;

29、所述第二过孔的槽壁坡度角的锐角小于或等于70°。

30、在一些实施方式中,所述第二压电薄膜层设置有第二凹槽,所述第二凹槽的槽深占所述第二压电薄膜层厚度的百分比大于0%且小于或等于17%;和/或,

31、所述第二凹槽的槽壁坡度角的锐角小于或等于20°;和/或,

32、所述第一过孔在所述硅片上的正投影落在所述第二凹槽的槽底在所述硅片上的正投影内,所述第二过孔在所述硅片上的正投影落在所述第二凹槽的槽底在所述硅片上的正投影内。

33、本申请提供一种电子器件的制备方法及电子器件,通过在硅片的一侧设置压电层,在远离压电层的一侧设置保护层。依次对保护层和第一压电层薄膜进行干法刻蚀,在保护层形成第一过孔和在第一压电薄膜层形成第一凹槽,对第一凹槽的槽底进行湿法刻蚀,在第一压电薄膜层形成第二过孔,在第二压电薄膜层形成第二凹槽。通过干法刻蚀和湿法刻蚀相结合,在改善所在第一压电薄膜层的第一凹槽的刻蚀角度的同时,降低第二压电薄膜层的刻蚀深度,从而避免刻蚀过刻的现象,提高电子器件的电学性能。

技术特征:1.一种电子器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的电子器件的制备方法,其特征在于,

3.根据权利要求2所述的电子器件的制备方法,其特征在于,

4.根据权利要求2所述的电子器件的制备方法,其特征在于,

5.根据权利要求1或2所述的电子器件的制备方法,其特征在于,

6.根据权利要求5所述的电子器件的制备方法,其特征在于,

7.一种电子器件,其特征在于,应用如权利要求1至7中任一项所述的电子器件制备方法制备得到的,所述电子器件包括:硅片、压电层、保护层;

8.根据权利要求7所述的电子器件,其特征在于,

9.根据权利要求7所述的电子器件,其特征在于,

10.根据权利要求8所述的电子器件,其特征在于,

技术总结本申请公开一种电子器件的制备方法及电子器件,涉及微电子技术领域,能够提高电子器件的电学性能。电子器件的制备方法包括:在硅片的一侧设置压电层,其中,压电层包括至少两层堆叠设置的压电薄膜层;在压电层远离硅片的一侧设置保护层;依次对保护层和至少一层压电薄膜层进行干法刻蚀,以依次在保护层形成第一过孔以及在压电层形成第一凹槽,得到过渡基片;对过渡基片进行湿法刻蚀,以刻蚀第一凹槽的槽底,在至少一层压电薄膜层形成第二过孔,第二过孔与第一过孔连通。技术研发人员:郭大飞,卜德冲,王鹏受保护的技术使用者:赛莱克斯微系统科技(北京)有限公司技术研发日:技术公布日:2024/6/2本文地址:https://www.jishuxx.com/zhuanli/20240726/124875.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。