时间间隔测量电路及其第二级TDC电路、电子设备

- 国知局

- 2024-07-30 10:21:43

本发明涉及时间测量领域,尤其涉及一种时间间隔测量电路及其第二级tdc电路、电子设备。

背景技术:

1、时间数字转换器(time-to-digital converter,tdc),可理解为能够对输入的开始信号、接收信号的时间间隔进行检测的任意电路,该开始信号、接收信号可基于触发脉冲的上升沿、下降沿而产生。

2、现有相关技术中,时间间隔测量电路可以包含两级tdc电路,其中的第二级tdc电路通常采用电荷泵+adc结构的形式。其中的电荷泵是一种常见的时间—电压转换电路,理论上其转换速率可以通过增加输出电流来达到任意值。但事实上,这一转换速率受限于电路工艺和要转换的时间长度。当时间长度很小(例如小于10ps)时,电荷泵的激励脉冲将过短,以至于无法驱动晶体管进行线性的电流输出,此时电荷泵将失效。增加输入时间的长度可以让电荷泵正常工作,但这是以增加adc位数和误差为代价的。这也就意味着这一结构的tdc存在一个由电荷泵限制的分辨率上限,目前这一上限约为0.8ps。

技术实现思路

1、本发明提供一种时间间隔测量电路及其第二级tdc电路、电子设备,以解决第二级tdc电路采用电荷泵而带来的问题。

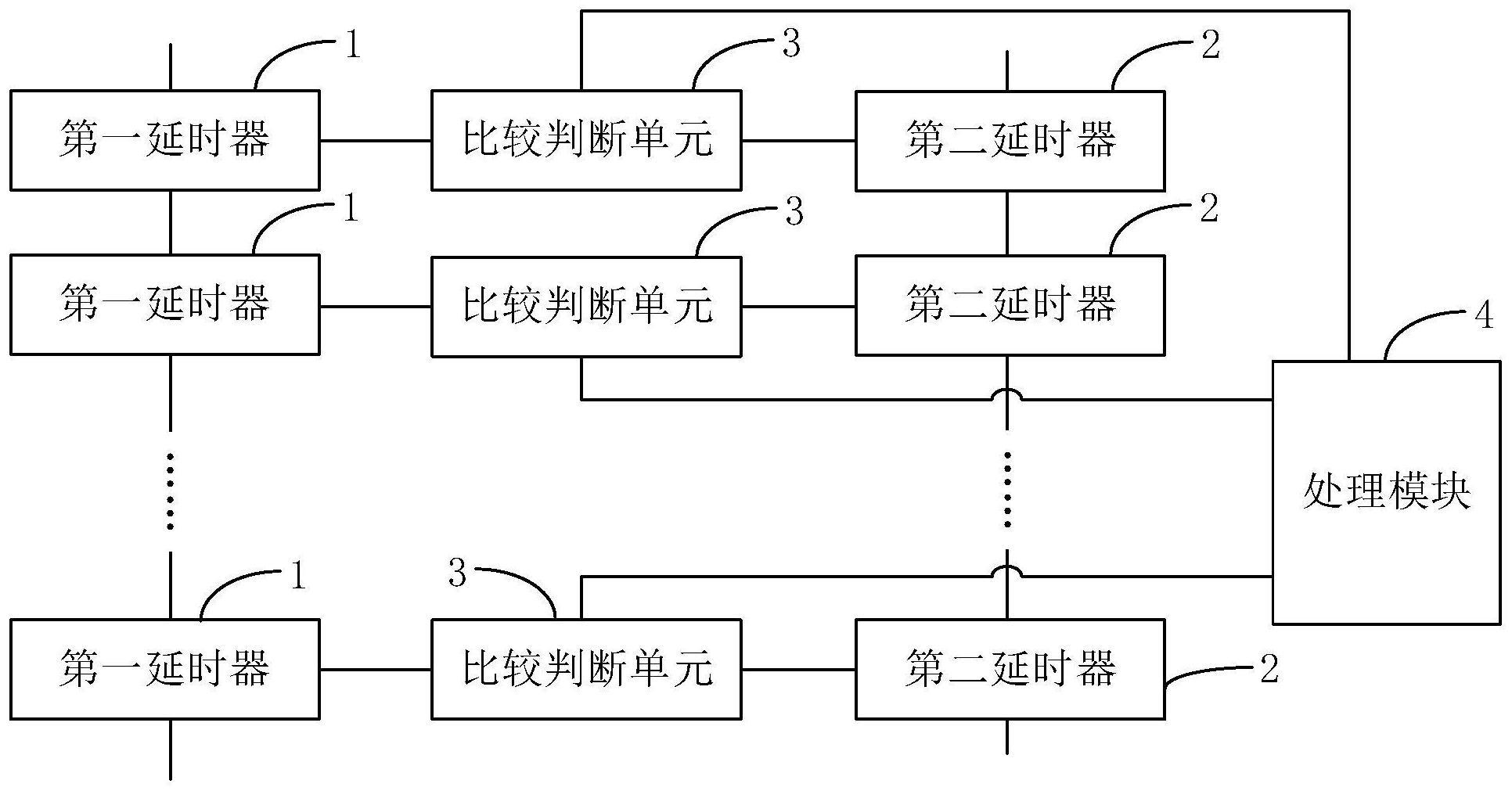

2、根据本发明的第二方面,提供了一种时间间隔测量电路的第二级tdc电路,包括:第一延时线路、第二延时线路与n个比较判断单元,所述第一延时线路包括n个第一延时器,所述第二延时线路包括n个第二延时器;

3、所述n个第一延时器依次连接,并通过其中的第一个第一延时器接收开始信号,所述第一延时线路中的第一延时器用于:传递所述开始信号,并在传递过程中执行所述开始信号的延时;所述n个第二延时器依次连接,并通过其中的第一个第二延时器接收结束信号,所述第二延时线路中的第二延时器用于:传递所述结束信号,并在传递过程中执行所述结束信号的延时;

4、其中,所述第二延时线路对所述结束信号的信号传递速度快于所述第一延时线路对所述开始信号的信号传递速度;

5、每个比较判断单元分别连接对应的一个第一延时器与一个第二延时器,且所述比较判断单元所连接的第一延时器、第二延时器在对应延时线路中的次序是相同的;

6、所述比较判断单元用于确定信号比较信息,所述信号比较信息表征了:该比较判断单元所连接的第一延时器传播中的开始信号的相位领先于还是落后于所连接的第二延时器传播中的结束信号的相位;

7、所述比较判断单元连接处理模块;所述处理模块用于:基于部分或全部比较判断单元的信号比较信息,确定目标时间间隔信息,所述目标时间间隔信息表征了:未经对应延时线路延时之前,所述开始信号与所述结束信号的时间间隔。

8、可选的,所述处理模块在基于部分或全部比较判断单元的信号比较信息,确定目标时间间隔信息时,具体用于:

9、若检测到任一第j个比较判断单元输出的信号比较信息与第j-1个比较判断单元输出的信号比较信息不同,则确定目标数量信息,并基于所述目标数量信息,确定所述目标时间间隔信息,所述目标数量信息表征了:在传播至所述第j个比较判断单元所连接的延时器时,所述开始信号和/或所述结束信号在对应延时线路中已传播经过的延时器的数量。

10、可选的,所述第一延时线路与所述第二延时线路中相对应的第一延时器与第二延时器结构相同,其中的器件尺寸也相同。

11、可选的,所述第一延时器与所述第二延时器均包括信号传输单元与游标延时控制单元;

12、任一延时器的信号传输单元均连接于所述任一延时器所相邻的一个或两个延时器的信号传输单元,用于执行对应信号的传播;所述对应信号为所述开始信号或所述结束信号;所述相邻的一个或两个延时器包括:所述任一延时器的上一个延时器和/或下一个延时器;

13、所述任一延时器的游标延时控制单元连接于所述任一延时器的信号传输单元,用于控制所述第一延时线路与所述第二延时线路之间是否产生延时差。

14、可选的,所述信号传输单元包括级联的第一反相器与第二反相器,所述游标延时控制单元包括第一晶体管与第二晶体管;

15、所述任一延时器中的第一反相器的输入端连接所述上一个延时器的第二反相器的输出端,所述任一延时器中的第二反相器的输入端连接所述任一延时器中的第一反相器的输出端,所述任一延时器中的第二方向器的输出端连接所述下一个延时器中的第一反相器的输入端;

16、在所述任一延时器中,所述第二反相器的输入端还连接所述第一晶体管的控制端,所述第一晶体管的第一端连接所述第二反相器的输出端,所述第一晶体管的第二端连接所述第二晶体管的第一端,所述第二晶体管的第二端接地;

17、其中,所述第一延时器与所述第二延时器中的第二晶体管的控制端接入的信号用于确定是否产生所述延时差。

18、可选的,若任一第k个第一延时器中第二晶体管的控制端接入的信号与第k个第二延时器的第二晶体管的控制端接入的信号为相同电平,则:所述第k个第一延时器与所述第k个第二延时器之间的延时相同;

19、若任一第k个第一延时器中第二晶体管的控制端接入的信号与第k个第二延时器的第二晶体管的控制端接入的信号为不同电平,则:所述第k个第一延时器与所述第k个第二延时器之间的延时呈指定延时差。

20、可选的,所述第一延时器与所述第二延时器均还包括延时校准单元;

21、所述延时校准单元包括多个并联的晶体管,所述多个并联的晶体管连接于所述第一反相器的电源端,所述多个并联的晶体管被配置为能够有选择地导通,以控制对应延时器所实现的延时。

22、可选的,所述比较判断单元连接于所述第一反相器的输出端;

23、所述比较判断单元在判断信号比较信息时,具体用于:通过比较所述第一延时器与所述第二延时器的第一反相器所输出的信号,判断所述信号比较信息。

24、根据本发明的第二方面,提供了一种时间间隔测量电路,包括两级tdc电路;

25、所述两级tdc电路中的第二级为第一方面及其可选方案涉及的第二级tdc电路;

26、所述两级tdc电路中的第一级tdc电路用于获取start信号与stop信号,并确定所述start信号与所述stop信号之间的初步时间间隔信息;

27、输入至所述第二级tdc电路的开始信号为与结束信号的时间间隔匹配于所述第一级tdc电路所确定的初步时间间隔信息。

28、根据本发明的第三方面,提供了一种电子设备,包括第二方面涉及的时间间隔测量电路。

29、本发明提供的时间间隔测量电路及其第二级tdc电路、电子设备中,由于第二级tdc电路采用了包含n个第一延时器的第一延时线路、包含n个第二延时器的第二延时线路与比较判断单元,通过两个延时线路的延时传递及比较判断单元的判断,可准确反应出传递至哪个延时器时结束信号追上开始信号,从而为目标时间间隔信息的确定提供充分的依据,可见,本发明无需采用电荷泵,进而,不会因为电荷泵的采用而导致的分辨率受限等问题,同时,本发明中两条延时线路的延时差可实现对应的分辨率,该分辨率可随延时差的变化而变化,在实施过程中,配置、校准实现合适的延时差之后,即可达到所需的分辨率,所以,本发明为保障分辨率提供了可靠的实现方式。

本文地址:https://www.jishuxx.com/zhuanli/20240730/152431.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表