基于固态等离子体的异质全息成像反射结构及制备方法

- 国知局

- 2024-07-31 18:22:38

本发明属于半导体材料及器件制造,具体涉及基于固态等离子体的异质全息成像反射结构,还涉及基于固态等离子体的异质全息成像反射结构的制备方法。

背景技术:

1、全息成像是一种利用光的干涉原理来记录并重建物体的三维图像的技术。在全息成像中,物体被照射或透过一束光,产生的光波与参考光波相互干涉,形成一幅复杂的干涉图案。这个干涉图案被记录下来,并经过数字化处理。然后,利用数字化的干涉图案,通过复杂的计算算法,可以重建出物体的三维形态和表面信息。与传统的二维成像技术相比,全息成像可以提供更加真实和细致的图像,包括物体的立体形状、表面纹理以及内部结构等信息。因此,全息成像技术在医学、生物学、安全检测、虚拟现实等领域具有广泛的应用前景。然而,目前全息成像大多基于传统器件设计,结构尺寸、相位调制自由度、集成度、多场景智能化应用等方面逐渐不能满足信息系统的要求。基于固态等离子体的异质全息成像反射结构展现出优越的性能、快速动态的可重构性,实时调控电磁波并对信息进行感知与学习,在高分辨率成像、三维成像、安全检测与防伪、光学信息处理、虚拟现实与增强现实等领域具有重要的研究意义和应用前景。

技术实现思路

1、本发明的目的是提供基于固态等离子体的异质全息成像反射结构,通过引入导电沟桥技术,有效提升了器件及系统成像、隐身与集成的性能。

2、本发明的另一目的是提供基于固态等离子体的异质全息成像反射结构的制备方法。

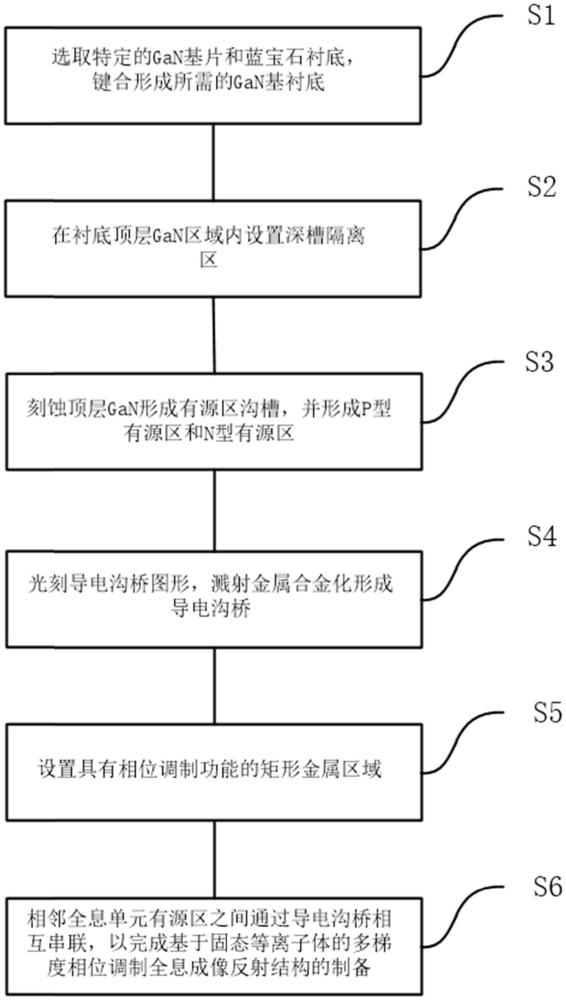

3、本发明所采用的技术方案是,基于固态等离子体的异质全息成像反射结构的制备方法,包括以下步骤:

4、s1.选取特定的gan基片和蓝宝石衬底,键合形成所需的gan基衬底;

5、s2.在衬底顶层gan区域内设置深槽隔离区;

6、s3.刻蚀顶层gan形成有源区沟槽,并形成p型有源区和n型有源区;

7、s4.光刻导电沟桥图形,溅射金属合金化形成导电沟桥;

8、s5.设置具有相位调制功能的矩形金属区域;

9、s6.相邻全息单元有源区之间通过导电沟桥相互串联,以完成基于固态等离子体的多梯度相位调制全息成像反射结构的制备。

10、本发明的特点还在于:

11、s1具体方法为:选取特定的gan基片和蓝宝石衬底,在gan基片和蓝宝石衬底表面分别形成氧化层,键合形成所需gan基衬底。

12、s2具体方法为:在衬底顶层gan表面形成保护层,利用光刻工艺在保护层上形成隔离区图形,利用干法刻蚀工艺在隔离区图形的指定位置处刻蚀保护层及衬底以形成隔离槽,且隔离槽的深度大于等于衬底的顶层gan的厚度,填充隔离槽以形成固态等离子体器件的隔离区,平整化处理衬底;

13、衬底顶层gan表面形成保护层的具体内容为:在衬底顶层gan表面生成二氧化硅层,在二氧化硅层表面生成氮化硅层。

14、s3具体方法为:在衬底表面形成保护层,利用光刻工艺在保护层上形成p型有源区和n型有源区图形,利用干法刻蚀工艺在有源区的指定位置处刻蚀保护层及顶层gan以形成p型沟槽和n型沟槽,有源区沟槽内壁的平整化,利用多晶algan填充p型沟槽和n型沟槽,形成p型有源区和n型有源区;

15、在衬底表面形成保护层的具体方法为:在衬底表面生成二氧化硅层,在二氧化硅层表面生成氮化硅层。

16、有源区沟槽内壁的平整化的具体方法为:氧化p型沟槽和n型沟槽以使p型沟槽和n型沟槽的内壁形成一层二氧化硅氧化层,利用湿法刻蚀工艺刻蚀p型沟槽和n型沟槽内壁的氧化层以完成p型沟槽和n型沟槽内壁的平整化。

17、利用多晶algan填充p型沟槽和n型沟槽的具体方法为:利用多晶algan填充p型沟槽和n型沟槽,平整化处理衬底后,在衬底表面上形成多晶algan层,光刻多晶algan层,并采用带胶离子注入的方法对p型沟槽和n型沟槽所在位置分别注入p型杂质和n型杂质以形成p型有源区和n型有源区且同时形成p型接触区和n型接触区,去除光刻胶,利用湿法刻蚀去除p型接触区和n型接触区以外的多晶algan层。

18、s4具体方法为:在衬底上生成二氧化硅,光刻导电沟桥区域图形,刻蚀形成导电沟桥区域,溅射金属,合金化形成金属硅化物,形成导电沟桥。

19、s5具体方法为:在衬底上生成二氧化硅,利用退火工艺激活有源区中的杂质,钝化处理,设置具有相位调制功能的矩形金属区域。

20、s6具体方法为:设置特定的编码形式,基于编码形成不同的相位分布,相邻全息单元有源区之间通过导电沟桥相互串联,以完成基于固态等离子体的多梯度相位调制全息成像反射结构的制备。

21、本发明所采用的另一技术方案是,基于固态等离子体的异质全息成像反射结构,采用基于固态等离子体的异质全息成像反射结构的制备方法制得。

22、本发明的有益效果是:

23、本发明提供的基于固态等离子体的异质全息成像反射结构及制备方法,通过设置具有相位调制功能的矩形金属区域,实现了全息成像反射结构在0-2π之间的相位自由调控;通过电控固态等离子体数字编码技术实现了全息单元相位的实时重构,将电磁波控制的物理行为与数字电路的编码对应起来,实现了电磁波的灵活调控;通过将导电沟桥设置在相邻器件有源区之间,利用金属硅化物的高导电性取代金属实现器件单元的控制以及相邻器件间的电气连接,在降低有源区串联电阻和接触电阻的同时,完全摆脱了金属接触区域对系统性能的束缚,可有效提升器件及其系统的全息、隐身与集成性能;采用蓝宝石(sapphire)衬底取代传统si衬底,利用蓝宝石出色的电绝缘性、机械性能和化学稳定性,进一步改善固态等离子体全息器件微波特性及其系统性能;algan/gan异质结构的引入使得全息结构在载流子注入比、迁移率、势垒高度、制备技术、晶格匹配等多方面具有优势,大幅提升全息结构的电磁调控与编码能力。

技术特征:1.基于固态等离子体的异质全息成像反射结构的制备方法,包括以下步骤:

2.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s1具体方法为:选取特定的gan基片和蓝宝石衬底,在gan基片和蓝宝石衬底表面分别形成氧化层,键合形成所需gan基衬底。

3.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s2具体方法为:在衬底顶层gan表面形成保护层,利用光刻工艺在保护层上形成隔离区图形,利用干法刻蚀工艺在隔离区图形的指定位置处刻蚀保护层及衬底以形成隔离槽,且隔离槽的深度大于等于衬底的顶层gan的厚度,填充隔离槽以形成固态等离子体器件的隔离区,平整化处理所述衬底;

4.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s3具体方法为:在所述衬底表面形成保护层,利用光刻工艺在所述保护层上形成p型有源区和所述n型有源区图形,利用干法刻蚀工艺在所述有源区的指定位置处刻蚀保护层及顶层gan以形成所述p型沟槽和所述n型沟槽,有源区沟槽内壁的平整化,利用多晶algan填充所述p型沟槽和所述n型沟槽,形成p型有源区和n型有源区;

5.根据权利要求4所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述有源区沟槽内壁的平整化的具体方法为:氧化所述p型沟槽和所述n型沟槽以使p型沟槽和n型沟槽的内壁形成一层二氧化硅氧化层,利用湿法刻蚀工艺刻蚀p型沟槽和n型沟槽内壁的氧化层以完成p型沟槽和n型沟槽内壁的平整化。

6.根据权利要求4所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述利用多晶algan填充所述p型沟槽和所述n型沟槽的具体方法为:利用多晶algan填充所述p型沟槽和所述n型沟槽,平整化处理所述衬底后,在所述衬底表面上形成多晶algan层,光刻所述多晶algan层,并采用带胶离子注入的方法对所述p型沟槽和所述n型沟槽所在位置分别注入p型杂质和n型杂质以形成p型有源区和n型有源区且同时形成p型接触区和n型接触区,去除光刻胶,利用湿法刻蚀去除所述p型接触区和所述n型接触区以外的所述多晶algan层。

7.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s4具体方法为:在所述衬底上生成二氧化硅,光刻导电沟桥区域图形,刻蚀形成导电沟桥区域,溅射金属,合金化形成金属硅化物,形成导电沟桥。

8.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s5具体方法为:在所述衬底上生成二氧化硅,利用退火工艺激活有源区中的杂质,钝化处理,设置具有相位调制功能的矩形金属区域。

9.根据权利要求1所述的基于固态等离子体的异质全息成像反射结构的制备方法,其特征在于,所述s6具体方法为:设置特定的编码形式,基于所述编码形成不同的相位分布,相邻全息单元有源区之间通过导电沟桥相互串联,以完成基于固态等离子体的多梯度相位调制全息成像反射结构的制备。

10.基于固态等离子体的异质全息成像反射结构,其特征在于,采用如权利要求1-9中任意一项所述的方法制得。

技术总结本发明公开了基于固态等离子体的异质全息成像反射结构的制备方法,包括以下步骤:S1.选取GaN基片和蓝宝石衬底,键合形成GaN基衬底;S2.在衬底顶层GaN区域内设置深槽隔离区;S3.刻蚀顶层GaN形成有源区沟槽,并形成P型和N型有源区;S4.光刻导电沟桥图形,溅射金属合金化形成导电沟桥;S5.设置矩形金属区域;S6.相邻全息单元有源区之间通过导电沟桥相互串联,以完成基于固态等离子体的多梯度相位调制全息成像反射结构的制备。本发明还开了基于固态等离子体的异质全息成像反射结构。本发明的基于固态等离子体的异质全息成像反射结构及制备方法,有效提升了器件及系统成像、隐身与集成的性能。技术研发人员:苏汉,贺小敏,路敏,席晓莉,邵琛杰受保护的技术使用者:西安理工大学技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178918.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表