一种基于二氧化钒的MOSFET器件的制作方法

- 国知局

- 2024-07-31 18:44:56

本发明属于半导体,具体涉及一种基于二氧化钒的mosfet器件。

背景技术:

1、场效应管(fet)的主要特点有如下两个方面:1、场效应管有一个由电压控制的栅极,该栅极电压通过电场间接控制源漏电流。2、场效应管的栅极输入电流很小,可以用很小的电流控制源漏大电流。场效应管工作原理用一句话说,就是“漏极-源极间流经沟道的id电流,用栅极与沟道间的pn结形成的反偏的栅极电压进行控制”。

2、金属氧化物制作的fet器件也被称作金属–氧化物–半导体晶体管(mosfet)。自1960年被贝尔实验室的韩裔科学家江大原(dawon.kahng)和马丁.阿塔拉(m.m.atalla)发明以来,mosfet被广泛的应用到大规模及超大规模集成电路中,主要用作二进制计算的逻辑电路。

3、二氧化钒是文献favaloro tela;;suh joonki;;vermeersch bjorn;;liu kai;;gu yijia;;chen long-qing;;wang kevin x;;wu junqiao;;shakouri ali.directobservation of nanoscale peltier and joule effects at metal-insulator domainwalls in vanadium dioxide nanobeams.[j].nano letters,2014公开的相变特性的新材料。二氧化钒的r相与m1相具有一种非常特殊的相变特性,被称之为金属-绝缘体转变(mit)。在340k左右,二氧化钒会从r相转变为m1相,从绝缘体变为金属。在刚发现时,其电阻率会发生2-3个数量级的可逆突变。在后来高质量的单晶材料发现后,这一数量级被提升至4-5个数量级。因此二氧化钒有十分广阔的应用前景。

4、公开号为cn104195552a的发明专利申请公开了一种在硅基底上制备高质量vo2薄膜的方法,用以提高vo2薄膜电阻变化率。选用双面抛光的si基底,首先清洗硅基底,然后采用原子层沉积法在si基底上沉积al2o3缓冲层,最后采用反应磁控溅射法以制备有al2o3缓冲层的si基底为衬底,溅射制备vo2薄膜。上述专利工艺简单,易于实现;制备的si基vo2薄膜具有极强的择优取向,成膜质量高,也更接近于金红石型vo2;通过al2o3缓冲层的引入,减小了相变弛豫时间,也极大的提高了电阻变化率,本发明引入的al2o3缓冲层厚度仅为25nm,并不会造成si基vo2薄膜在作为电致开关或者电致存储器件时其阈值电压过大。

5、但上述专利制备得到的薄膜不能直接应用在半导体器件上,因此,亟需设计一种基于vo2制备且较好利用vo2性能的半导体器件。

技术实现思路

1、本发明提供了一种基于二氧化钒的mosfet器件,该器件能够较好的保留vo2的金属-绝缘体转变(mit)这一特性,进而利用该特性提高mosfet器件的性能。

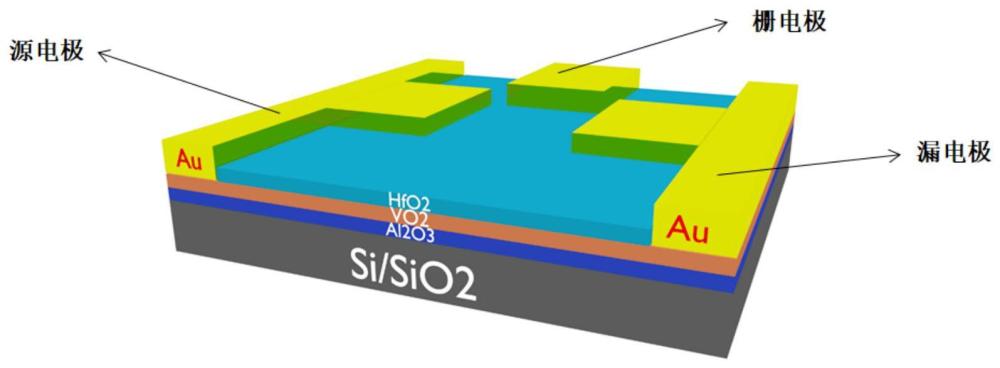

2、本发明具体实施例提供了一种基于二氧化钒的mosfet器件,包括:

3、基底层;

4、过渡层,在所述基底层上方;

5、vo2沟道层,在所述过渡层上方;

6、设置于所述vo2沟道层上的hfo2栅极层、源电极和漏电极,所述源电极和漏电极彼此分割开预定的间隙;

7、栅电极,在所述hfo2栅极层上。

8、依照实施例,向栅极层施加栅压后通过调节温度使得vo2沟道层发生相变,从而实现对所述mosfet器件的电阻的调控,在升温时,施加正向偏压会导致电阻变小;在降温时施加正向偏压会导致电阻变大。

9、依照实施例,通过施加栅极偏压控制vo2本身的相变,从而改变其电阻率,进而控制源漏电流的大小,由于vo2相变温度接近室温,相变时间非常短,且相变可逆,相变前后电学性质、光学性质和磁性等发生巨大变化,因此,本发明提供的mosfet器件具有较好的存储介质材料的性能。

10、依照实施例,通过加入过渡层后,使得本发明提供的mosfet器件能够灵活的更换基底,避免如果vo2沟道层直接生长在基底上时,更换基底会对vo2沟道层产生影响,还避免了如果部分基底具有导电作用,使得vo2沟道层无法发挥作用。

11、依照实施例,将hfo2作为栅极层覆盖在vo2沟道层上,使得vo2沟道层受污染较少,其由于温度的变化产生相变从而产生较高的电阻变化这一性能被较好的保留下来,使得本发明提供的mosfet器件具有较高的开关速度。

12、进一步优选地,所述栅极层的厚度为10-20nm。过薄将导致栅极出现电流泄露现象,过厚会导致栅极调控作用减弱。

13、优选地,所述过渡层的材料为al2o3。

14、进一步优选地,所述过渡层的厚度为40-50nm。合适厚度的al2o3层能够降低vo2薄膜在生长时与底部衬底晶格失配的影响,同时也是作为电介质层与衬底隔离。

15、优选地,所述vo2沟道层的厚度为30-40nm。

16、优选地,所述基底层为si/sio2基底层,所述基底层的厚度为300-500nm。

17、优选地,所述源电极、漏电极和栅电极均是从au电极、pt/au电极中选择任意一个。

18、优选地,所述源漏电极的间距为0.5-1mm。

19、优选地,实现对所述mosfet器件的电阻的调控,包括:向所述mosfet器件施加栅压,使得所述mosfet器件的电阻在200-380k温度范围内随着温度上升而上升,随着温度下降而下降。

20、与现有技术相比,本发明的有益效果为:

21、在现有技术中将vo2作为沟道层时存在沟道层被污染导致vo2的mit特性无法实现的问题,本发明利用hfo2栅极层使得vo2的mit特性能够较好实现,进而首次将vo2作为沟道层来制作mosfet器件,该mosfet器件切实可行地实现了对vo2沟道层的电调控和温度控制,利用vo2在温度变化下能够产生相变从而实现较高的电阻变化率这一工作机制,相比普通的mosfet器件,在物理本质上的开关速度更快,热噪声更低,有很高的应用前景。

技术特征:1.一种基于二氧化钒的mosfet器件,其特征在于,包括:

2.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述hfo2栅极层的厚度为10-20nm。

3.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述过渡层的材料为al2o3。

4.根据权利要求3所述的基于二氧化钒的mosfet器件,其特征在于,所述过渡层的厚度为40-50nm。

5.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述vo2沟道层的厚度为30-40nm。

6.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述基底层为si/sio2基底层,所述基底层的厚度为300-500nm。

7.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述源电极、漏电极和栅电极均是从au电极、pt/au电极中选择任意一个。

8.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,所述源电极和漏电极的间距为0.5-1mm。

9.根据权利要求1所述的基于二氧化钒的mosfet器件,其特征在于,实现对所述mosfet器件的电阻的调控,包括:向所述mosfet器件施加栅压,使得所述mosfet器件的电阻在200-380k温度范围内随着温度上升而上升,随着温度下降而下降。

技术总结本发明公开了一种基于二氧化钒的MOSFET器件,包括从下到上依次设置的Si/SiO<subgt;2</subgt;基底层、Al<subgt;2</subgt;O<subgt;3</subgt;层、VO<subgt;2</subgt;栅极层,在VO<subgt;2</subgt;沟道层上设置HfO<subgt;2</subgt;栅极层和源漏电极,所述HfO<subgt;2</subgt;栅极层将源漏电极隔开,在HfO<subgt;2</subgt;栅极层上设置栅电极层。该器件能够较好的保持栅极层二氧化钒的电阻变化率,从而提高MOSFET器件的性能。技术研发人员:邵云开,陈鑫,戴宁,黄田田,杨万丽受保护的技术使用者:国科大杭州高等研究院技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/180280.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表