硅氮化物的保形沉积的制作方法

- 国知局

- 2024-07-31 18:46:41

本发明涉及半导体设备的制造方法和装置。具体而言,本发明的实施方案涉及用于在半导体处理中进行硅氮化物的保形沉积的方法和装置。

背景技术:

1、在半导体设备的制造中,沉积和蚀刻技术被使用于形成材料图案,例如形成嵌于介电质层中的金属线。沉积技术包括原子层沉积(ald)、化学气相沉积(cvd)和物理气相沉积(pvd)。蚀刻技术包括湿式蚀刻方法和干式蚀刻方法,例如反应性离子蚀刻(rie)。

2、当需要进行保形材料沉积时,ald通常是优选的沉积技术,因为ald依赖于一或更多种反应物的吸附,并且通常会使用表面限制反应而使得所沉积的层的厚度变化最少。

3、这里提供的背景描述是为了总体呈现本公开内容的背景的目的。在此背景技术部分中描述的范围内的当前指定的发明人的工作以及在提交申请时不能确定为现有技术的说明书的各方面既不明确也不暗示地承认是针对本公开内容的现有技术。

技术实现思路

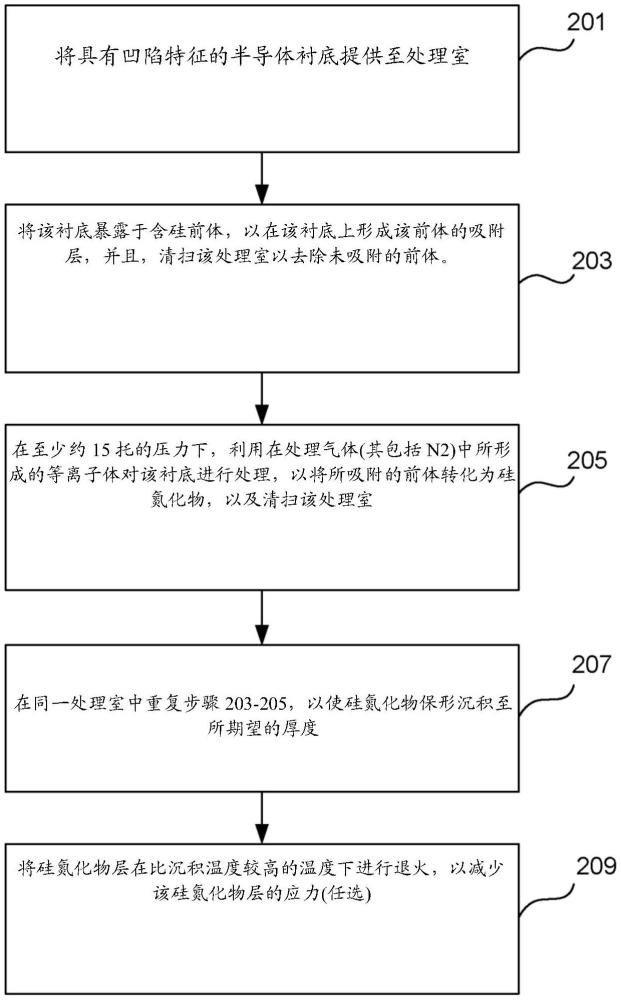

1、高质量的硅氮化物“在稀氢氟酸中具有低的湿式蚀刻速率(wer)的硅氮化物”难以高保形度的方式进行沉积。本文中提供用于沉积硅氮化物的方法和装置。在一些实施方案中,所提供的方法允许硅氮化物以高保形度的方式(例如,具有至少约80%的保形度,如至少约90%或至少约95%的保形度)沉积在凹陷特征中,其中所沉积的该硅氮化物的特征在于在100:1(h2o:hf)的稀水性氢氟酸中具有低的湿式蚀刻速率(例如,小于约/分钟的wer,如小于约/分钟的wer)。在一些实施方案中,所提供的方法允许保形沉积基本上不含氢的硅氮化物,其证据在于ir光谱中缺乏si-h峰和n-h峰。所提供的方法可以用于在高深宽比的凹陷特征中(例如,在深宽比至少为约5:1、至少为约10:1或至少为约50:1的凹陷特征中)沉积硅氮化物衬垫。

2、在一方面,提供了一种在半导体衬底上沉积硅氮化物层的方法。所述方法包括:(a)在沉积处理室中,将所述半导体衬底暴露于不含卤素的含硅前体,以在所述半导体衬底上形成所述含硅前体的吸附层,其中所述含硅前体还包括至少一个氮(n)原子;以及(b)在相同的所述处理室中,利用在包含氮(n2)的处理气体中形成的等离子体对所述半导体衬底进行处理,以将所述含硅前体的所述吸附层转化为硅氮化物,其中从所述含硅前体的所述吸附层到硅氮化物的所述转化是在介于约300℃与约750℃之间的温度和至少约15托的压强下执行。在一些实施方案中,该含硅前体为不含卤素的含硅前体。

3、在一些实施方案中,所述半导体衬底包括至少一个凹陷特征,且所述硅氮化物层以至少约80%的保形度沉积在所述凹陷特征中。此外,以至少约80%的保形度沉积在所述凹陷特征中的所述硅氮化物层可以在100:1的氢氟酸中具有小于约/分钟的湿式蚀刻速率(wer)。例如,在一些实施方案中,所述硅氮化物层以至少90%的保形度沉积在所述凹陷特征中,且所沉积的所述硅氮化物在100:1的氢氟酸中具有小于约/分钟的湿式蚀刻速率(wer)。

4、在一些实施方案中,从所述含硅前体的所述吸附层到硅氮化物的所述转化在介于约400℃与约750℃之间的温度和介于约15托与约30托之间的压强下执行。

5、在一些实施方案中,在所述转化步骤中使用的所述处理气体还包含惰性气体(例如氩),且所述处理气体中的n2含量小于约10体积%,例如小于约5体积%。

6、在一些实施方案中,所述硅氮化物沉积包括至少100个沉积循环,其中每个循环包括一个含硅前体暴露步骤(a)和一个等离子体转化步骤(b)。在一些实施方案中,在含硅前体暴露步骤(a)后将该处理室进行清扫,以移除未吸附的该含硅前体。

7、在一些实施方案中,所述半导体衬底包括深宽比至少为5:1的凹陷特征,且所述硅氮化物被保形沉积在该凹陷特征中达到至少的厚度。

8、在一些实施方案中,该方法涉及将暴露步骤(a)至转化步骤(b)重复进行以形成具有所期望的厚度的完整硅氮化物层;以及通过在缺乏等离子体的情况下,于至少700℃的温度下将所述半导体衬底暴露于n2,以对所述完整的硅氮化物层进行退火,其中所述退火使得硅氮化物的绝对应力值降低。

9、合适的不含卤素的含硅前体(其包括氮)的示例包括但不限于氨基硅烷,例如二(甲基氨基)硅烷(dmas)、二(乙基氨基)硅烷(deas)、二(丙基氨基)硅烷(dpas)、二(异丙基氨基)硅烷(dipas)、二(仲丁基氨基)硅烷(dsbas)、双(叔丁基氨基)硅烷(btbas)以及三(二甲基氨基)硅烷(tdmas)。

10、在一些实施方案中,本文所提供的方法与光刻处理整合在一起。例如,该方法可包括以下步骤:将光致抗蚀剂涂敷于所述半导体衬底上;将所述光致抗蚀剂曝光;将所述光致抗蚀剂图案化,并且将所述图案转移至所述半导体衬底;以及将所述光致抗蚀剂从所述半导体衬底选择性移除。例如,这种光刻图案化可以用于在进行硅氮化物沉积之前在该衬底上形成凹陷特征。

11、在另一方面,提供了一种半导体衬底的处理装置。在一些实施方案中,该装置包括处理室,其被配置成容纳所述衬底,其中所述处理室包括衬底保持件和输入口,所述衬底保持件被配置成保持所述衬底,而所述输入口被配置成将一或更多种反应物引进所述处理室。该装置还包括用于生成等离子体的机构;以及控制器,其具有程序指令,所数据程序指令被配置成致使执行本文所提供的任何方法的步骤。例如,该控制器可以包括程序指令,所述程序指令被配置成通过导致以下操作来实现在所述半导体衬底上沉积硅氮化物层:(i)在沉积处理室中,将所述半导体衬底暴露于不含卤素的含硅前体,以在所述半导体衬底上形成所述含硅前体的吸附层,其中所述含硅前体还包括至少一个氮(n)原子;以及(ii)在相同的所述处理室中,利用在包含氮(n2)的处理气体中形成的等离子体对所述半导体衬底进行处理,以将所述含硅前体的所述吸附层转化为硅氮化物,其中从所述含硅前体的所述吸附层到硅氮化物的所述转化是在介于约300℃与约750℃之间(例如介于约400℃与约750℃之间)的温度和至少约15托(例如介于约15托与约30托之间)的压强下执行。该控制器还可包括用于重复步骤(i)至(ii)以执行至少100个沉积循环的程序指令。在一些实施方案中,所述程序指令被配置成致使将该半导体衬底暴露于不含卤素的含硅前体,其中该不含卤素的含硅前体是氨基硅烷,所述氨基硅烷选自于由二(甲基氨基)硅烷(dmas)、二(乙基氨基)硅烷(deas)、二(丙基氨基)硅烷(dpas)、二(异丙基氨基)硅烷(dipas)、二(仲丁基氨基)硅烷(dsbas)、双(叔丁基氨基)硅烷(btbas)以及三(二甲基氨基)硅烷(tdmas)组成的群组。

12、在一些实施方案中,所述程序指令被配置成致使所述硅氮化物以至少约80%的保形度而保形沉积在凹陷特征中。

13、在另一方面,提供了一种系统,其中该系统包括本文所提供的沉积装置及步进器。

14、在另一方面,提供了一种非临时计算机机器可读介质,其中该非临时计算机机器可读介质包括用于控制装置的程序指令,所述装置被配置用于半导体衬底处理,其中所述程序指令包括代码,所述代码被配置成实现:(i)在沉积处理室中,将所述半导体衬底暴露于不含卤素的含硅前体,以在所述半导体衬底上形成所述含硅前体的吸附层,其中所述含硅前体还包括至少一个氮(n)原子;以及(ii)在相同的所述处理室中,利用在包含氮(n2)的处理气体中形成的等离子体对所述半导体衬底进行处理,以将所述含硅前体的所述吸附层转化为硅氮化物,其中从所述含硅前体的所述吸附层到硅氮化物的所述转化是在介于约300℃与约750℃之间的温度和至少约15托的压强下执行。

15、在另一方面,提供了一种在半导体衬底上沉积硅氮化物层的方法,其中该方法包括:(a)在沉积处理室中,将所述半导体衬底暴露于不含卤素的含硅前体,以在所述半导体衬底上形成所述含硅前体的吸附层,其中所述含硅前体还包括氮(n);以及(b)在相同的所述处理室中,利用在包含氮(n2)的处理气体中形成的等离子体对所述半导体衬底进行处理,以将所述含硅前体的所述吸附层转化为硅氮化物,其中从所述含硅前体的所述吸附层到硅氮化物的所述转化是在介于约300℃与约750℃之间的温度下执行,且其中所述处理气体中的n2含量小于约10%。

16、本说明书中所述的主题的实现方案的这些及其他方面被阐述于附图及下文的描述中。

本文地址:https://www.jishuxx.com/zhuanli/20240731/180416.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表