电子封装件及其封装基板与制法的制作方法

- 国知局

- 2024-07-31 18:59:52

本发明有关一种半导体封装制程,尤指一种具有abf的电子封装件及其封装基板与制法。

背景技术:

1、随着终端产品的功能需求增加,半导体芯片需具备更多的输入/输出(i/o)接点,因而用于承载半导体芯片的封装基板的外接垫的数量亦相对应增加。

2、目前应用于芯片封装领域的技术繁多,例如芯片尺寸构装(chip scale package,简称csp)、芯片直接贴附封装(direct chip attached,简称dca)或多芯片模块封装(multi-chip module,简称mcm)等覆晶型态的封装模块,亦或将芯片立体堆叠化整合为三维集成电路(3d ic)芯片堆叠技术等。

3、图1为现有半导体封装件1的剖面示意图。如图1所示,该半导体封装件1的制法先提供一硅中介板(through silicon interposer,简称tsi)10,该硅中介板10具有相对的置晶侧10a与转接侧10b及连通该置晶侧10a与转接侧10b的多个导电硅穿孔(through-silicon via,简称tsv)100,且该置晶侧10a上具有一电性连接该些导电硅穿孔100的线路重布层(redistribution layer,简称rdl)12;接着,将一半导体芯片11以其电极垫110借由多个焊锡凸块111电性结合至该线路重布层12上,并于该半导体芯片11与该硅中介板10之间填充底胶(underfill)112以包覆该些焊锡凸块111;之后,将一封装基板16以其焊垫160借由多个如焊料凸块或铜柱的c4规格导电元件15电性结合于该导电硅穿孔100上,并于该硅中介板10与该封装基板16之间填充另一底胶17以包覆该些导电元件15;最后,于该封装基板16底侧接置多个焊球19以外接一电路板(图略)。

4、惟,现有半导体封装件1中,采用硅中介板10作为半导体芯片11与电路板之间信号传递的介质,故于制作该硅中介板10时,需制作现有导电硅穿孔100及c4规格导电元件15等制程,因而大幅增加制程难度及制作成本,且该封装基板16需通过该导电元件15传导电性信号及散热,致使该封装基板16的导电效能及散热效能不佳。

5、再者,该硅中介板10需借由该些导电元件15设于该封装基板16上,致使该半导体封装件1的整体厚度难以降低,导致应用该半导体封装件1的电子产品难以符合微小化的需求。

6、另外,现有半导体封装件1于制作过程中,该封装基板16与该硅中介板10之间的热膨胀系数(cte)不匹配(mismatch),因而容易发生热应力不均匀的情况,致使于后续回焊焊锡凸块111、导电元件15与焊球19时,该封装基板16会产生极大的翘曲(warpage),以致于发生植球状况不佳(即该焊球19掉落)、焊球19不沾锡(non-wetting)或该封装基板16裂开等可靠度问题,进而导致应用该半导体封装件1的终端电子产品(如电脑、手机等)发生可靠度问题。

7、另外,硅材与金属材的结合性不佳,因而不利于制作该线路重布层12,使该线路重布层12与该硅中介板10容易发生分离的风险。

8、因此,如何克服上述现有制法的种种问题,实已成目前亟欲解决的课题。

技术实现思路

1、鉴于上述现有技术的种种缺失,本发明提供一种电子封装件及其封装基板与制法,可至少部分地解决现有技术的问题。

2、本技术的封装基板,包括:布线结构,其具有相对的第一侧与第二侧,其中,该布线结构包含至少一绝缘层及设于该绝缘层上的布线层,且形成该绝缘层的材质为味之素增层膜(ajinomoto build-up film);第一线路结构,其设于该布线结构的第一侧上,其中,该第一线路结构包含至少一形成于该绝缘层上的第一介电层及设于该第一介电层上且电性连接该布线层的第一线路层,且形成该第一介电层的材质不同于形成该绝缘层的材质;以及第二线路结构,其设于该布线结构的第二侧上,其中,该第二线路结构包含至少一形成于该绝缘层上的第二介电层及设于该第二介电层上且电性连接该布线层的第二线路层,且形成该第二介电层的材质不同于形成该绝缘层的材质。

3、前述的封装基板中,该第一线路结构结合至一核心板体,该核心板体具有相对的第一表面及第二表面,以令该第一线路结构结合至该核心板体的第一表面上,且该核心板体具有多个连通该第一与第二表面的导电通孔,以令该导电通孔电性连接该第一线路层。

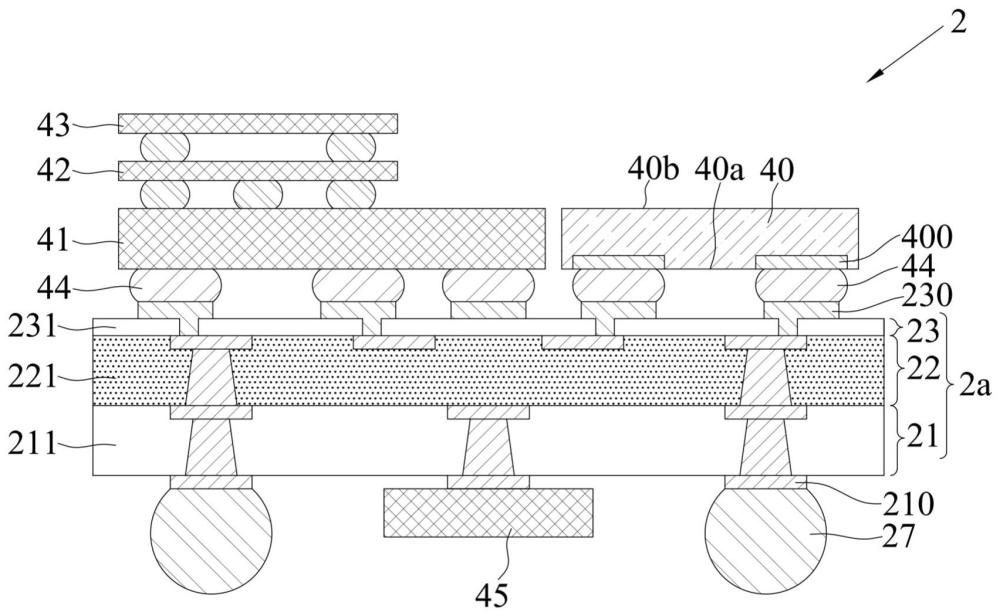

4、本发明亦提供一种电子封装件,包括:前述的封装基板;以及电子元件,其设于该第二线路结构上且电性连接该第二线路层。

5、本发明又提供一种封装基板的制法,包括:形成布线结构于一承载件上,该布线结构具有相对的第一侧与第二侧,以令该布线结构以其第二侧结合该承载件,其中,该布线结构包含至少一绝缘层及设于该绝缘层上的布线层,且形成该绝缘层的材质为味之素增层膜(ajinomoto build-up film);形成第一线路结构于该布线结构的第一侧上,其中,该第一线路结构包含至少一形成于该绝缘层上的第一介电层及设于该第一介电层上且电性连接该布线层的第一线路层,且形成该第一介电层的材质不同于形成该绝缘层的材质;移除该承载件,以外露出该布线结构的第二侧;以及形成第二线路结构于该布线结构的第二侧上,其中,该第二线路结构包含至少一形成于该绝缘层上的第二介电层及设于该第二介电层上且电性连接该布线层的第二线路层,且形成该第二介电层的材质不同于形成该绝缘层的材质。

6、本发明还提供一种封装基板的制法,包括:提供一核心板体,其具有相对的第一表面及第二表面,且该核心板体具有多个连通该第一与第二表面的导电通孔;形成第一线路结构于该核心板体的第一表面上,其中,该第一线路结构包含至少一形成于该核心板体上的第一介电层及设于该第一介电层上且电性连接该导电通孔的第一线路层;形成布线结构于该第一线路结构上,且该布线结构具有相对的第一侧与第二侧,以令该布线结构以其第一侧结合该第一线路结构,其中,该布线结构包含至少一形成于该第一介电层上的绝缘层及设于该绝缘层上的布线层,且形成该绝缘层的材质为味之素增层膜(ajinomoto build-up film),其不同于形成该第一介电层的材质;以及形成第二线路结构于该布线结构的第二侧上,其中,该第二线路结构包含至少一形成于该绝缘层上的第二介电层及设于该第二介电层上且电性连接该布线层的第二线路层,且形成该第二介电层的材质不同于形成该绝缘层的材质。

7、前述的封装基板及其两种制法中,该第一与第二介电层的材质相异。

8、本发明另提供一种电子封装件的制法,包括:提供一前述的封装基板;以及将电子元件设于该第二线路结构上,且该电子元件电性连接该第二线路层。

9、前述的电子封装件及其制法,还包括形成外接元件于该第一线路结构上,且该外接元件电性连接该第一线路层。

10、由上可知,本发明的电子封装件及其封装基板与制法,主要借由abf作为绝缘层以取代现有硅板体,并利用布线层作为电子元件与电路板之间信号传递的介质,故相较于现有技术,本发明无需制作现有硅中介板有关导电硅穿孔及c4规格导电元件等的制程,因而能大幅降低制程难度及制作成本,且该封装基板的导电效能及散热效能大幅提升。

11、再者,本发明借由该布线结构直接接合该第一线路结构的设计,以取代现有硅中介板及c4规格导电元件的配合,使本发明的封装基板的厚度有利于薄化需求。

12、另外,借由形成该绝缘层的材质不同于形成该第一与第二介电层的材质,以利于分散热应力,使本发明的封装基板于后续制程中可有效避免发生翘曲的问题。

13、另外,本发明借由abf作为绝缘层的设计,以利于采用rdl制程制作该第二线路结构,使该第二线路层有利于符合高密度的细线路/细间距的需求,且能降低该第二线路结构与该布线结构发生分离的风险。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181295.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表