一种基于SOI工艺的CMOS集成电路基本单元

- 国知局

- 2024-07-31 19:05:50

本发明属于微电子,具体涉及一种基于soi工艺的cmos集成电路基本单元。

背景技术:

1、集成电路技术快速发展,从摩尔定律[1]提出开始,集成电路的发展一直遵循按比例缩小原则。随着器件尺寸的日益减小,等比例缩小原则开始面临严峻的挑战。finfet为鳍式场效应晶体管,其主要特点为沟道区域是一个被栅极包裹的鳍状半导体,沿源漏方向的鳍的长度,为沟道长度。与传统的平面cmos相比,finfet的半环栅鳍形结构增加了栅极对沟道的控制面积,使得栅控能力大大增强,从而可以有效抑制短沟效应,减小亚阈值漏电流。现有技术中还提出了环绕式栅极(gate-all-around)晶体管结构,该结构中其栅极和源漏不再维持鳍形的样子,而是柱体结构垂直穿过栅极,因此栅极可以从四面包裹沟道,延续了finfet立体结构的思路,从而最大程度地实现栅极对沟道区的控制,更好控制短沟道及dibl等效应,实现更大的功耗和面积优势。但是根据irds给出的数据,5nm finfet的栅长实际为18nm,后续的工艺节点下,沟道长度lch也很难按比例缩小,造成cmos集成电路小型化困难。

技术实现思路

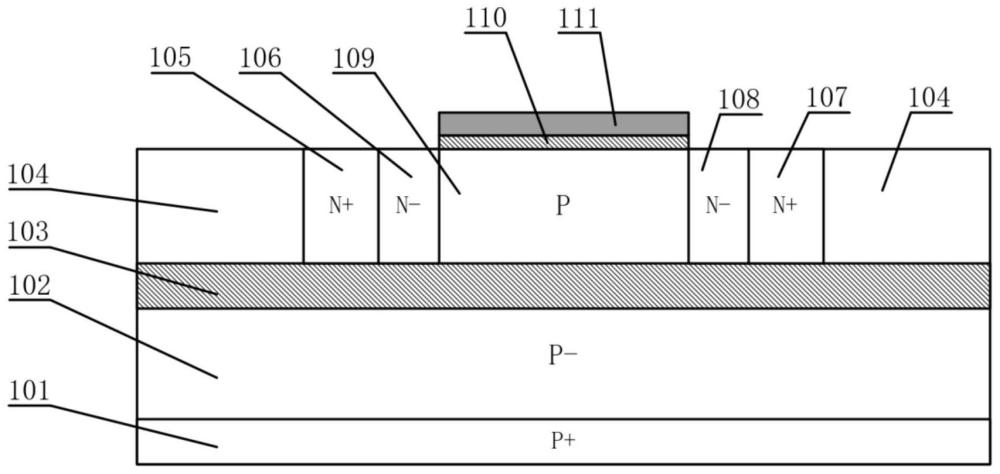

1、为解决以上现有技术存在的问题,本发明提出了一种基于soi工艺的cmos集成电路基本单元,该单元结构包括:从下到上依次设置有硅单晶半导体区域、外延硅单晶区域、soi区域以及晶体管;晶体管由硅单晶半导体区、沟道区、漂移区、源区、漏区、栅极氧化层以及多晶硅电极组成;其中沟道区设置在soi层上表面的中心区域,沟道区的两侧分别设置漂移区,在两个漂移区的外侧分别设置源区和漏区,在源区和漏区的外侧均设置硅单晶半导体区,沟道区顶部依次设置栅极氧化层和多晶硅电极。

2、本发明的有益效果:

3、本发明基于soi工艺在源区和漏区增加漂移区,使得沟道区的掺杂浓度远大于轻掺杂源漏漂移区的掺杂浓度,当该处得到pn结处于反偏时,耗尽区向轻掺杂源漏区延伸,几乎不会向沟道区扩展;通过这种结构保证了沟道区的势垒处于稳定状态,极大的降低了dibl效应;由于沟道区重掺杂,即使沟道长度做到几纳米,也可以有效抑制dibl效应;本发明能够极大减小沟道长度,结合目前国内已经成熟的硅平面工艺制程,使用平面工艺也可以做到沟道长度12nm以下,提高芯片集成度。

技术特征:1.一种基于soi工艺的cmos集成电路基本单元,其特征在于,包括:从下到上依次设置有硅单晶半导体区域、外延硅单晶区域、soi区域以及晶体管;晶体管由硅单晶半导体区、沟道区、漂移区、源区、漏区、栅极氧化层以及多晶硅电极组成;其中沟道区设置在soi层上表面的中心区域,沟道区的两侧分别设置漂移区,在两个漂移区的外侧分别设置源区和漏区,在源区和漏区的外侧均设置硅单晶半导体区,沟道区顶部依次设置栅极氧化层和多晶硅电极。

2.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,soi区域采用的材料为sio2。

3.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,沟道区的长度范围为2nm~100nm。

4.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,源区的长度范围为2nm~1000nm,漏区的长度范围与源区的长度范围相同。

5.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,漂移区的长度范围为2nm~1000nm。

6.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,硅单晶半导体的厚度范围为2nm~2000nm,且沟道区、漂移区、源区以及漏区的厚度与硅单晶半导体的厚度相同。

7.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,soi区域的厚度范围为2nm~2000nm。

8.根据权利要求1所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,晶体管中各个区域的掺杂浓度范围为1e14cm-3-1e22 cm-3。

9.根据权利要求8所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,沟道区的掺杂浓度比漂移区的参杂浓度至少高一个数量级。

10.根据权利要求8所述的一种基于soi工艺的cmos集成电路基本单元,其特征在于,源区和漏区的掺杂浓度比沟道区的掺杂浓度高至少1个数量级。

技术总结本发明属于微电子技术领域,具体涉及一种基于SOI工艺的CMOS集成电路基本单元,包括:从下到上依次设置有硅单晶半导体区域、外延硅单晶区域、SOI区域以及晶体管;晶体管由硅单晶半导体区、沟道区、漂移区、源区、漏区、栅极氧化层以及多晶硅电极组成;其中沟道区设置在SOI层上表面的中心区域,沟道区的两侧分别设置漂移区,在两个漂移区的外侧分别设置源区和漏区,在源区和漏区的外侧均设置硅单晶半导体区,沟道区顶部依次设置栅极氧化层和多晶硅电极;本发明基于SOI工艺在源区和漏区增加漂移区,抑制短沟道效应,进而可以提高IC集成度,节约芯片面积。技术研发人员:廖永波,徐丰和受保护的技术使用者:电子科技大学重庆微电子产业技术研究院技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181622.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。