用于多目标模拟的双口RAM读出方法及电路与流程

- 国知局

- 2024-07-31 19:09:09

本发明涉及智能硬件,尤其涉及一种用于多目标模拟的双口ram读出方法及电路。

背景技术:

1、在电子对抗领域,雷达信号干扰发挥着越来越重要的作用,其可以对敌方雷达进行干扰进而掩护我方行动。在当前雷达干扰模式中,基于数字射频存储器(digital radiofrequency memory,drfm)模式的密集假目标干扰可以促使敌方雷达失去对我方目标的捕捉能力。当前实现假目标方法主要通过双口随机存取存储器(random access memory,ram)实现,系统一边通过现场可编程门阵列(field-programmable gate array,fpga)向ram中写入目标信息,另一方面根据模拟的假目标的距离和数量对ram进行读出,读出后的数据经调制输出,进而起到干扰作用。

2、实现该功能的一种方法是利用fpga内部存储资源实现,然而当模拟目标较多、或者面对大脉宽雷达信号时,fpga内部存储资源往往无法达到要求。还有一种是通过外挂四倍数据速率静态随机存取存储器(quad data rate static random access memory,qdrsram)方式,进行存储及读写控制实现,但是,当需要同时模拟多目标时,需要多个相应存储颗粒,这会导致系统体积增大,同时消耗大量fpga管脚,也对fpga性能提出了更高要求。

3、因此在进行多目标模拟时,急需一种新型ram或者方法在能提高模拟目标的数目的同时,对fpga的性能需求也不能产生太大影响。

技术实现思路

1、本发明主要目的:在模拟多个目标输出同时,避免消耗过多的fpga内部存储资源,保证fpga处理资源的利用效率,同时避免使用多个相应存储颗粒,导致系统体积增大,且消耗大量fpga管脚的问题。

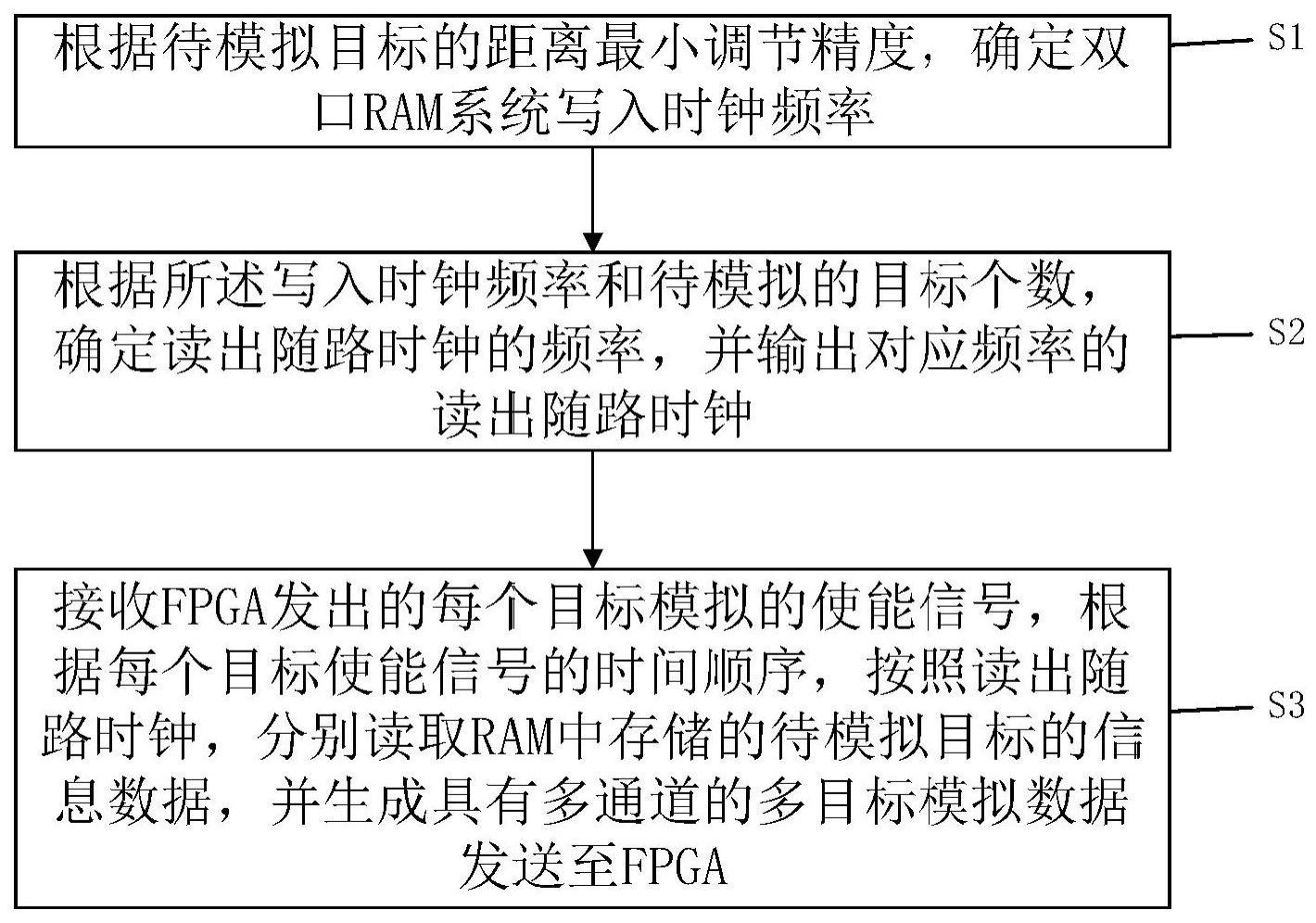

2、本发明提供一种用于多目标模拟的双口ram读出方法,包括:根据待模拟目标的距离最小调节精度,确定双口ram系统写入时钟频率;根据所述写入时钟频率和待模拟的目标个数,确定读出随路时钟的频率,并输出对应频率的读出随路时钟;接收fpga发出的每个目标模拟的使能信号,根据每个目标使能信号的时间顺序,按照所述读出随路时钟,分别读取ram中存储的待模拟目标的信息数据,并生成具有多通道的多目标模拟数据发送至fpga;其中,每个目标的使能信号为fpga根据每个目标的距离所对应的延迟时刻发出,所述多目标模拟数据中的每个通道与每个模拟目标对应。

3、基于本发明的用于多目标模拟的双口ram读出方法,所述输出对应频率的读出随路时钟,包括:根据读出随路时钟的频率和锁相环中压控震荡器的频率输出范围,确定分频器的分频比,以使所述压控震荡器根据所述分频比经所述分频器分频后,产生满足已确定频率的读出随路时钟。

4、基于本发明的用于多目标模拟的双口ram读出方法,还包括:将所述读出随路时钟信号发送至fpga,以用于fpga根据所述读出随路时钟信号和所述多目标模拟数据,并基于每个目标模拟的使能信号,解析出每个通道的目标模拟数据。

5、基于本发明的用于多目标模拟的双口ram读出方法,所述根据每个目标的使能信号分别读取ram中存储的待模拟目标的信息数据之前,还包括:根据待模拟目标信息数据的起止信息,通过fpga的控制信号,将待模拟目标的信息数据写入到ram对应地址中。

6、基于本发明的用于多目标模拟的双口ram读出方法,还包括:在数据读出地址超过写入地址,或者写入的目标数据量超过存储器的总容量,或者收到新目标模拟指令的情况下,终止读取ram中存储的待模拟目标的信息数据。

7、本发明还提供一种用于多目标模拟的双口ram读出方法,包括:根据每个目标的距离所对应的延迟时刻,向双口ram发出每个目标模拟的使能信号;接收双口ram读取后发送的具有多通道的多目标模拟数据;其中,所述多目标模拟数据,为双口ram根据每个目标使能信号的时间顺序,按照所述读出随路时钟,分别读取ram中存储的待模拟目标的信息数据后生成;所述读出随路时钟的频率,根据系统写入时钟频率和多目标个数确定;所述系统写入时钟频率,根据待模拟目标的距离最小调节精度确定;所述多目标模拟数据中每个通道与每个模拟目标对应。

8、基于本发明的用于多目标模拟的双口ram读出方法,所述接收双口ram读取后发送的具有多通道的多目标模拟数据之后,还包括:根据所述读出随路时钟信号和所述多目标模拟数据,并基于每个目标模拟的使能信号,解析出每个通道的目标模拟数据。

9、本发明还提供一种用于多目标模拟的双口ram读出电路,包括:数据写入模块、存储阵列、锁相环、分频器、目标个数控制模块和数据读出模块;所述数据写入模块,用于将待模拟目标的信息数据写入存储阵列;所述存储阵列,用于对写入的信息数据进行存储保持;所述目标个数控制模块,用于向所述分频器提供待模拟的目标个数;所述锁相环,用于根据输入的系统写入时钟产生高频时钟,所述高频时钟经所述分频器分频后得到读出随路时钟,其中,所述读出随路时钟频率根据双口ram系统写入时钟频率和目标个数控制模块提供的目标个数确定;所述数据读出模块,用于接收fpga发出的每个目标模拟的使能信号,根据每个目标使能信号的时间顺序,按照所述读出随路时钟,分别读取ram中存储的待模拟目标的信息数据,并生成具有多通道的多目标模拟数据发送至fpga;其中,每个目标的使能信号为fpga根据每个目标的距离所对应的延迟时刻发出,所述多目标模拟数据中的每个通道与每个模拟目标对应。

10、基于本发明的用于多目标模拟的双口ram读出电路,还包括保护控制模块,用于:在数据读出地址超过写入地址,或者写入的目标数据量超过存储器的总容量,或者收到新目标模拟指令的情况下,终止读取ram中存储的待模拟目标的信息数据。

11、基于本发明的用于多目标模拟的双口ram读出电路,所述分频器为第二分频器,所述锁相环包括鉴相器、低通滤波器、压控振荡器及第一分频器;读取时钟、所述鉴相器、所述低通滤波器、所述压控振荡器依次连接;所述压控振荡器根据所述读取时钟得到的高频信号,分别通过第一分频器与鉴相器连接,以及通过所述第二分频器分频得到所述读出随路时钟后,连接至所述数据读出模块。

12、本发明产生的有益效果是:根据写入时钟频率和目标个数确定读出时钟频率,配合外部的fpga相应控制逻辑的使能信号,实现单通道模拟信号输入而多个目标的同时模拟输出,并且可以通过设定该目标是否使能,进而控制每个目标的输出延时,进而实现虚假目标体或者虚假场景的模拟。相比较与当前的同时产生多目标方式,本发明的方法可以大大节约fpga资源,减小多目标下状态下常规ram芯片数目,有利于同时进行多目标模拟系统的小型化和集成化。

技术特征:1.一种用于多目标模拟的双口ram读出方法,其特征在于,包括:

2.根据权利要求1所述的用于多目标模拟的双口ram读出方法,其特征在于,所述输出对应频率的读出随路时钟,包括:

3.根据权利要求1所述的用于多目标模拟的双口ram读出方法,其特征在于,还包括:

4.根据权利要求1所述的用于多目标模拟的双口ram读出方法,其特征在于,所述根据每个目标的使能信号分别读取ram中存储的待模拟目标的信息数据之前,还包括:

5.根据权利要求1或4所述的用于多目标模拟的双口ram读出方法,其特征在于,还包括:

6.一种用于多目标模拟的双口ram读出方法,其特征在于,包括:

7.根据权利要求6所述的用于多目标模拟的双口ram读出方法,其特征在于,所述接收双口ram读取后发送的具有多通道的多目标模拟数据之后,还包括:

8.一种用于多目标模拟的双口ram读出电路,其特征在于,包括:

9.根据权利要求8所述的用于多目标模拟的双口ram读出电路,其特征在于,还包括保护控制模块,用于:

10.根据权利要求8所述的用于多目标模拟的双口ram读出电路,其特征在于,所述分频器为第二分频器,所述锁相环包括鉴相器、低通滤波器、压控振荡器及第一分频器;

技术总结本发明公开了一种用于多目标模拟的双口RAM读出方法及电路,属于智能硬件技术领域,该方法包括:根据待模拟目标的距离最小调节精度,确定写入时钟频率;根据写入时钟频率和待模拟的目标个数,确定读出随路时钟的频率,并输出对应频率的读出随路时钟;接收FPGA发出的每个目标模拟的使能信号,并根据每个目标使能信号的时间顺序分别读取RAM中存储的待模拟目标的信息数据,按照读出随路时钟生成具有多通道的多目标模拟数据发送至FPGA;其中,每个目标的使能信号为FPGA根据每个目标的距离所对应的延迟时刻发出,多目标模拟数据中的通道与模拟目标一一对应。该方法可以大大节约FPGA资源,减小多目标下状态下常规RAM芯片数目。技术研发人员:张怀东,周巧玲,谭亮受保护的技术使用者:武汉贞坤电子有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181759.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。