存算一体存储器及其执行同态运算的方法与流程

- 国知局

- 2024-07-31 19:13:44

本发明涉及集成电路,特别涉及一种存算一体存储器及其执行同态运算的方法。

背景技术:

1、非同态加密方案在普通的加密传输方面表现良好,但是随着云计算、联邦学习等概念的兴起,非同态加密如果要进行运算,必须得进行解密后再进行运算,这就对数据的安全性提出挑战且加解密过程还会占用较大计算资源;而同态加密后的密文可以直接在云端对密文进行运算,这样就能保证加密计算过程的数据安全性。而这个过程中,必须使用同态计算进行数据处理。

2、但传统的同态计算架构,同态运算会造成需要处理的数据量极大,因此数据通信的消耗也很大,且整个系统的功耗很大。

技术实现思路

1、本发明的目的在于提供一种存算一体存储器及其执行同态运算的方法,以解决现有的同态运算架构需要处理的数据量极大的问题。

2、为解决上述技术问题,本发明提供一种存算一体存储器,包括:

3、存算一体存储单元,其被配置根据控制信号为对第一输入数据与第二输入数据执行加法运算和/或乘法运算和/或乘加运算;以及

4、控制器,其被配置为将第一输入数据与第二输入数据的同态运算转换为加法运算和/或乘法运算和/或乘加运算并且向所述多个存算一体存储单元发送相应控制信号。

5、可选的,在所述的存算一体存储器中,其中存算一体存储单元包括:

6、被配置为存储至少部分输入数据的输入组件;

7、包括多个存储单元的存储阵列;

8、被配置为在模拟模式或数字模式下运行的外围逻辑;和

9、控制电路,其被配置为:

10、在数字模式下,使能外围逻辑进行乘法运算或累加运算;和

11、在模拟模式下,使能外设逻辑以执行移位加运算并生成部分和。

12、可选的,在所述的存算一体存储器中,其中存算一体存储单元包括:

13、存内计算电路,被配置为对输入数据和/或存储数据进行逻辑运算,以形成中间计算结果,其中所述输入数据和存储数据表征浮点数;以及

14、浮点计算电路,被配置为对输入数据和/或中间计算结果进行浮点运算,以形成最终计算结果;

15、输入数据和/或存储数据包括第一输入数据和/或第二输入数据。

16、可选的,在所述的存算一体存储器中,其中所述存算一体存储单元包括暂存空间,所述暂存空间被配置为存储第一输入数据和第二输入数据以及中间计算结果。

17、可选的,在所述的存算一体存储器中,其中第一输入数据c1和第二多项式c2为密文,所述密文是经过基于多项式环空间的同态加密的密文,其中所述控制器被配置为执行下列动作中的一个或多个:

18、根据下列公式将同态加法转换为加法运算和/或乘法运算和/或乘加运算:

19、homadd(c1,c2)=([c1[0]+c2[0]]q,[c1[1]+c2[1]]q);

20、其中运算[·]q定义为:

21、根据下列公式将同态减法转换为加法运算和/或乘法运算和/或乘加运算:

22、homsub(c1,c2)=([c1[0]-c2[0]]q,[c1[1]-c2[1]]q);

23、根据下列公式将同态乘法转换为加法运算和/或乘法运算和/或乘加运算:

24、hommul(c1,c2)=(cx+<rlk0,cz>,cy+<rlk1,cz>);

25、其中rlk为重线性化密钥,由两个多项式组成,rlk=(rlk0,rlk1),<> 为内积操作,其中:

26、

27、

28、

29、可选的,在所述的存算一体存储器中,直接将存内计算与同态加密后的密文运算进行结合,以进行同态加法和/或乘法运算;

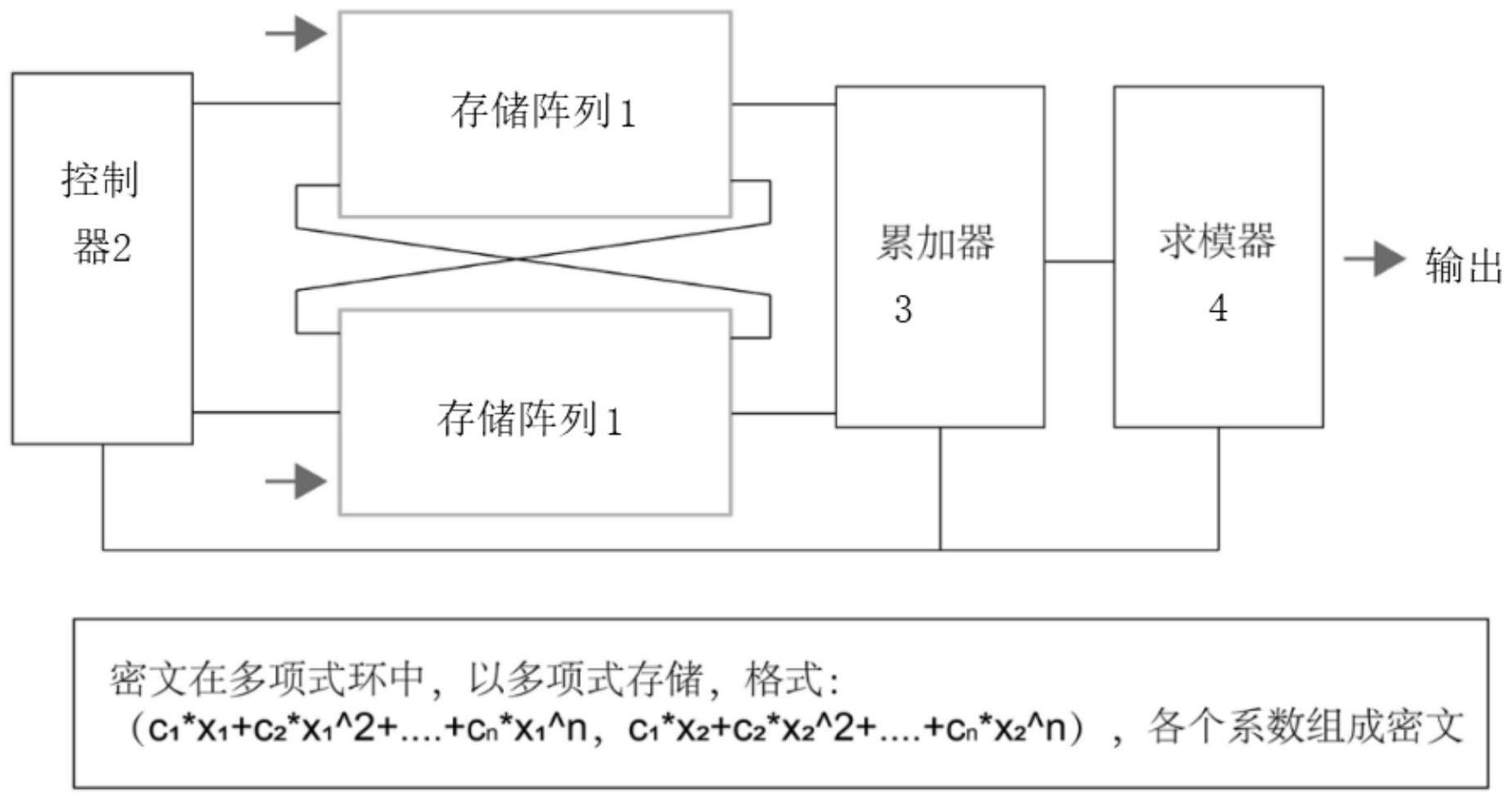

30、存算一体存储单元包括存储阵列,存内计算的功能基于存储阵列设计,存储阵列能够支持同态运算,以减少数据传输所需要的功耗。

31、可选的,在所述的存算一体存储器中,存储阵列包括多个存储单元,单个存储单元的存储空间能够满足第一加密度阈值的多项式单个系数的存储空间,或单个存储单元拆解为多个系数的存储空间,以满足第二加密度阈值的情况;

32、在进行同态加法或乘法时,多项式不同项的系数能够在存算一体存储单元内部同时进行运算,以提高并行度及减少计算所需时间。

33、可选的,在所述的存算一体存储器中,其中存储阵列为sram阵列,以n个bit数据为一个单位进行存储,n为正整数;

34、存储单元还包括本地处理单元、第一输出端和第二输出端,本地处理单元配置逻辑计算功能,第一输出端输出该存储单元输入数据与存储数据的单bit计算结果;

35、在逻辑计算功能为and的情况下,经过移位加法器的处理,第二输出端输出该存储单元输入数据与存储数据的n个bit乘法结果。

36、可选的,在所述的存算一体存储器中,根据多项式系数最大位数的不同,单个存储单元储存一个或多个系数,由控制信号选择后进行计算并输出;多出的存储单元作为暂存空间,存储整个计算的中间结果。

37、可选的,在所述的存算一体存储器中,基于密文存储阵列的整个同态计算包括:

38、所述控制器发送控制信号以进行以下操作:

39、选择存储阵列内部数据;

40、选择存储阵列内部计算方式;以及

41、提供累加器和求模器的控制信号。

42、可选的,在所述的存算一体存储器中,在同态加法/减法时,存储阵列每次直接输出n个bit的密文或中间结果,在累加器中加/减并与之前暂存的中间结果在其中移位相加,由于系数位数较多,整个过程需要多个周期完成;

43、当结果中的一个系数的全部计算完成时,计算结果传输到求模器进行 [c]q操作,最后输出结果;

44、若还有后续计算则将其存入暂存空间中。

45、可选的,在所述的存算一体存储器中,在同态乘法时,存储阵列每次输出n个bit数据相乘的结果,在累加器中移位相加,由于系数位数较多,同时多项式乘法需要进行多次两个系数相乘的操作,整个过程需要多个周期完成;

46、当结果中一个系数的cx,cy,cz的非除法部分计算完成时,数据传输至求模器并进行计算,然后传输至暂存空间存储;

47、cx,cy,cz在累加器中,经过rlk的内积计算与最后的加法后得到乘法结果,若还有后续计算则将其存入暂存空间中。

48、本发明还提供一种使用存算一体存储器执行同态运算的方法,包括下列步骤:

49、接收第一输入数据c1;

50、接收第二输入数据c2,第一输入数据c1和第二多项式c2为密文,并且所述密文是经过基于多项式环空间的同态加密的密文;

51、将第一输入数据与第二输入数据的同态运算转换为加法运算和/或乘法运算和/或乘加运算;以及

52、使用存算一体存储器执行所述加法运算和/或乘法运算和/或乘加运算。

53、可选的,在所述的使用存算一体存储器执行同态运算的方法中,包括将密文写入存算一体存储器,暂存空间的第一输入数据和第二输入数据同时读取至第一输出端;

54、同次数项对应系数单次以存储阵列的存储位数相加后在累加器中进行后续不同权重的累加,每个系数长度是n倍,n为正整数;

55、在累加器对密文进行普通加法计算后,求模器对多项式进行[c]q操作,得到某一步的结果后寄存在暂存空间中等待后续操作调用,或是整个计算的最终结果后输出。

56、可选的,在所述的使用存算一体存储器执行同态运算的方法中,包括将密文写入存算一体存储器,暂存空间的第一输入数据和第二输入数据同时读取至第二输出端,以进行两个密文对应系数相乘;

57、相乘后,同次数项对应系数单次以存储阵列的乘法结果位数相加后在累加器中进行后续不同权重的累加,每个系数长度是n的倍数;

58、在累加器对密文进行累加计算后,求模器对多项式进行[c]q操作,得到某一步的结果后寄存在暂存空间中等待后续操作调用,或是整个计算的最终结果后输出;

59、对于乘法过程,第一次计算结果cx,cy,cz传回至暂存空间,等待rlk 还原操作调用,rlk内积结束后再次传回暂存空间,进行加法后得到乘法结果。

60、在本发明提供的存算一体存储器及其执行同态运算的方法中,由于采用存算一体执行同态运算,将存储资源中嵌入计算能力,减少了数据频繁移动带来的延迟和能耗方面的开销,因此相较于传统的架构,本发明的存内计算能够减少数据通信的消耗,对于处理数据量极大的同态运算,理论上能过显著减少功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181941.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表