具有写掩码的数据校验系统的制作方法

- 国知局

- 2024-07-31 19:14:06

本发明涉及芯片,尤其涉及一种具有写掩码的数据校验系统。

背景技术:

1、芯片中会包括多个不同的芯片内部存储器,例如静态随机存取存储器(sram)、锁存器阵列(latch array)等。当芯片内部存储器受到高能粒子冲击时,由于辐射干扰,所存储的数据可能存在误差,因此可以为芯片内部存储器设置误差校正码(error correctingcode,简称ecc),通过ecc码来校验数据准确性。每一芯片内部存储器具有对应的写数据位宽,但通常情况下,并非每次同时更新写数据位宽对应的全部数据,因此,通过写掩码(writemask)将不需要更改的数据遮盖,从而只更改需要更改的数据。

2、现有技术中,通常对芯片内部的存储器单独实现ecc保护机制,或者,单独实现写掩码,若需要对芯片内部的同一存储器同时实现ecc保护机制和写掩码,则需要使得ecc位数和写掩码位数严格对齐,否则,就会出现数据冲突。随着ecc位数的指数增加,对应的校验码位数是线性增加的。例如,某一芯片中,10%的操作对应的写掩码的位数为8位,而90%的操作对应的写掩码位数为32位,如果处理写掩码位数为32位的操作,若将ecc位数设置为32bit,每32bit数据对应7bit校验位,可以大大减少校验位的数目,且能保护90%的操作。若从保护完备性上来考虑,ecc保护要做8bit粒度,每8bit数据对应5bit校验位,会造成芯片面积浪费。因此对同一芯片中不同的芯片内部存储器设置对齐的ecc位数和写掩码位数,会造成芯片面积浪费,且无法实现较ecc位数更小粒度的数据校验,数据校验灵活性差。此外,若ecc位数和写掩码位数不对齐,还可以通过读取写掩码对应的位置当前在芯片内部存储的数据,然后再和当前待写入数据拼接,再生成ecc校验码,但需要消耗大量的时间,且增加了读取数据的次数,降低了芯片性能。

技术实现思路

1、本发明目的在于,提供一种具有写掩码的数据校验系统,提高了数据校验的灵活性,减少了芯片面积浪费,提升了芯片性能。

2、根据本发明第一方面,提供了一种具有写掩码的数据校验系统,包括设置在预设芯片中的n个芯片内部存储器{m1,m2,…,mn,…mn}、存储有计算机程序的存储器和处理器,其中,mn为预设芯片中的第n个内部存储器,n的取值范围为1到n;mn对应的ecc位数为an,ecc校验码的位数为gn,mn对应的写掩码位数为bn,mn对应的数据写入位宽为cn,mn对应的存储位宽为dn,cn≥an,cn≥bn,mn中包括一位校验标识位、gn位ecc校验码存储位和cn位写入数据存储位;当所述处理器执行所述计算机程序时,实现以下步骤:

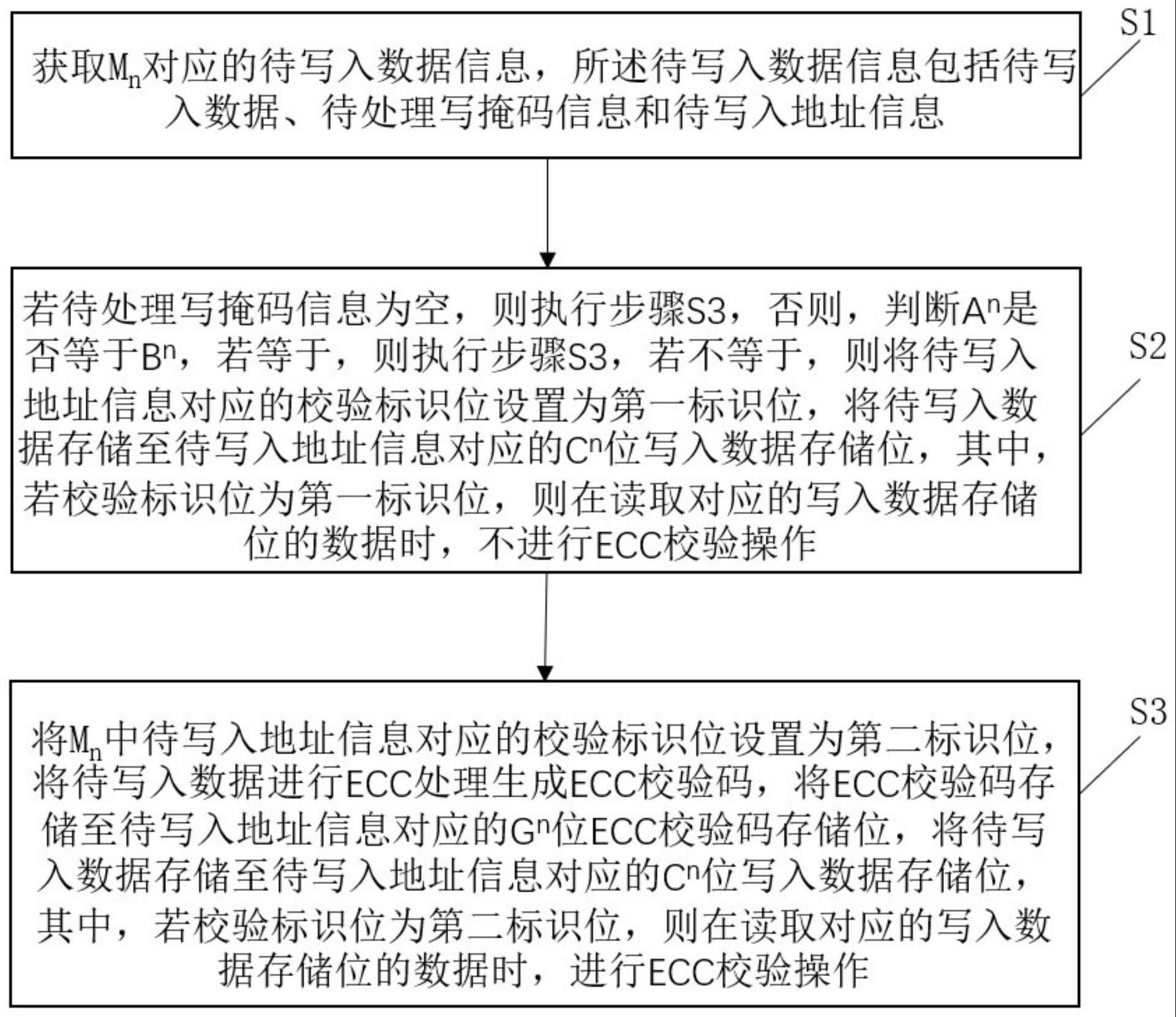

3、步骤s1、获取mn对应的待写入数据信息,所述待写入数据信息包括待写入数据、待处理写掩码信息和待写入地址信息;

4、步骤s2、若待处理写掩码信息为空,则执行步骤s3,否则,判断an是否等于bn,若等于,则执行步骤s3,若不等于,则将待写入地址信息对应的校验标识位设置为第一标识位,将待写入数据存储至待写入地址信息对应的cn位写入数据存储位,其中,若校验标识位为第一标识位,则在读取对应的写入数据存储位的数据时,不进行ecc校验操作;

5、步骤s3、将mn中待写入地址信息对应的校验标识位设置为第二标识位,将待写入数据进行ecc处理生成ecc校验码,将ecc校验码存储至待写入地址信息对应的gn位ecc校验码存储位,将待写入数据存储至待写入地址信息对应的cn位写入数据存储位,其中,若校验标识位为第二标识位,则在读取对应的写入数据存储位的数据时,进行ecc校验操作。

6、本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种具有写掩码的数据校验系统可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有以下有益效果:

7、本发明所述系统能够灵活设置写掩码位数和ecc位数,兼顾了ecc位数设置的灵活性和芯片的面积,提高了数据校验的灵活性,减少了芯片面积浪费,提升了芯片性能。

技术特征:1.一种具有写掩码的数据校验系统,其特征在于,

2.根据权利要求1所述的系统,其特征在于,

3.根据权利要求1所述的系统,其特征在于,

4.根据权利要求1或3所述的系统,其特征在于,

5.根据权利要求1所述的系统,其特征在于,

6.根据权利要求1所述的系统,其特征在于,

7.根据权利要求6所述的系统,其特征在于,

8.根据权利要求7所述的系统,其特征在于,

技术总结本发明涉及芯片技术领域,尤其涉及一种具有写掩码的数据校验系统,包括设置在预设芯片中的N个芯片内部存储器{M<subgt;1</subgt;,M<subgt;2</subgt;,…,M<subgt;n</subgt;,…M<subgt;N</subgt;}、存储有计算机程序的存储器和处理器,其中,M<subgt;n</subgt;为预设芯片中的第n个内部存储器;M<subgt;n</subgt;对应的ECC位数为A<supgt;n</supgt;,ECC校验码的位数为G<supgt;n</supgt;,M<subgt;n</subgt;对应的写掩码位数为B<supgt;n</supgt;,M<subgt;n</subgt;对应的数据写入位宽为C<supgt;n</supgt;,M<subgt;n</subgt;对应的存储位宽为D<supgt;n</supgt;,C<supgt;n</supgt;≥A<supgt;n</supgt;,C<supgt;n</supgt;≥B<supgt;n</supgt;,M<subgt;n</subgt;中包括一位校验标识位、G<supgt;n</supgt;位ECC校验码存储位和C<supgt;n</supgt;位写入数据存储位。本发明提高了数据校验的灵活性,减少了芯片面积浪费,提升了芯片性能。技术研发人员:周健受保护的技术使用者:沐曦集成电路(上海)有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181971.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。