具有存内布尔逻辑运算功能的存储电路及其模块、芯片

- 国知局

- 2024-07-31 19:12:46

本发明涉及集成电路设计领域中的一种存储电路,尤其涉及一种具有存内布尔逻辑运算功能的存储电路、将所述存储电路集成为模块使用的存储电路模块、将所述存储电路封装成为芯片使用的存储电路芯片。

背景技术:

1、现阶段人工智能(artificial intelligence,ai)的应用范围逐渐扩大到各个领域,如自动驾驶、可穿戴设备等。在传统冯·诺依曼架构体系中,当加速器在处理ai底层运算时,大量数据会往返于运算模块和存储模块之间,带来了数据传输的延迟和较大的能量消耗,为了有效解决上述问题,存内计算架构(compute in memory,cim)被提出。存内计算架构就是将运算电路内嵌到存储电路中,所以是存储电路中的计算电路结构,称之为存内计算架构。存内计算架构的存在,使得存储电路在实现基本的读、写、保持功能的同时,也可以实现计算功能。

2、以双6t-sram的存储电路为例,双6t-sram是指存储电路的两个存储单元都采用了6个晶体管。两个存储单元受控于位线bl、位线blb和不同的字线wl,分别形成具有相应的输出节点q、qb。现有的6t-sram相应实现布尔逻辑运算时,一般需要将参考电压接入灵敏放大器sa,或使用adc模数转换电路,因此需要嵌入的运算电路(即存内计算架构)的晶体管多达16t。这样会造成整个存储电路不但在读、写、保持功能这写基本操作时,能耗偏高、面积开销大,而在进行乘累加运算时,也会有相同的问题。

技术实现思路

1、基于此,为了解决现有的存储电路在应用于布尔逻辑运算功能时存在能耗偏高、面积开销大的技术问题,本发明提供一种具有存内布尔逻辑运算功能的存储电路、将所述存储电路集成为模块使用的存储电路模块、将所述存储电路封装成为芯片使用的存储电路芯片。

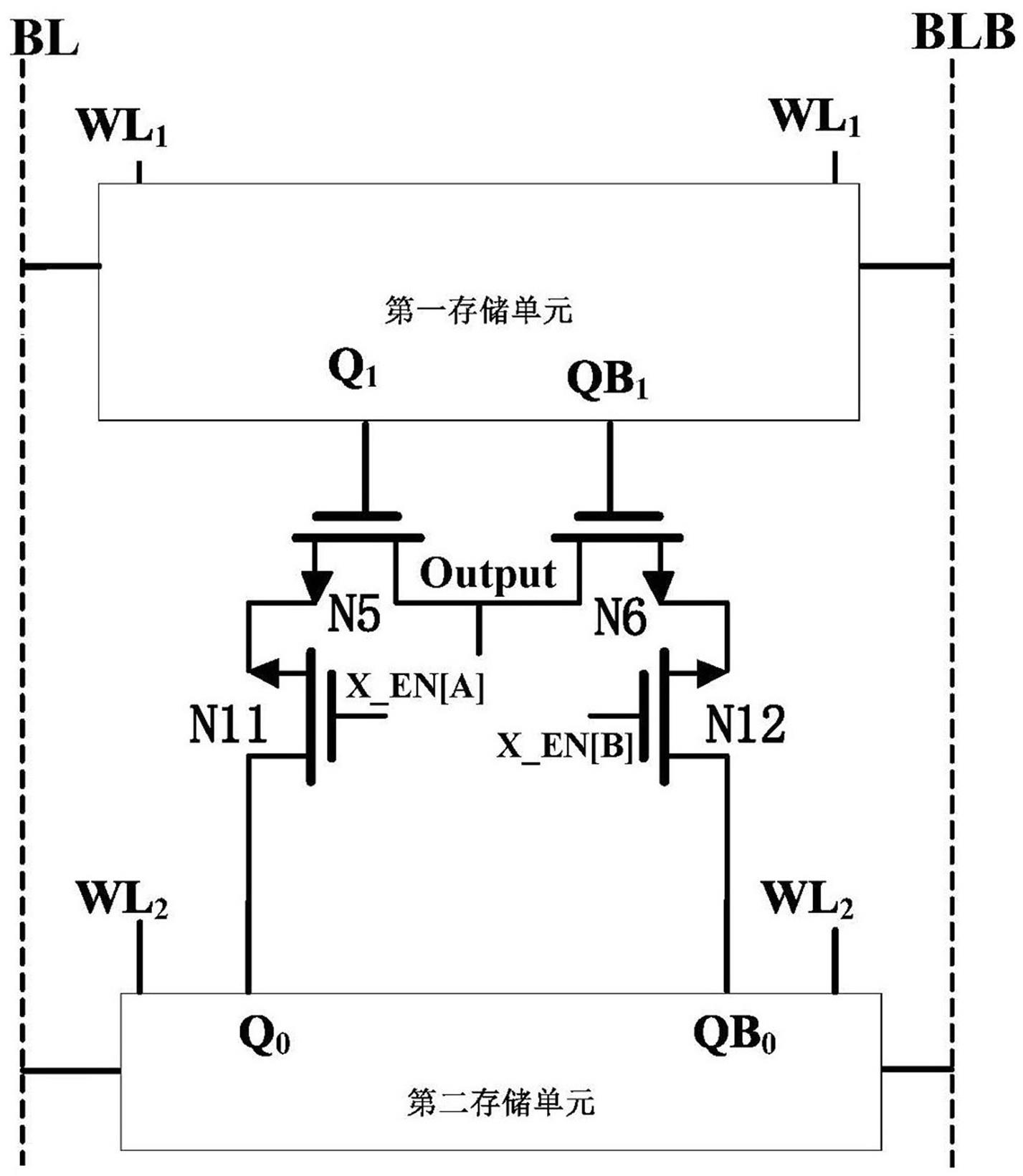

2、本发明的目的是通过以下技术方案实现的:一种具有存内布尔逻辑运算功能的存储电路,所述存储电路包括:

3、第一存储单元,其具有一对高低电平相反的存储节点q1、qb1;

4、第二存储单元,其具有一对高低电平相反的存储节点q0、qb0;

5、运算电路,其用于实现所述存储电路的存内布尔逻辑运算功能;

6、其中,所述运算电路包括nmos晶体管n5、n6、n11、n12;n5的栅极电连q1,且作为所述运算电路的其中一个运算输入节点;n5的源极电连n11的源极,n5的漏极电连n6的漏极并形成所述运算电路的运算输出节点output;n6的栅极电连qb1;n6的源极电连n12的源极;n11的漏极电连q0,且作为所述运算电路的其中另一个运算输入节点;n12的漏极电连qb0,n11、n12的栅极分别受控于使能信号x_en[a]、x_en[b]。

7、作为上述方案的进一步改进,在每次进行与运算前,重置运算输出节点output为低电平。

8、作为上述方案的进一步改进,所述第一存储单元由一对交叉耦合的反相器和两个传输管构成。

9、进一步地,所述第一存储单元包括pmos晶体管p1、p2和nmos晶体管n1~n4;n1、n2的栅极均电连字线wl1,n1的源极电连位线bl,n1的漏极电连q1;n2的源极电连位线blb,n2的漏极电连qb1;p1、p2的源极均电连电压源vdd,p1、n3的栅极电连qb1,p1、n3的漏极电连q1;p2、n4的栅极电连q1,p2、n4的漏极电连qb1;n3、n4的源极均电连电压源vss。

10、优选地,所述第二存储单元由一对交叉耦合的反相器和两个传输管构成。

11、再优选地,所述第二存储单元包括pmos晶体管p3、p4和nmos晶体管n7~n10;n7、n8的栅极均电连字线wl0,n7的源极电连位线bl,n7的漏极电连q0;n8的源极电连位线blb,n8的漏极电连qb0;p3、p4的源极均电连电压源vdd,p3、n9的栅极电连qb0,p3、n9的漏极电连q0;p4、n10的栅极电连q0,p4、n10的漏极电连qb0;n9、n10的源极均电连电压源vss。

12、作为上述方案的进一步改进,设存储节点q1和qb1的存储内容分别为a和,设存储节点q0和qb0的存储内容分别为b和,在使能信号x_en[a]、x_en[b]都为高电平的状态下,则运算输出节点output的同或逻辑运算表达式为ab + ;在第二存储单元的存储节点的路径上加n11、n12作为使能控制管,进而控制同或运算的开启/关闭。

13、作为上述方案的进一步改进,将同或使能信号中的x_en[a]置为高电平,x_en[b]节点置为低电平,此刻产生的逻辑关系为与。

14、本发明还提供一种存储电路模块,其采用上述具有存内布尔逻辑运算功能的存储电路集成,所述存储电路模块至少具有以下接线端:

15、电连所述第一存储单元的第一接线端,用于接入字线wl1;

16、电连所述第二存储单元的第二接线端,用于接入字线wl0;

17、电连所述第一存储单元的第三接线端,用于接入位线bl;

18、电连所述第二存储单元的第四接线端,用于接入位线blb;

19、电连n11的栅极的第五接线端,用于接入使能信号x_en[a];

20、电连n12的栅极的第六接线端,用于接入使能信号x_en[b];

21、电连运算输出节点output的第七接线端,用于输出所述存储电路模块的运算输出;

22、电连p1、p2的源极的第八接线端,用于接入电压源vdd;

23、电连n3、n4的源极的第九接线端,用于接入电压源vss。

24、本发明还提供一种存储电路芯片,其采用具有存内布尔逻辑运算功能的存储电路封装而成,所述存储电路芯片至少具有以下引脚:

25、电连所述第一存储单元的第一引脚,用于接入字线wl1;

26、电连所述第二存储单元的第二引脚,用于接入字线wl0;

27、电连所述第一存储单元的第三引脚,用于接入位线bl;

28、电连所述第二存储单元的第四引脚,用于接入位线blb;

29、电连n11的栅极的第五引脚,用于接入使能信号x_en[a];

30、电连n12的栅极的第六引脚,用于接入使能信号x_en[b];

31、电连运算输出节点output的第七引脚,用于输出所述存储电路模块的运算输出;

32、电连p1、p2的源极的第八引脚,用于接入电压源vdd;

33、电连n3、n4的源极的第九引脚,用于接入电压源vss。

34、与现有技术相比,本发明的电路结构通过控制运算电路的开启实现对两个存储单元的存储做逻辑运算,通过利用原有的两个存储单元设计分离控制的一组信号接口,实现同一个电路结构可以输出两种不同的逻辑信号,从而能耗低、运算灵活,解决现有的存储电路在应用于布尔逻辑运算功能时存在能耗偏高、面积开销大的技术问题。

35、同时本发明为了拓展运算类型和覆盖运算的数据粒度,整个存储电路的架构具有两种不同的计算模式。可以通过组合不同模块执行不同类型的运算,进而实现更多复杂数据运算,同时降低存储电路运行功耗,使运算效率大大提高。

36、而且本发明利用四个晶体管控制,实现了同列相邻两个数据的同或运算、与运算,并将权重放置在晶体管栅极,使用解耦的方式来运算同或结果,保证了权重的不受干扰。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181876.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表